基于VHDL的直接数字频率合成器的模块化设计及实现

2021-10-22包本刚邓长吉梁晓琳

包本刚 邓长吉 梁晓琳

基于VHDL的直接数字频率合成器的模块化设计及实现

包本刚1邓长吉2梁晓琳1

(1.湖南科技学院 智能制造学院,湖南 永州 425199;2.祁阳县肖家镇中学,湖南 祁阳 426131)

直接数字频率合成器(Direct Digital Frequency Synthesizer,DDFS)是一种全数字频率合成器件。本文介绍DDFS的工作原理及技术方案的VHDL实现,给出了基于Altera公司的FLEX 10K系列FPGA芯片完成DDFS系统的具体设计方案及实现方法。各个模块电路均采用硬件描述语言(VHDL)进行描述,给出了模块设计方案和仿真图。仿真结果表明:该设计波形仿真良好,具有很好的应用价值,且可移植性强,可应用于各种数字系统。

DDFS;FPGA;VHDL;数字调制;可移植性

频率合成器在电子对抗、数字通信系具有广泛的应用[1]。高性能的DDFS芯片不断推出,如Qualcomm推出的Q2368,美国AD公司推出的AD9853等产品[2]。但是专用DDFS芯片控制方式固定,并不适合所有用户的需求,而利用FPGA可编程芯片来设计则可以根据用户需要方便地实现各种比较复杂的调相、调幅和调频功能,具有良好的实用价值和可移植性[3]。采用VHDL语言强大的自顶向下的设计功能,可以非常方便地进行DDFS的模块化设计,并且具有很好的修改性和可移植性。本文提出一种基于FPGA和VHDL的DDFS设计方案,FPGA部分主要包括频率字模块、相位字模块、相位累加器模块、相位调制器模块、ROM表模块、D/A控制器模块,只需控制ROM查找表经DAC连续输出,然后经低通滤波器便可得到所需的信号。

1 DDFS的工作原理

一个单频信号可表示为

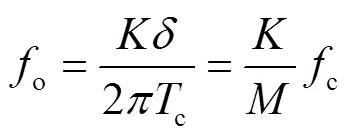

其中:fo为信号的输出频率,0为初始相位。对式(1)进行离散化处理,根据采样定理,fo为

其中:c为时钟频率;为δ的倍数,为π的分段倍率,和都是正整数,K的最大值小于M的1/2。

把式(2)和0=0代入式(1)中,式(1)初始相位为0的模拟信号为

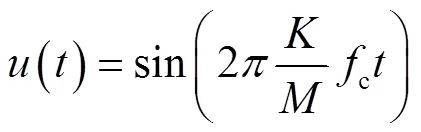

综上所述,当采样频率一定时,可以通过控制两次采样之间的相位增量来控制所得离散序列的频率,而这个相位增量不大于π,然后保持,滤波之后可唯一地恢复出此频率的模拟信号[3-5]。DDFS技术是一种把一系列数字形式的信号通过DAC转换成模拟信号的合成技术,一般是利用高速存储器做一个查找表,然后通过高速DAC输出以数字形式存入的波形[6]。基本的DDFS电路包括基准时钟、D/A转换器等。DDFS电路的基本原理框图如图1所示。

其中:为累加器的位数;为存储数字信号的位数;()为离散的波形输出函数;()为实际的波形输出函数;频率预置与调节电路中的不变量被称为相量增量,或者称为频率控制字。

当时钟脉冲每触发一次,相位累加器将频率控制字与相位寄存器输出的累加相位数据相加,把相加后的结果送至相位寄存器的输入端保存[3]。与此同时,相位寄存器会将在上一个时钟周期作用后所产生的新的相位数据反馈到加法器的输入端,在下一时钟到来时,加法器会不断地与频率控制字相加;并将这个值作为取样地址值送入波形存贮器中的波形查找表,波形查找表根据这个地址值输出相应的波形数据。波形数据会经DAC转换和低通滤波器将数字信号转换成所需要的模拟波形信号。相位累加器在基准时钟的作用下,进行线性相位累加,当相位累加器累加满量程时就会产生一次溢出,这样就完成了一个周期的波形输出,也就是DDFS合成信号的一个频率周期[7]。

2 基于FPGA的DDFS电路设计框图

本文完成一个频率和相位均可调节的具有余弦或正弦波形输出的DDFS,相位和频率值的预置与调节可以由键盘控制。DDFS设计总体框图如图2所示,累加器的字长为16 bit,波形存储器的地址长度为8 bit,波形存储器输出的幅值位数为8 bit,DAC选用常用的DAC0832,低通滤波器(LPF)采用压控电压源二阶低通滤波器,并且频率和相位值各由6 bit数码管显示。基准时钟取1MHz(主要是根据DAC的采样频率确定),c为1MHz,频率分辨率为1kHz,相位分辨率为0.36°[3,8-9,10]。

本文采用Altera 公司的QuartusⅡ10.0软件进行设计,采用VHDL编写。在DDFS设计中最基本的模块是波形存储器和相位累加器。为了实现相位调制的功能,在波形存储器前面加了一个相位调制器。整个基于FPGA的DDFS系统的程序是根据图2给出的DDFS设计总体框图进行设计。

图2 DDFS设计总体框图

3 基于FPGA和VHDL的DDFS模块电路设计及仿真

3.1 频率预置模块与频率调节电路

输出频率o=c/2。当=1时,电路输出最低频率为c/2N,而DDFS的最大输出频率由奈奎斯特定理决定,即fc/2,也就是说的最大值为2N−1。因此,只要足够大,DDFS可以得到足够细的频率间隔[10]。因此想要改变DDFS的输出频率,只要改变频率控制字即可。在本文中,相位的调节与频率的预置都是通过外部设备进行输入,并且采用了延时模块进行延时检测;因为外部设备输入的频率值与相位值是不能直接被检测到的,所以本文设计了按键输入模块来把输入的频率值与相位值转化成累加器需要的值和相位增量。把要显示的相位值和频率值以BCD码的形式进行存储,提供给数码管显示电路,便于进行译码和动态扫描。

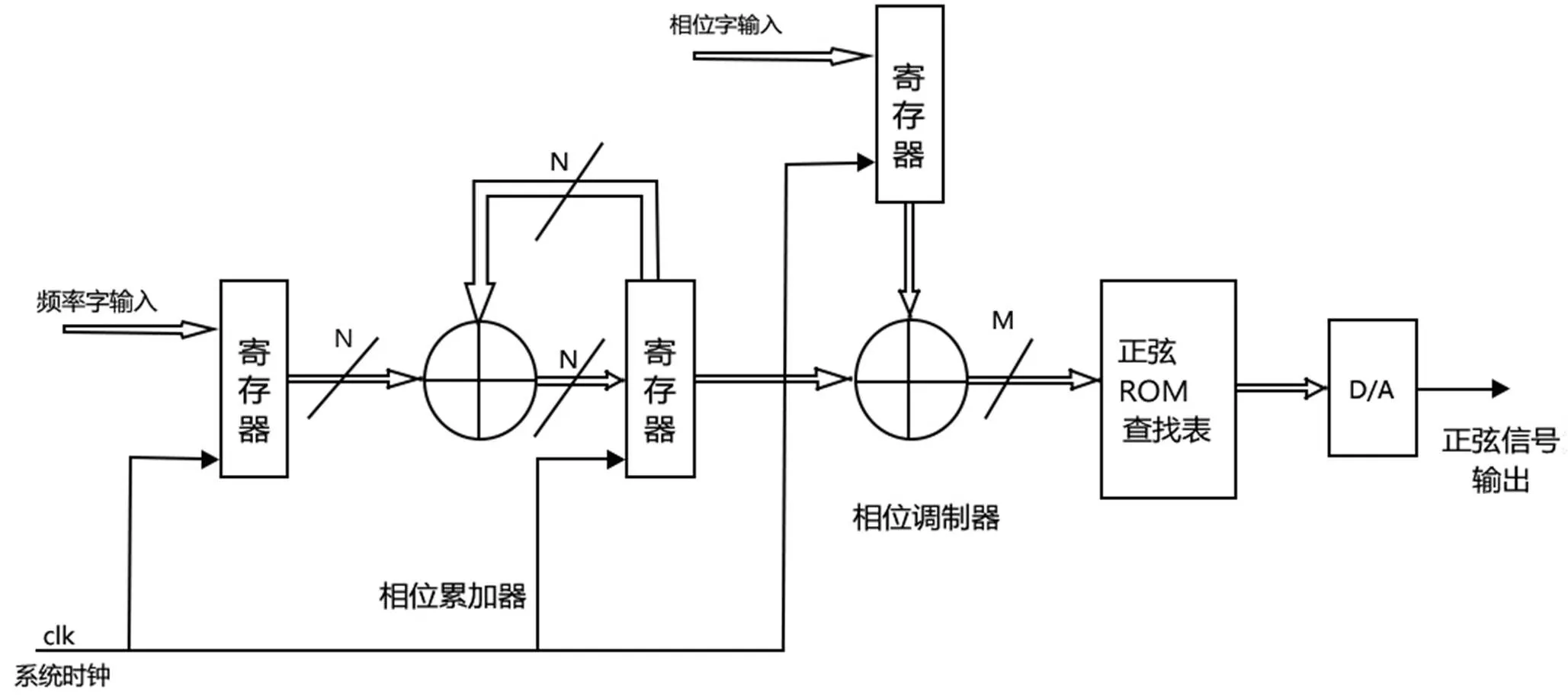

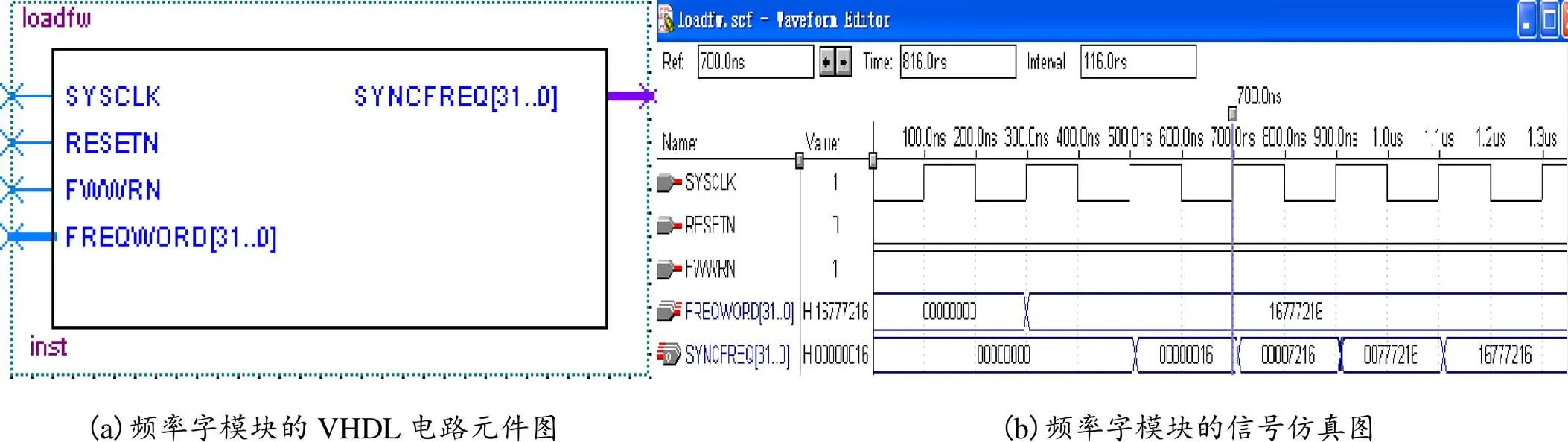

3.2 DDFS频率字模块与仿真

本模块为频率字输入模块,DDFS频率字模块的VHDL电路元件图和信号仿真图分别如图3(a)和(b)所示。输入“频率字”(图3(a)中的“FREQWORD[31..0]”)与输出“同步频率字”(图3(a)中的“SYNCFREQ[31..0]”)的字长=32。图3(a)中的“FWWRN”控制频率字写入,并把频率字加载到寄存器中,提供给相位累加器。

图3 频率字模块的VHDL电路元件图和信号仿真图

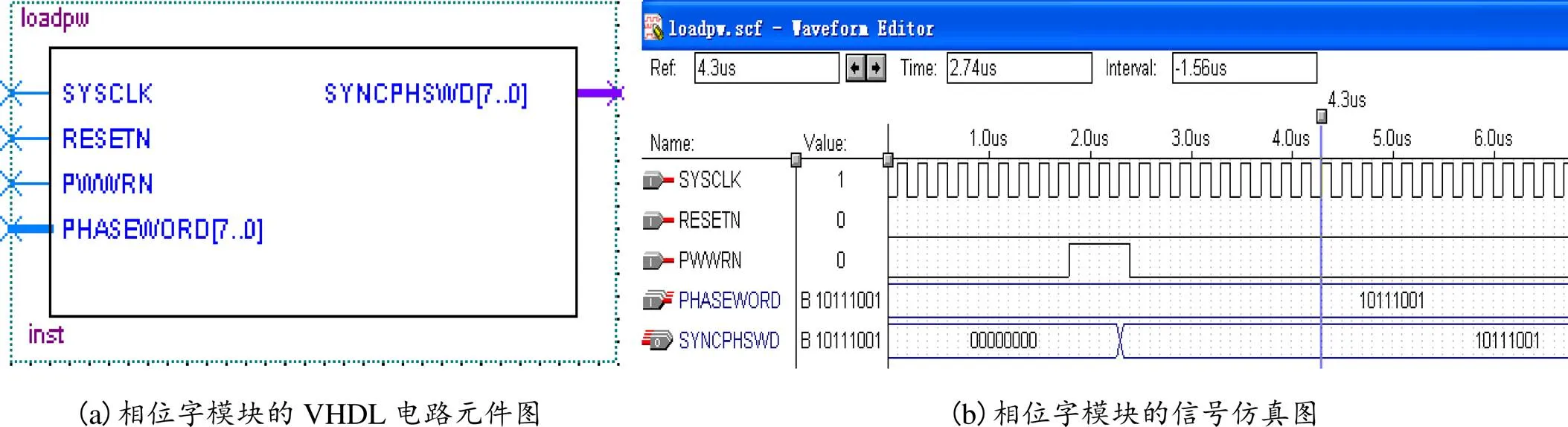

3.3 DDFS相位字模块与仿真

本模块为相位字模块。输入相位字与输出同步相位字的字长N=8。DDFS相位字模块的VHDL电路元件图和信号仿真图分别如图4(a)和(b)所示。图4(a)中的“PWWRN”来控制相位字写入,并把相位字加载到寄存器中,提供给相位调制器。

图4 相位字模块的VHDL电路元件图和信号仿真图

3.4 相位累加器模块与仿真

相位累加器为整个DDFS系统的核心。相位累加器模块的VHDL电路元件图和信号仿真图分别如图5(a)和(b)所示。输入为同步频率字,其字长=32,实现相位的累加功能。输出为8 bit量化相位值。

图5 相位累加器模块的VHDL电路元件图和信号仿真图

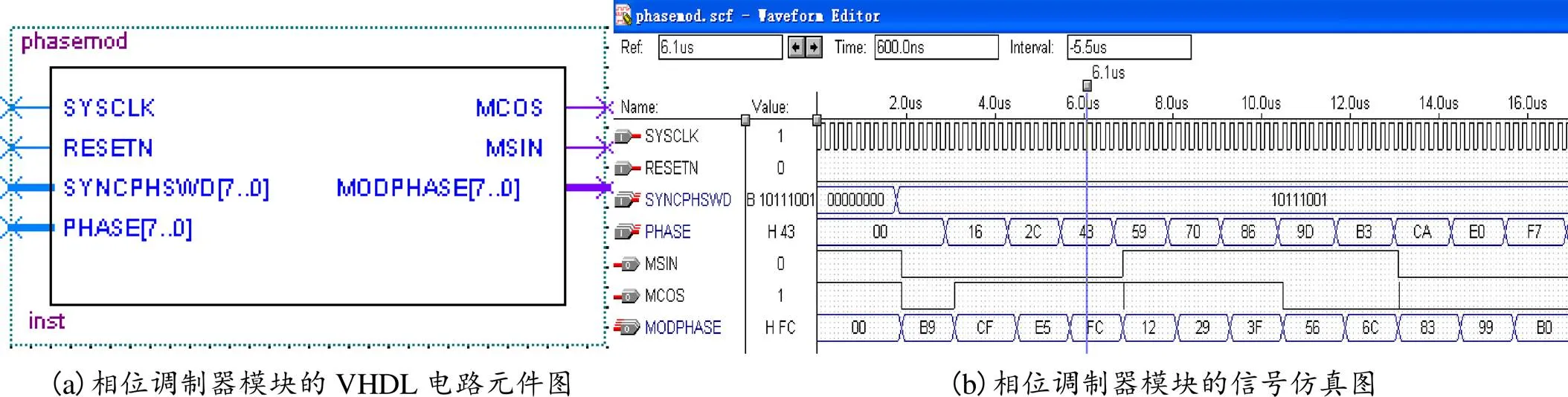

3.5 相位调制器模块与仿真

本模块为相位调制器模块。相位调制器模块的VHDL电路元件图和信号仿真图分别如图6(a)和(b)所示。输入为“同步相位字”(图6(a)中的“SYNCPHSWD[7..0]”)和8 bit量化“相位值”(图6(a)中的“PHASE[7..0]”)。输出为8 bit已调相位,实现对相位的数字调制功能。

图6 相位调制器模块的VHDL电路元件图和信号仿真图

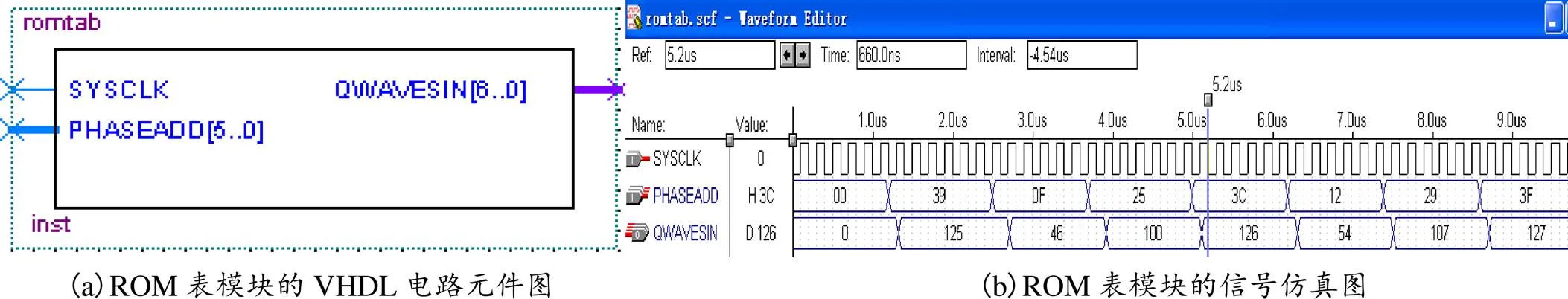

3.6 ROM表模块与仿真

ROM表模块的VHDL电路元件图和信号仿真图分别如图7(a)和(b)所示。假设ROM表中存放地址为0~63,数据为0~127。因此ROM的输入地址宽度为6 bit,相位调制器输出的数据通过逻辑运算便可以得到ROM表的地址;ROM表输出数据宽度为7 bit[11]。其表数据存放在ncosin.mif文件中。

图7 ROM表模块的VHDL电路元件图和信号仿真图

3.7 波形存储器模块与仿真

波形存储器模块,即正弦ROM查找表。这个模块需要把存储在相位累加器中的抽样值转换成正弦波幅度的数字量函数[12],可理解为相位到幅度的转换。波形存储器模块的VHDL电路元件图和信号仿真图分别如图8(a)和(b)所示。它的输入是“相位调制器”(图8(a)中“MODPHASE[7..0]”)中输出的高8 bit值,并将其作为正弦ROM查找表的地址码;查找表通过输入的地址相位信息得到相应的正弦波幅值信号;并通过“输出端口”(图8(a)中“NCOOUT[7..0]”)送往DAC,转化为模拟信号。

图8 波形存储器模块的VHDL电路元件图和信号仿真图

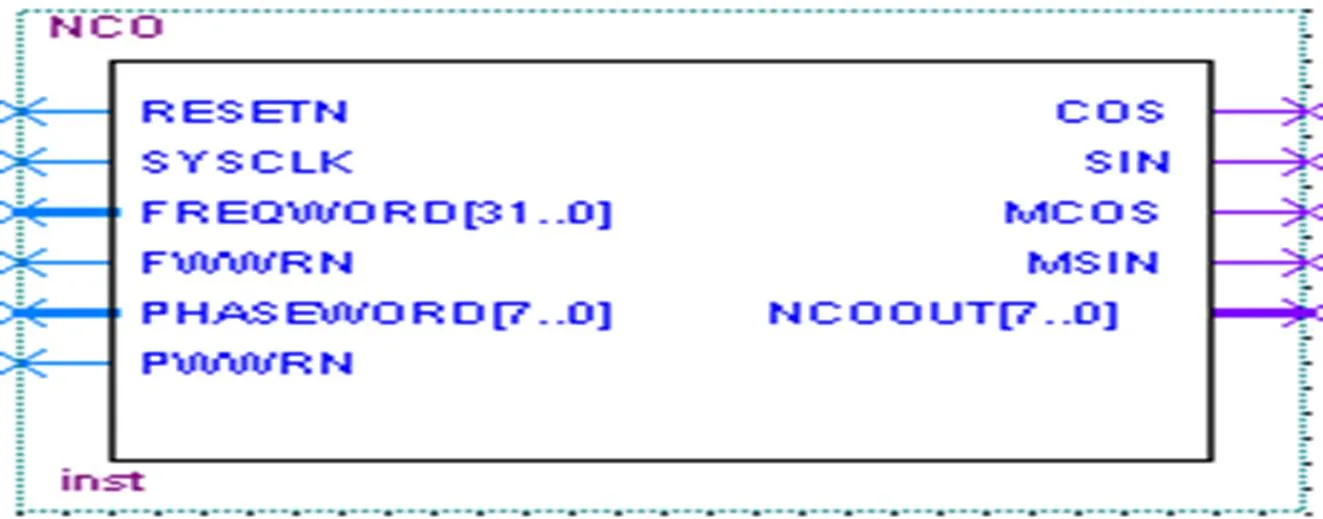

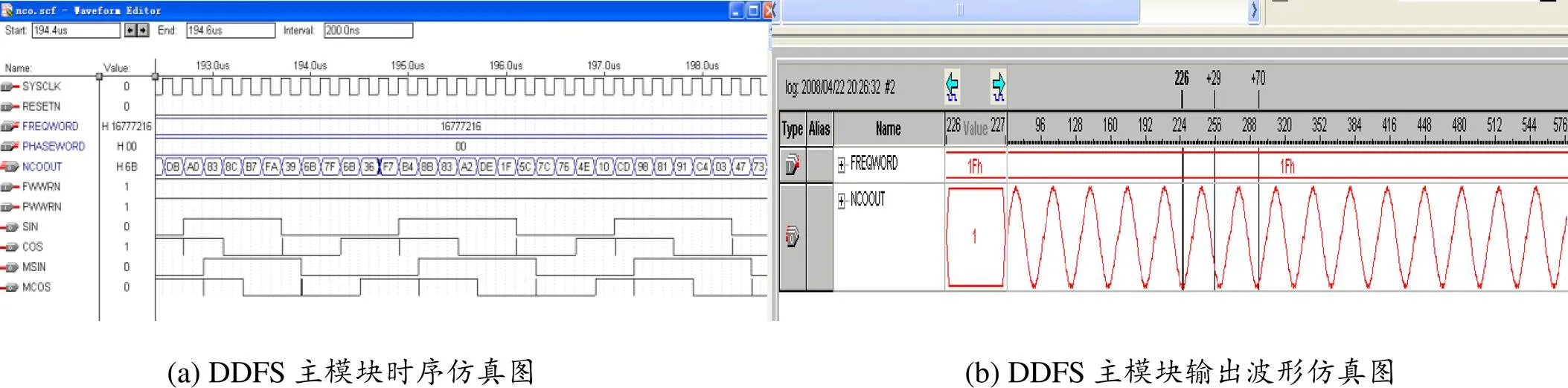

3.8 基于FPGA的DDFS的主模块的设计与仿真

本模块为DDFS的主模块,也是整个设计的顶层模块。DDFS信号源的底层模块采用VHDL语言进行设计描述,其顶层设计不但可以采用硬件电路图的形式进行描述,也可以采用VHDL描述。DDFS主模块的VHDL电路元件图如图9所示,DDFS主模块的时序仿真图和输出波形仿真图分别如图10(a)和(b)所示。图9中“NCOOUT[7..0]”为8 bit正弦波输出。图9中的“SYSCLK”为系统时钟信号输入,图9中的“RESETN”为系统复位信号,图9中的“FREQWORD[31..0]”为频率控制字输入,图9中的“FWWRN”为控制频率控制字写入脉冲输入,图9中的“PHASEWORD[7..0]”为相位控制字输入,图9中的“PWWRN”为控制相位控制字写入脉冲输入。图9中的“MCOS”“MSIN”是经相位调制器后的分别输出余弦信号和正弦信号的位置符号,图9中的“COS”“SIN”端口表示经相位累加器后分别输出余弦和正弦信号的位置符号。

图9 DDFS主模块的VHDL电路元件图

图10 DDFS主模块的时序仿真图和输出波形仿真图

4 结 语

本文采用规模大、功能强、处理速度快的FPGA芯片,利用VHDL自顶向下的设计方法设计了基于DDFS原理的数字频率合成器,实现了对波形频率、幅度、相位的连续可调。经测试,各项指标达到设计要求,实现了频率转换时间短、频谱纯度高、频率转换时相位连续。本文的成果可以应用于通信、电子及微波等领域。

[1]李永杰.高速直接数字频率合成器数字单元的设计与实现[D].成都:电子科技大学,2019.

[2]马文杰.基于DDS技术的程控信号发生器的研究[D].南京:南京林业大学,2009.

[3]苏健民,付金霞,刘嘉新.基于FPGA的直接数字频率合成器设计[J].自动化技术与应用,2006,25(8):29-31,40.

[4]祁艳杰,刘章发.基于Parallel_CORDIC的高精度高速度直接数字频率合成器的FPGA实现[J].电子学报,2014,42(7): 1392-1397.

[5]郑浩,饶远.直接数字频率合成器的FPGA设计与实现[J].计算机与网络,2012,38(22):66-68.

[6]李朋飞,王勇,黄秋兰.基于DDS的任意波信号发生器设计[J].现代电子技术,2012,35(17):72-74.

[7]常红霞,陈初侠,周平.基于FPGA的直接数字频率合成器的设计[J].皖西学院学报,2011,27(2):82-84.

[8]李智华,周峰,张帅.基于Multisim的直接数字频率合成器的设计与仿真[J].电力学报,2012,27(1):23-26.

[9]宋学良,郭裕顺.基于分段多项式的直接数字频率合成器设计[J].机电工程,2011,28(9):1113-1116.

[10]朱钰铧.基于FPGA的直接数字频率合成器的设计实现[J].安庆师范学院学报(自然科学版),2004,10(3):29-31,41.

[11]井新宇.基于CPU和FPGA/CPLD结构设计电子系统[J].电子工程师,2004,30(8):21-24,39.

[12]王磊.基于软件无线电的DS/FH混合扩频通信系统的研究[D].西安:西北工业大学,2003.

TN74

A

1673-2219(2021)03-0015-05

2021-04-09

湖南省普通高校教学改革项目(湘教通〔2018〕436号No.688);2020年度湖南省自然科学基金项目资助(项目编号2020JJ4322)。

包本刚(1976-),男,湖南永州人,硕士,副教授,研究方向为集成电子电路设计与测试。

(责任编校:宫彦军)