基于65-nm CMOS工艺的W波段两路电流合成型功率放大器的设计

2021-10-14黄占秋张旭赵晨曦康凯

黄占秋 张旭 赵晨曦 康凯

0 引言

近年来人们对高速率无线通信的需求日益提升,频率较低的频带范围(<10 GHz)被蓝牙、Wi-Fi、4G、5G通信等应用占据,频谱资源已经消耗殆尽,而频率较高的毫米波频带范围具有充足的频谱资源,因此具有广泛的应用前景[1-2].W波段电磁波由于在大气中的衰减较小,且对云、雾、雨的穿透特性好,因此在全天候雷达系统中有着良好的应用背景[3-4].在W波段的雷达系统中,功率放大器(Power Amplifier,PA)是一个十分关键的模块,其输出功率和效率直接决定了雷达系统的探测距离和功耗,因此设计高输出功率、高效率的功率放大器是一项十分必要的工作.通常W波段的功率放大器由基于Ⅲ-Ⅴ族的工艺实现,它具有高截止频率、高耐压的特性,因此能实现更高的增益和输出功率.但Ⅲ-Ⅴ族工艺不易与基于CMOS工艺的数字电路集成在一起,且生产成本高.CMOS工艺的优点是集成度高、成本低,而近年来它的工艺节点已经来到了深亚微米级,器件的最大振荡频率(fmax)超过200 GHz,因此非常适合毫米波相关应用,最近基于 CMOS 工艺的PA研究也越来越热门.2012年,Tsai等[5]基于65-nm CMOS工艺设计出了工作在W波段、带宽为27 GHz的PA,其饱和输出功率达到了14.8 dBm;同年,Gu等[6]采用65-nm CMOS工艺设计出了一款工作在101~107 GHz的功率放大器,饱和输出功率(Psat)为14.8 dBm,峰值功率附加效率(PAE)为9.4%;2018年,Vigilante等[7]采用28-nm CMOS工艺设计出了一款具有AM-PM失真补偿效果的超宽带PA,其小信号3-dB 带宽达到了29~57 GHz,通过调节补偿偏压,可以将工作频带内的AM-PM失真控制在1°以内,实现了很高的线性度;2019年,El-Aassar等[8]采用45-nm CMOS工艺设计了一款3-dB带宽为DC到108 GHz的超宽带分布式PA,采用堆叠式结构将PA的供电电压提升到6.6 V,最终实现了20.8 dBm的线性输出功率.

为了实现高输出功率、高带宽以及高效率,本文采用65-nm CMOS工艺设计了一款工作在W波段的功率放大器,通过三级级联以提升PA的整体增益,采用两路功率合成来提升输出功率,所有匹配网络均采用变压器结构实现,以此来增大带宽及减小版图面积.仿真结果显示所设计PA的3-dB带宽达到了20 GHz(84~104 GHz),小信号增益12.7~15.7 dB,饱和输出功率14.6 dBm,峰值功率附加效率(PAE)为9.7%,电路核心面积仅为0.115 mm2.

1 有源电路设计

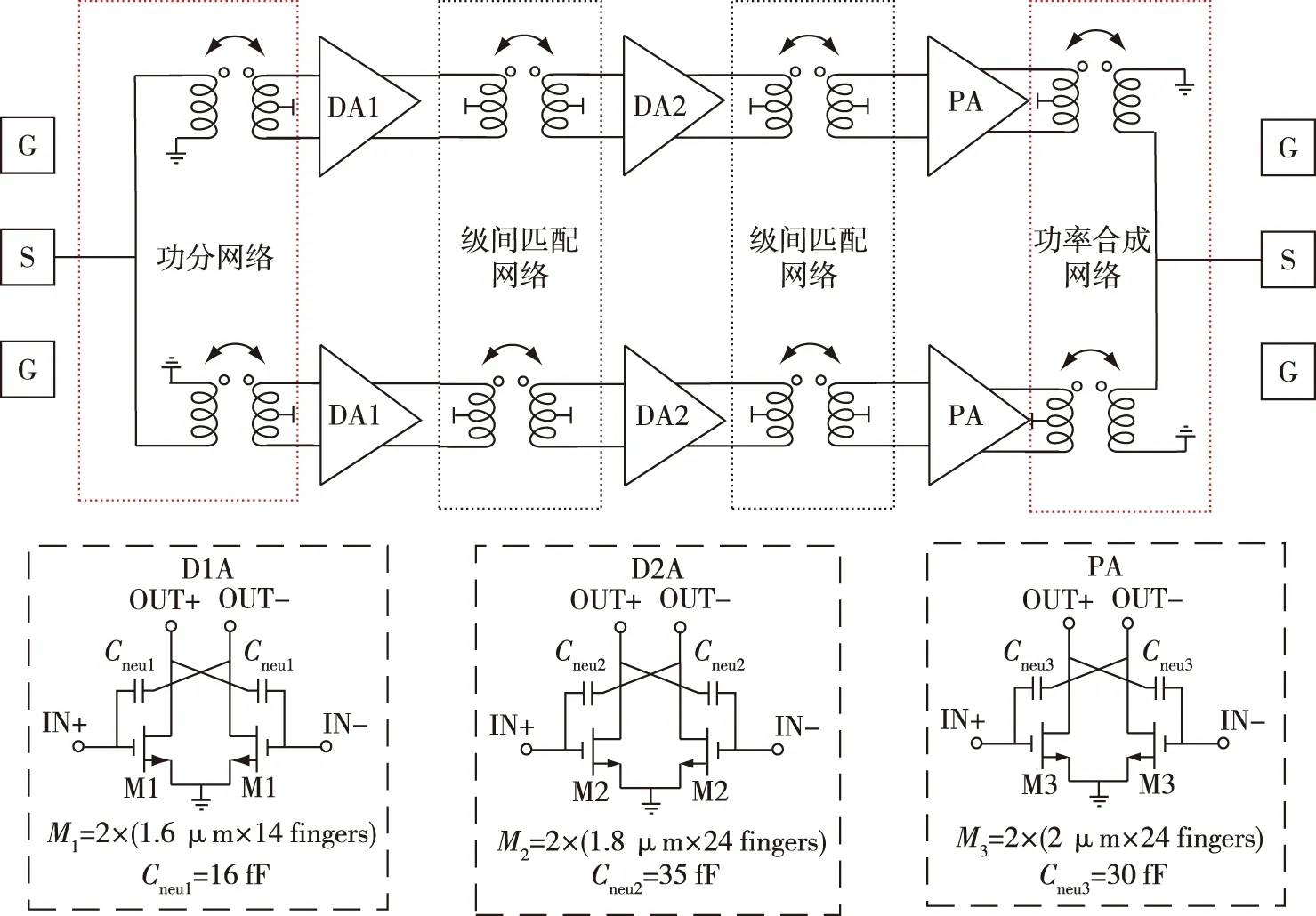

PA整体结构如图1所示,采用了两路差分功率合成的架构,通过三级基于中和电容的共源结构级联以实现高增益和稳定性.级间匹配网络和输入、输出匹配网络均采用变压器实现,大幅减小版图面积.

图1 功率放大器原理图Fig.1 Schematic of the proposed PA

共源级是PA常用的一种电路结构,其优点是输出端回波损耗会比较小,S22一般能做到-10 dB以下.然而由于CMOS工艺不提供背孔,因此其接地特性不好,而差分结构天然具有“虚地”特性,可以屏蔽掉芯片外围bonding线对电路性能的影响,因此CMOS功率放大器多用差分结构实现[9].图1显示所设计的PA有源电路采用差分共源结构.差分结构除了具有接地特性良好的优点外,还能将单端负载上的电压摆幅扩大为原来的两倍,从而提升输出功率[10].MOS管的栅漏寄生电容CGD的存在会引入一个负反馈路径,降低信号从栅极到漏极的增益及隔离度,从而引起稳定性问题.Cneu为中和电容,将其交叉并接在差分MOS管的栅、漏极之间可以补偿CGD产生的负反馈效应,从而提升共源结构的增益和稳定性[11].

图2为加入中和电容之后差分对的最大可用增益(Max Gain)和稳定性随电容值的变化曲线,它显示了适当容值的中和电容可以显著提升放大器的增益和稳定性,但若容值超过此区间,反而会降低稳定性.为了应对工艺、电压和温度的波动,电容容值的选取应留有足够的裕度,因此对于图2中的情况,容值选择为35 fF是一个比较好的选择,在此容值上下波动10%时放大器依然是无条件稳定的.

图2 中和电容对电路增益和稳定性的影响Fig.2 Influence of capacitance neutralization on max gain and stability

为了获得较高的输出功率,功放级单个MOS管的总栅宽选择为96 μm,而为了减小大尺寸晶体管的寄生带来的增益恶化,往往需要将其划分为多个小尺寸晶体管的并联[12],因此这里将单个96 μm的MOS管替换为2个总栅宽为48 μm的MOS管并联,单指栅宽选择为2 μm,指数为24,以此来获得单个MOS管的最佳性能.第2驱动级MOS管选择2个管子并联,每个管子有24 fingers,其单指栅宽为1.8 μm,总栅宽为2×1.8×24=86.4 μm.第1驱动级由于不需要提供高输出功率,故选择2个管子并联,每个管子有14 fingers,其单指栅宽为1.6 μm,总栅宽为2×1.6×14=44.8 μm,在节省功耗的同时提高增益.

2 无源电路设计

2.1 基于变压器的级间匹配网络的设计

由于硅基工艺往往提供多层金属,例如65-nm CMOS工艺提供了M1~M9共9层金属用于走线,这为变压器的使用提供了便利.图3为采用M8和M9两层金属设计的一种变压器,这两层为顶层金属,具有最大的厚度和最低的电阻率,因此无源损耗较低.两层金属各自绕成一圈电感,在空间上呈垂直堆叠的状态,因此二者具有一定的电磁耦合,形成了具有一定耦合系数的变压器结构,初级线圈的能量可以通过电磁耦合传递到次级线圈.对于差分电路来说,变压器可以同时用来实现阻抗匹配和直流供电的作用[13].线圈中心抽头处是天然的虚地点,直流电压从该点馈入,不会影响变压器的性能.作为级间匹配网络使用时,初、次级线圈各自的两个端口分别与前级的差分输出端口和后级的差分输入端口相连,在阻隔直流信号的同时可以实现级间的阻抗匹配.变压器的两种简化的等效电路也显示在了图3中,L1、L2、M分别为初、次级线圈的电感量和互感量,M与耦合系数k的关系为

图3 变压器3D模型及其两种等效电路Fig.3 The 3D model of the transformer and its equivalent circuits

(1)

线圈的感量可以通过其尺寸大小进行相应调整,耦合系数则由初、次级线圈的空间相对位置决定.通过选取合适变压器结构和尺寸,可以得到所需的电感值和耦合系数,从而实现阻抗变换,达到阻抗匹配的效果.此外,由于变压器本身可以看作分布参数电路,初、次级线圈之间以及线圈与地之间都存在寄生电容,这些电容与线圈本身的电感形成一些高阶的LC谐振腔,因此可以实现较高的匹配带宽.

2.2 基于变压器的功率分配、功率合成网络的设计

由于输入输出信号都是单端信号,因此在输入和输出端口均需要巴伦进行信号的单-差分转换,将变压器次级线圈的一端接地即可实现巴伦的作用.以输入匹配网络为例,单端信号馈入输入PAD后,经传输线直接分为两路同相位的单端信号,即实现了功率分配的作用.由于功分后的两路信号是同相位的,不存在隔离度的问题,因此不需要采用威尔金森功分器结构进行功率分配.单端信号经过巴伦转换成差分信号后被MOS管放大,最后经结构相同的功率合成网络合成一路单端信号后传输到输出PAD上.

图4显示了功率放大器的输出端功率合成网络的3D模型图及其等效电路.负载电阻为50 Ω,Csg为信号PAD的对地电容.末级一路PA需要的差分最佳负载阻抗Zopt为18.1+14jΩ,因此功率合成网络的作用是要将50 Ω的单端阻抗转换成末级PA所需要的差分最佳负载阻抗Zopt.变压器T1可以用其等效模型表示.A点为经过PAD看到的负载阻抗,B点为经过一段电感看到的阻抗,C点为功分后一路看到的阻抗,即为B点阻抗的两倍.D点为巴伦单端看到的阻抗,经变压器的阻抗变换后变为Zopt=18.1+14jΩ.阻抗变换的过程显示在图5所示的Smith圆图中.

图5 功率合成网络的阻抗变换过程Fig.5 Impedance transformation process of the power combiner

3 仿真结果

基于65-nm CMOS工艺实现了W波段的功率放大器,电路版图如图6所示.整体电路采用ANSYS HFSS进行3-D电磁仿真.电源电压采用1 V,末级PA的栅极偏压为0.7 V,驱动级的栅极偏压均为0.6 V,版图核心面积为230 μm×500 μm,总面积(包含PAD)为750 μm×560 μm,静态功耗为350 mW.

图6 功率放大器版图Fig.6 Layout of the PA

图7a给出了PA的S参数后仿结果,在1 V的供电电压下,实现了84~104 GHz的3-dB带宽,峰值增益为94.5 GHz处的15.7 dB.在90~100 GHz的频率范围内S11、S22均小于10 dB,实现了较好的匹配效果.图7b显示了PA在84、94和104 GHz处的大信号仿真结果,输出功率和效率均在94 GHz处达到了最大,Psat为14.6 dBm,OP 1-dB(输出1-dB压缩点)为11.3 dBm,峰值PAE为9.7%.

图7 1 V供电下的仿真结果Fig.7 Simulation results of the PA under 1 V supply

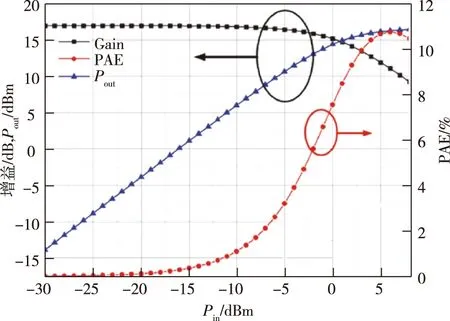

为了与其他文献中的测试条件保持一致,将供电电压加大到1.2 V进行了仿真,供电电压的提升会使得MOS管漏极电压摆幅增大,从而提升输出功率和效率.仿真结果显示在94.5 GHz处,输出功率和效率均有提升,输出1-dB压缩点上升到了12.7 dBm,Psat为16.3 dBm,对应的峰值PAE达到了10.7%.仿真结果如图8所示.与表1中其他文献对比,本文所设计的PA在输出功率、效率和芯片面积上都有一定的优势.

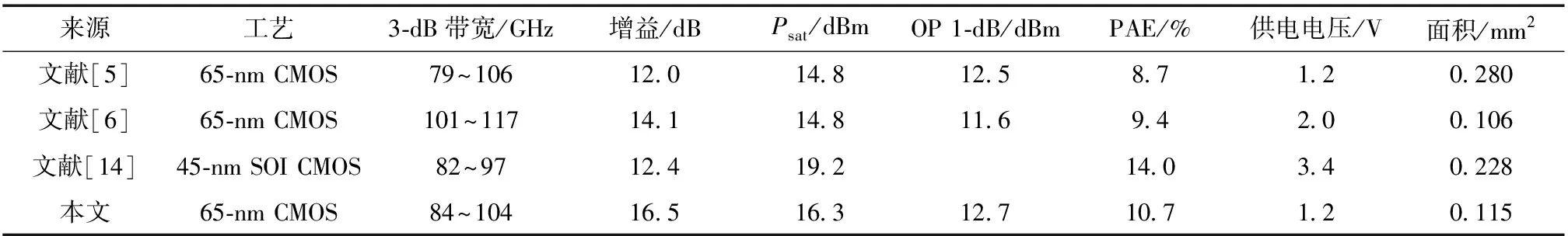

表1 电路性能比较

图8 1.2 V供电下的大信号性能Fig.8 Simulated large signal results under 1.2 V supply

4 结束语

本文基于变压器的阻抗匹配和功率合成的思想,采用65-nm CMOS工艺设计了一种高增益、高输出功率的功率放大器.仿试验结果表明该放大器在84~104 GHz的范围内实现了大于12.7 dB的小信号增益,最大饱和输出功率达到了14.6 dBm,对应的PAE为9.7%,在增益、带宽、输出功率和效率上都表现出了良好的性能.