一种适用于TSN 端系统的DMA 控制器的设计与仿真分析*

2021-10-03乔庐峰陈庆华王雷淘

杜 婧,乔庐峰,陈庆华,王雷淘

(陆军工程大学,江苏 南京 210001)

0 引言

时间敏感型网络(Time Sensitive Network,TSN)是目前国际上正在积极推动的全新网络技术。TSN允许周期性与非周期性数据在同一网络中传输,使得标准以太网具有确定性传输的优势[1]。典型TSN网络如图1 所示,该网络由TSN 端系统、物理传输链路和TSN 交换机组成。TSN 端系统是产生各类网络数据和对接收数据进行处理的终端设备。TSN网络中的时间敏感业务以全局高精度时间同步为基础,对端到端时延有确定性要求[2]。TSN 端系统可以根据网络配置对时间敏感业务按照确定的时延进行收发调度和处理[3],对于非时间敏感业务,可以根据业务类别提供差异化的收发调度和处理。当不同类别的业务在端系统中进行混合处理和传输时,端系统可以针对不同类别的业务流建立不同的逻辑队列,进行差异化处理。

图1 TSN 网络结构

TSN 网络把业务分成8 个基本类别[2],其中时间敏感业务流有音频流、视频流、网络控制流和内部网络控制流。除了时间敏感业务流之外还有最大努力流、卓越努力流、严苛应用流和基础数据流。时间敏感业务流在交换节点和端系统中收发处理优先级最高,其他业务流收发处理优先级 较低。

在TSN 端系统中,直接内存存取(Direct Memory Access,DMA)控制器通过处理器总线在网络接口和处理器内存之间进行高速数据收发。根据处理器总线技术体制的不同,DMA 控制器的设计有很大差异,赛灵思(Xilinx)的Zynq7000 系列现场可编程门阵列(Field Programmable Gate Array,FPGA)采用片上系统(System on Chip)架构设计,是实现TSN端系统较为理想的平台。Zynq7000 系列FPGA 提供了完整易用的开发环境[4],包括高效的DMA 控制器内核,但是所提供的DMA 控制器采用单一的循环队列结构,无法对不同类型的业务在收发方向上进行区分调度,无法满足对TSN 端系统的要求。本文设计了一种在收发方向上各支持8 个逻辑队列并支持缓冲区共享的DMA 控制器,在保持高效数据收发的同时可支持差异化的业务调度和处理。

1 端系统电路结构设计

本文所实现的端系统电路结构如图2 所示。端系统电路主要分为5 个部分,包括PL 端的接收控制电路、发送控制电路、DMA 控制器以及PS 端内存中的接收数据队列和缓冲区、发送数据队列和缓冲区。

系统初始化时,先需要在内存中设置多块固定大小的接收和发送缓冲区,针对每一块收发数据缓冲区建立数据描述符[1]。数据描述符中包括对应数据缓冲区的起始地址。在接收方向上,每个接收描述符对应的指针被写入接收自由指针队列,供DMA 控制器接收使用;在发送方向上,每个发送描述符对应的指针被写入发送自由指针队列,供 CPU 使用。

如图2 所示为接收数据的流程,具体如下文 所述。

图2 端系统电路结构

(1)接收MAC 控制器先判断到达数据帧是否为时间敏感数据帧,然后读取数据帧的流类型、字节数等字段,并标记数据帧的到达时间,生成指针存入接收接口队列的指针先入先出队列(First Input First Output)中等待DMA 控制器读取。

(2)数据帧存入接收FIFO 后,接收MAC 控制器发送信号给DMA 控制器,表示数据帧准备好被读取。

(3)DMA 控制器中的写内存控制电路检测到接收接口队列有完整数据帧时,从接收FIFO 中读取一个预先存储的自由指针和对应的接收描述符,从而获取接收数据帧在内存中的具体存储位置。然后将接收数据帧以突发方式通过总线接口高效写入内存,并根据接收数据帧的长度更新位于内存中的描述符信息,最后将该描述符的指针根据流类型写入相应的接收完成指针队列。

(4)CPU 检测到内存中相应接收指针队列非空后,读取完成队列指针及其指向的描述符,根据描述符提供的起始地址和有效长度,进行数据处理。由于存在多个接收完成指针队列,因此处理器可以对接收指针业务进行差异化处理。

图2 为发送数据的流程,具体流程如下文所述。

(1)CPU 先把准备好的数据帧存入内存,按照流类型把发送数据帧的完成指针存入对应的完成队列,等待DMA 读取,CPU 修改PL 端DMA 控制器内的完成指针队列状态寄存器,DMA 控制器获取到内存中的完成指针队列状态。。

(2)DMA 控制器中的读内存控制电路检测到相应队列中有待发送数据帧,优先读取高优先级完成指针队列。读内存控制电路通过总线读取内存中的完成指针及其对应的描述符,得到待发送数据帧的起始地址和有效长度。

(3)DMA 控制器以突发的方式从内存中读取待发送数据帧。DMA 控制器把待发送数据帧写入发送接口队列的发送数据FIFO 中并生成相应的指针,发送MAC 控制电路从FIFO 中读出数据帧后发出。内存中的FQ—PTR 为存放自由指针的队列,PQ0—PTR 到PQ7—PTR 为存放完成指针的 队列。

为了满足TSN 端系统对不同类型业务的差异化处理和调度需求,本文设计了一种支持多个逻辑队列且支持发送和接收缓冲区共享的多通道DMA 控制器。在接收方向上,接收管理电路将收到的混合业务流分类,DMA 控制器首先给每个数据帧分配1 个描述符,描述符中包含数据帧基本信息,并且DMA 控制器给不同类型的数据帧提供差异化服务,如DMA 控制器内部有8 个队列,分别对应8 个不同的流类型,其中优先级最高的是时间敏感型数据帧。DMA 控制器把不同类型的数据帧存入内存后,把其对应的完成指针存入完成指针队列[5],CPU 根据需要从完成队列中读取指针,再根据指针指向的内存块读取数据。时间敏感数据帧和非时间敏感数据帧在DMA 控制器内部独立排队,保证时间敏感数据帧能够被处理。在发送方向上,CPU 准备好待发送的数据帧,时间敏感型和非时间敏感型待发送数据帧在内存中独立排队,内存中也有8 个完成指针队列。DMA 控制器优先从内存中读取高优先级队列的完成指针,传送给下级电路,保证时间敏感数据帧能优先发送。在内存和DMA 控制器中,根据流类型把完成指针存放在不同的完成队列,在接收方向或者发送方向上,不同业务流的描述符和内存块是共享的[5],满足混合业务流的传输需求的同时提高了资源利用率。

多通道DMA 控制器可以完成包括时间敏感型数据流在内8 个混合业务流的收发操作,接收缓冲区和发送缓冲区被8 类业务共享,缓冲区中存储业务类别由缓冲区对应指针的队列决定,有效提高缓冲区利用率,降低CPU 负荷。

2 多队列DMA 控制器的数据结构设计

在TSN 端系统中,DMA 控制器[3]通过高级可扩展接口(Advanced eXtensible Interface,AXI)[2]在内存和本地缓冲区之间高速收发数据,其支持的队列结构如图3 所示。

图3 DMA 控制器内部结构

2.1 DMA 控制器接收数据处理流程

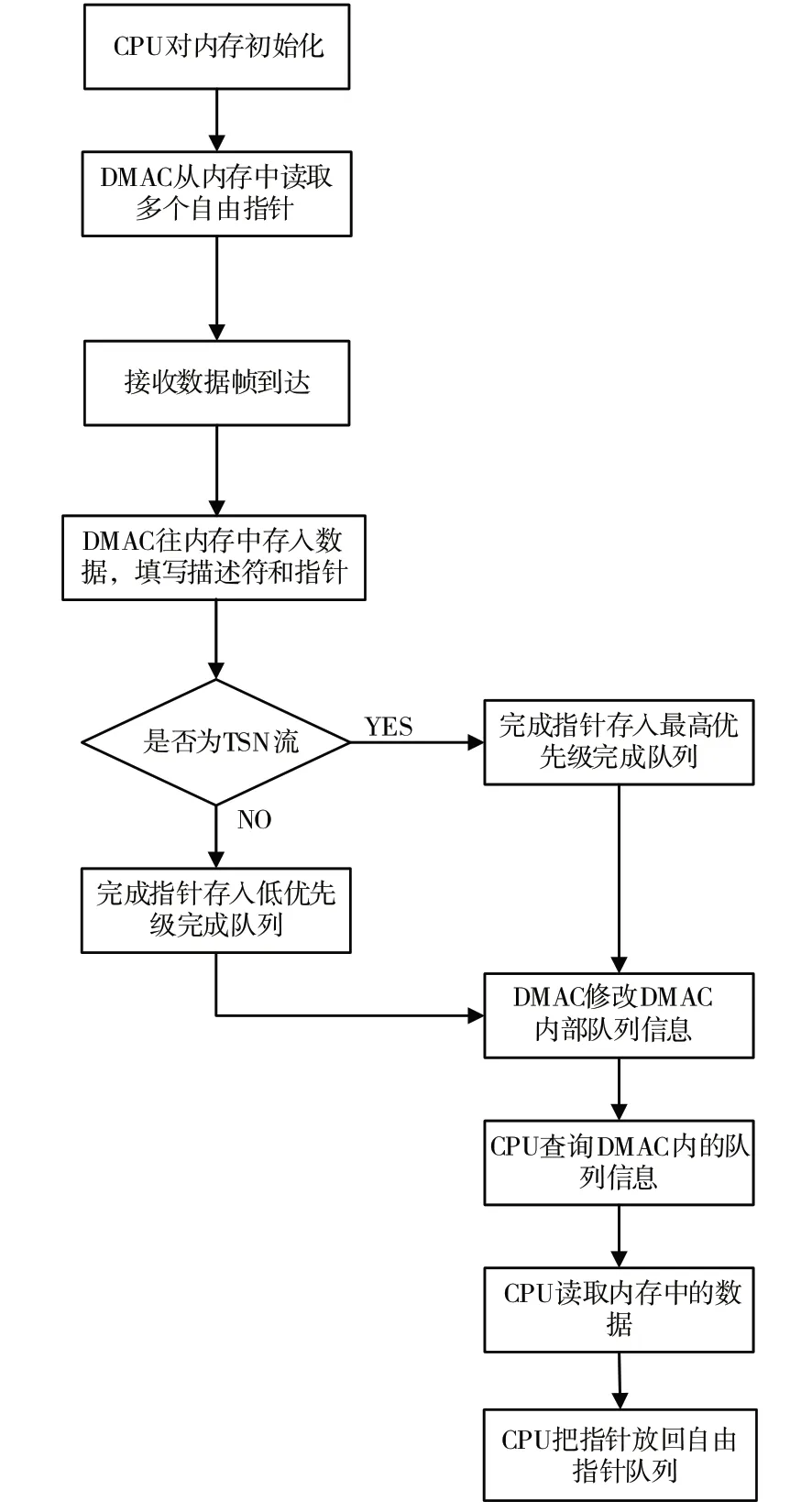

DMA 控制器数据接收处理流程如图6 所示,在接收方向上的处理流程具体如下文所述。

图6 接收数据流程

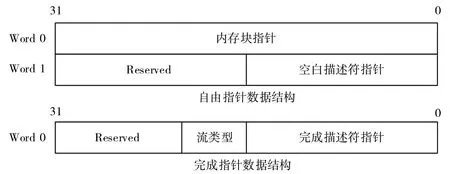

(1)在TSN 端系统接收数据之前,先需要进行初始化操作。CPU 在内存中设置数据缓冲区,把数据缓冲区分成固定大小的内存块,每个内存块对应1 个描述符,1 个描述符对应1 个指针。指针和描述符在CPU 和DMA 控制器之间通信,用来指示数据帧在内存中存放的位置和数据帧的基本信息。描述符数据结构如图4 所示,描述符中存放着对应内存块在内存中起始地址和有效位,以及对应数据帧的流类型、字节数和到达时间等。指针有自由指针和完成指针两种。自由指针和完成指针的数据结构如图5 所示,自由指针指向空白描述符和空白内存块在内存中的起始地址,自由指针存放在自由指针队列中。完成指针存放着完成描述符在内存中的起始地址和该完成指针对应数据帧的流类型。完成指针存放在完成队列中,根据数据帧的流类型,划分出8 个完成指针队列,其中时间敏感型数据帧优先级最高。自由指针队列和完成指针队列有首尾指针和读写指针,在内存中构成一个FIFO 队列。自由指针或完成指针队列首尾指针相同时,队列为空;首尾指针不同时,队列中存在可用的自由指针或完成指针。读指针指向当前队列中即将被读取的指针,写指针指向该队列即将被写入指针的地址。DMA控制器内部的队列状态寄存器存放着内存中自由指针队列和完成指针队列的首尾和读写指针。初始化结束时,内存中的自由指针队列为满,8 个完成指针队列为空,同时CPU 修改DMA 控制器内部的各指针队列的指针寄存器。

图4 描述符数据结构

图5 指针数据结构

(2)DMA 控制器从内存中读取多个自由指针存入DMA 控制器内部FIFO。接收控制电路准备好数据帧后,DMA 控制器先把数据写入自由指针指向的内存块,修改描述符,根据数据帧的流类型,把完成指针存入对应的完成指针队列,同时修改DMA 控制器中该队列的写指针,指向下一个完成指针的写入位置。

(3)CPU 查询DMA 控制器内部的8 个完成指针队列信息,判断各个完成指针队列中是否有待处理的数据帧。按照优先级顺序,先读取高优先级完成指针队列中的指针,然后读取相应的描述符,处理用户数据。

(4)数据处理完成后,CPU 将该指针写入接收自由指针队列,并同时修改内存和DMA 控制器中自由指针队列的写指针,使得接收缓冲区可以循环利用。

2.2 DMA 控制器发送数据处理流程

DMA 控制器数据发送处理流程如图7 所示,在发送方向的具体流程如下所述。

图7 发送数据流程

(1)发送数据前端系统也需要进行初始化操作,具体操作方式与接收数据状态初始化过程相似。CPU 在内存中设置数据缓冲区,给缓冲区分配描述符,给描述符建立指针,修改DMA 控制器内部队列状态寄存器。

(2)初始化结束后,在发送方向上,CPU 需要发送数据时,从发送自由指针队列读取一个自由指针,然后读出对应的描述符。CPU 将待发送数据写入描述符指向的缓冲区,然后根据业务类型把完成指针写入相应的待发送指针队列,修改该完成队列的写指针,同时修改DMA 控制器内部的相应完成指针队列的写指针。

(3)DMA 控制器查询8 个完成指针队列信息,检测到内存中某个完成指针队列有待发送的数据帧,准备发起对内存的读操作。DMA 控制器通过AXI 总线一次可以读取多个完成指针,并读取对应的描述符;根据描述符信息读取内存块中的数据帧,通过网络端口发出。

(4)DMA 控制器把已发送数据对应的指针以突发方式写入内存中的发送自由指针队列,修改内部发送自由指针队列的写指针寄存器,使发送数据缓冲区可以循环利用。

3 仿真分析

图8、图9 给出了DMA 控制器从内存中读取数据并进行发送的基本流程。仿真实验中,在发送方向上,配置了128 个大小为512 bits 的内存块,相应地,配置了128 个大小为128 bits 的描述符以及128 个对描述符对应的自由指针。此外,完成队列分成4 个子队列,每个完成指针为32 bits,每个子队列有32 个完成指针。

图8 自由指针队列的读取和写入

图9 数据发送过程中完成指针队列的写入和读出

发送数据时,发送过程对自由队列的读取和写入过程如图8 所示,CPU 对完成指针队列的写入操作和DMA 控制器对完成指针队列的读出操作如图9 所示。其中,图8 中①处是自由指针队列初始化完成之后的指针值,自由指针中存储着描述符和内存块的起始地址,自由指针队列初始化之后,CPU先从自由指针队列读取一个自由指针。图8 中②和图9 中①、③是CPU 从自由指针队列读取自由指针的仿真波形。

CPU 写入数据帧和描述符之后,根据待发送数据帧的优先级把完成指针写入对应的完成指针子队列,如图9 中②所示,CPU 把一个数据帧写入内存后对应的完成指针被写入优先级为4(最高优先级)的完成指针子队列中,等待被DMA 控制器读取。DMA 控制器检测到优先级为4 的完成指针子队列非空,如图9 中④所示,DMA 控制器从该完成指针队列读取一个完成指针,然后获取对应描述符的起始地址,通过描述符获得对应内存块的起始地址,开始读取并发送数据。数据读取完成之后,DMA控制器把指针写入自由指针队列,如图9 中⑤和图8 中③所示。

4 结语

针对TSN 网络端系统设计需求,基于Xilinx Zynq7000 系列FPGA,本文设计了支持多个逻辑队列和共享缓冲区的DMA 控制器。在发送方向上,CPU 可以根据业务流类别在内存中建立8 个指针队列,DMA 控制器可以按优先级进行业务发送;在接收方向上,DMA 控制器可以根据业务流类别将接收数据的指针写入8 个逻辑队列,供CPU 进行差异化处理。本方案可以支持时间敏感业务流和其他业务流混合传输并为不同业务流提供所需的服务质量(Quality of Service,QoS)保证。