基于sbRIO的多通道多类微弱小信号采集与处理

2021-09-28陈源宝

谢 刚, 陈源宝, 黄 双

(武汉第二船舶设计研究所,湖北 武汉 430064)

现代船舶涵盖航行操纵、动力推进、通信导航等多个环节,是典型的信息物理系统[1-3]。早期的设计中由于缺乏一体化的设计手段,导致电子信息系统烟囱化堆叠式现象普遍存在,存在信息设备冗余、异构系统众多、数据共享不畅等顽疾,对各类传感器信号均采用独立采集的方式[4-5],存在多种信息采集装置,造成一定的资源浪费。随着船舶信息系统扁平化、集成化、智能化的发展,作为数据获取源头的数据采集系统,其高密度、一体化集成需求越发强烈。进一步的,异构系统中进行集成、高通量、低噪声、大动态、兼容性的微弱信号是异质信号集成设计的难点,也是需重点解决的问题。在调研现代船舶各类传感器信号输出特点和电气特性基础上,选取两种典型传感器,进行高密度兼容集成采集,在信号采集前端通过不同类型传感器(恒压供电与ICP供电)进行电路的统一兼容化设计,采用“FPGA+sbRIO(single board RIO)”的处理架构,使用sbRIO内部多种成熟的模块资源,同时以图形化的方式实时显示各通道信号数据,从而提出一种兼容采集的集成优化设计方法。

传感器数据采集系统一般由信号采集模块与信号处理模块组成,信号采集模块用于传感器输出信号的采集,将模拟量信号转换为数字信号;信号处理模块一般采用“FPGA+控制器”的处理架构[6-7],用于处理转换后的数字信号,信号经分析后发送至远程监控终端。现有信号采集系统多采用“FPGA+DSP/ARM”的处理架构,该架构较为成熟通用,适用于大多数应用场景,然而,该架构对处理芯片的软件设计能力要求较高,同时不具备图形化的显示界面,需单独开发上位机显示程序,开发难度较大。与此同时,多数信号采集系统设计上只考虑了某一种或某一类传感器信号的采集,信号采集模块的兼容性不强,导致需针对每种传感器都设计一次信号采集模块,开发较为烦琐。

sbRIO是一种可重新配置的板载嵌入式控制器,集成了实时处理器、用户可重配置FPGA和I/O。sbRIO可轻松嵌入具有灵活性、可靠性和高性能需求的高密度应用中。同时具有以太网、CAN、USB、串行和SDHC端口。sbRIO内建多达600多个LabVIEW函数,可建立用于实时控制、分析、数据记录与通信的多线程实时嵌入式系统,极大地简化了用户嵌入式软件开发难度,同时根据不同应用场景进行模块化切换,具有良好的灵活性与可靠性[8]。

基于sbRIO具有开发速度快、灵活拓展性强等工程化应用特点,结合船舶系统各部位传感器的多通道多类微弱信号采集处理,提出了一种基于sbRIO的多通道多类微弱小信号采集与处理的方法,实验表明搭建的数据采集系统在高密度、传感器接入兼容性、本底噪声、信号一致性、带宽平坦度方面表现优异,可为智能船舶异构系统集成优化设计提供技术基础。

1 系统总体设计

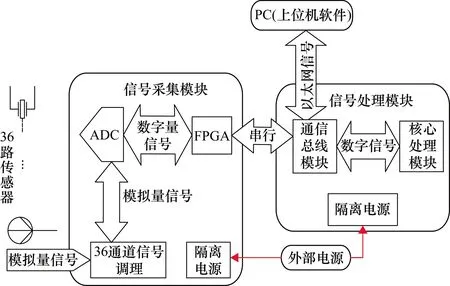

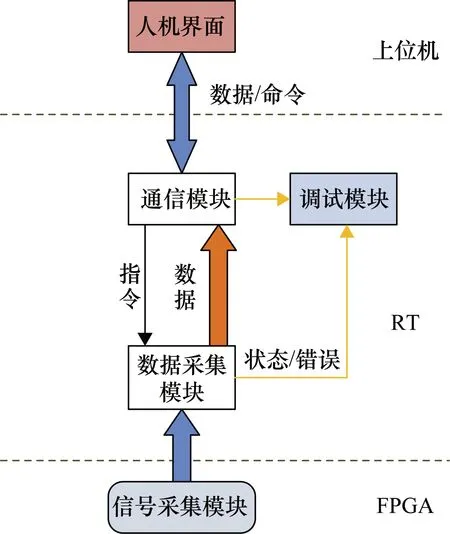

基于sbRIO的多通道多类微弱小信号采集与处理系统主要由36路传感器、信号采集模块、信号处理模块、上位机组成。具体框图如图1所示。

图1 系统原理框图

上位机软件通过图形界面配置整个采集系统各通道传感器接入类型、采样分辨率等参数,将配置指令下发给信号处理模块上的sbRIO控制器,sbRIO控制器将指令解析后发与信号采集模块,信号采集模块完成通道配置。配置完成之后接入各类传感器(涉及到两类传感器即ICP供电与恒压供电传感器,具体参数及电气特性在下一节中介绍)。传感器接入采集系统后,经过信号采集模块进行信号调理、滤波、前置放大等信号预处理后,使用ADC芯片进行模数转换后进入FPGA进行串行处理。FPGA处理之后的数据传输至信号处理模块,信号处理模块上的sbRIO控制器处理接收串行数据后,利用RealTime(简称RT)状态机进行数据的存储转换,并封装成以太网数据包上传至上位机进行实现显示与监控。上位机软件基于LabVIEW开发,通过调用RT网络通信模块与信号采集系统进行人机交互,使用模块化设计,有效地减少上位机软件开发难度,提升开发效率。

2 传感器介绍

本系统涉及到两类传感器,ICP传感器(下称I型传感器)和恒压供电传感器(下称II型传感器)。

传感器参数如表1所示。

表1 两型传感器的电气特性

由表1可知,采集系统性能参数应兼顾两类传感器的电气特性的上下限,才能实现兼容两类传感器的采集接入。因此,本系统需具备ICP恒流2~20 mA供电及恒压12~15 V供电能力,同时具备18 μV~1 V的微弱小信号采集处理能力。与此同时,本系统采样率为204.8 kHz,采样位数为24 bit,带宽为10 Hz~40 kHz。

3 系统硬件设计

信号采集系统硬件部分由信号采集模块、信号处理模块两部分组成。

3.1 信号采集模块

信号采集模块用于完成传感器模拟信号的调理和传感器信号兼容接入采集,主要构成包括驱动前端传感器接口转换、信号放大和A/D转换[9]。每通道能够以高达204.8 kHz的速率对信号进行数字化,从而实时、无失真地对传感器信号进行采集和传输。

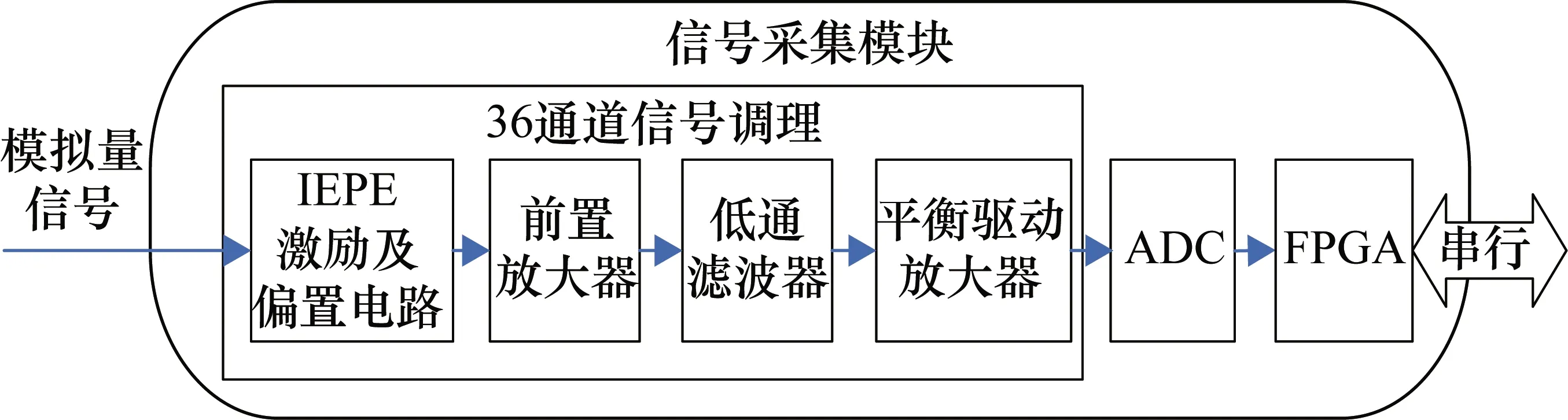

信号采集模块由IEPE激励及偏置电路、前置放大器、低通滤波器、平衡驱动放大器、ADC和FPGA组成,原理如图2所示。

图2 信号采集模块原理框图

信号采集模块根据所使用的传感器按其原理设计为恒流源驱动(I型传感器)和恒压源驱动(II型传感器)两种通道类型,从而实现两类传感器的兼容接入。

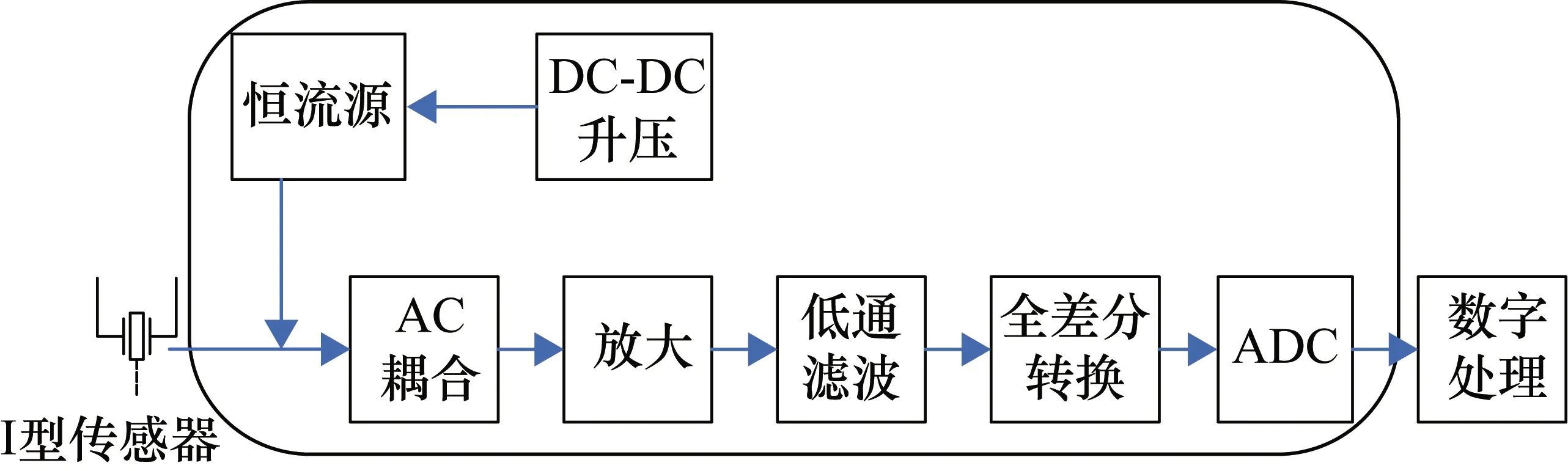

恒流源驱动电路设计如图3所示。

图3 恒流源驱动电路原理框图

恒流源驱动电路适用于采用恒流源驱动的I型传感器,其中恒流源输出最大10 mA(可以通过更改电阻值改变其驱动电流),其恒流源驱动电压为24 V;AC耦合采用4.7 μF耦合电容,降低低频响应;为保证AC耦合和后端低通滤波电路的独立性,在此处需要使用放大电路进行隔离;对于后端的低通滤波器,因为I型传感器的频响范围在高频处为10 kHz,低通滤波器设计采用Sallen-Key滤波器;后端其输入为全差分,为充分应用其输入量程以及降低噪声,在ADC前端采用增益为1的全差分电路,用于隔离驱动后端的ADC芯片。

恒压源驱动电路设计图4所示。

图4 恒压源驱动电路原理框图

该调理电路与恒流源驱动电路不同之处在于驱动电源,II型传感器为恒压驱动,采用15 V驱动电压(可用过调节电阻值改变恒压电压值)。因为此传感器的频响范围在高频处为40 kHz,低通滤波器可以设计截止频率为45 kHz、增益为1的Sallen-Key 滤波器。

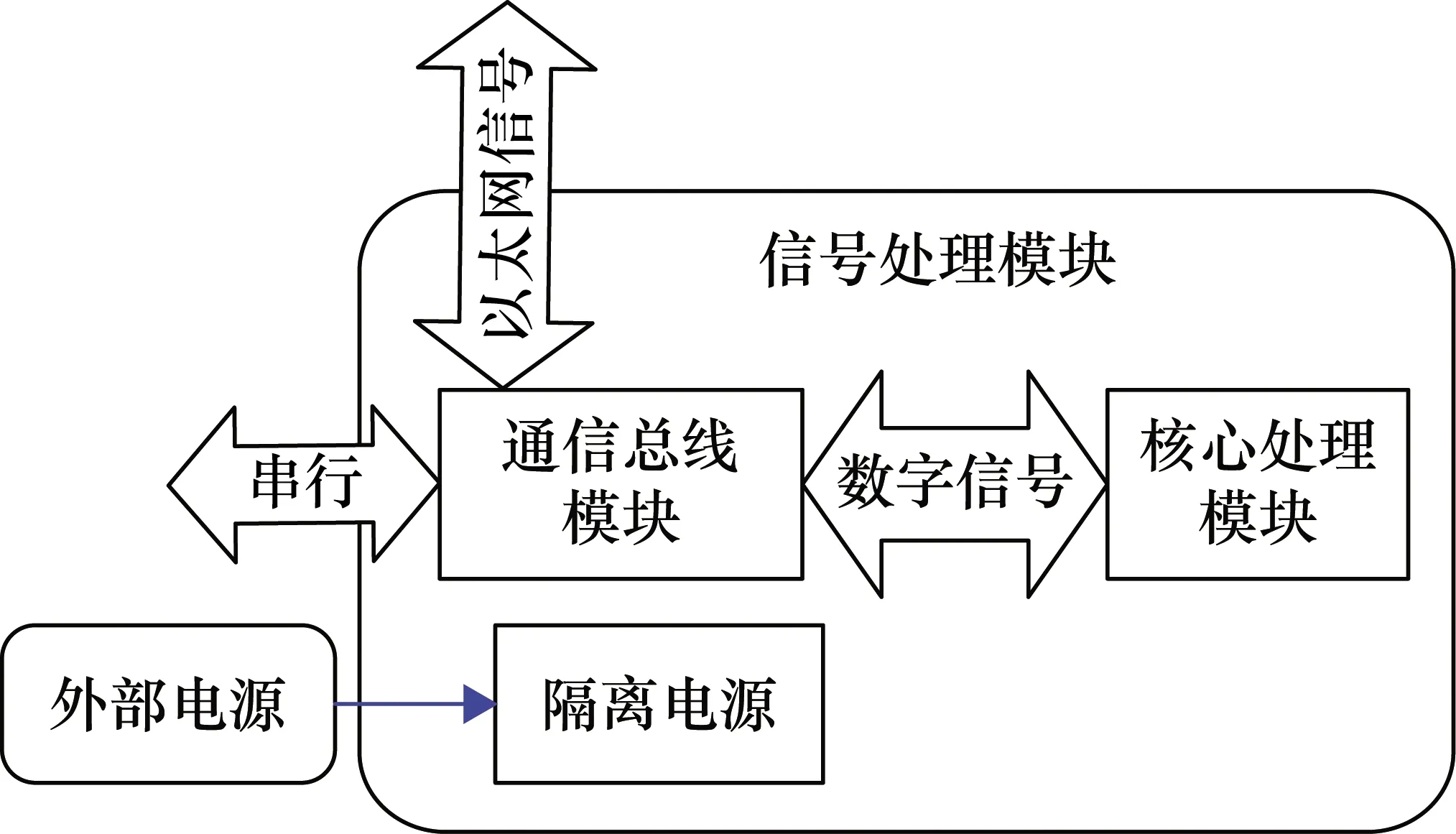

3.2 信号处理模块

信号采集模块用于完成串行数据解析、数据存储转换和与上位机的网络通信。信号处理模块主要由核心控制模块、电源模块、通信总线模块3部分组成,原理框图如图5所示。

图5 信号处理模块原理框图

核心控制模块为信号处理模块的核心部分,该模块采用单板嵌入式系统sbRIO-9651作为实时控制器,用于对数据的实时处理。sbRIO-9651结合了Xilinx Zynq完全可编程片上系统(SoC)、通用组件(如内存)和完整的中间件解决方案,以最大限度减少嵌入式控制或监测应用的设计时间和风险,该控制器搭载了NI Linux RealTime,兼具了实时操作系统的性能和Linux的开放性,具有较低的开发难度与良好的工程应用性。sbRIO模块实物图如图6所示。

图6 sbRIO模块

4 系统软件设计

信号采集系统软件以硬件结构体系为基础,结合模块化的软件设计思想开发而成,具备数据实时采集、数据实时显示、采集参数配置管理等功能。软件框架如图7所示。

图7 系统软件框图

系统软件由FPGA软件、RT软件、上位机软件3部分组成。其中FPGA软件运行于信号采集模块FPGA上,主要实现数据采集与转换功能;RT软件运行于sbRIO实时控制器中,主要实现FPGA传输的数据协议的转换,同时封装成以太网数据包发送至上位机;上位机软件运行于监控终端,主要实现人机交互功能,如数据显示、采集参数配置等。FPGA和RT均集成在信号采集系统中,通常称为下位机,上位机与下位机之间通过标准的TCP协议进行通信。

FPGA软件用于控制ADC芯片进行模数转换,并将数字量进行高速缓存,按一定协议发送至RT软件。

FPGA软件主要为逻辑控制,通过控制采集时钟、FIFO缓存、RST 信号线等逻辑实现[10]。

RT软件主要由3个模块组成,分别是数据采集模块、调试接口模块及核心的网络通信模块。数据采集模块接收由FPGA采集处理后的传感器信号数据,并以相应协议进行数据解析后发送至网络通信模块。网络通信模块收到数据采集模块解析后的数据后,对所有通道传感器数据进行统一封装,通过TCP网络协议发送至上位机进行显示或处理。同时,网络通信模块可接收上位机的配置参数等指令信息,并按相应协议转换至数据采集模块,实现数据采集参数配置。调试模块与数据采集模块及网络通信模块相连,用于监视两模块的运行装置,将两模块运行过程中的状态或错误信息发送至上位机。

上位机软件为基于LabVIEW开发的显示软件,通过NI自带的LabVIEW库进行开发,极大地降低了开发难度,缩减了开发周期,适用于工程化应用和快速开发[11]。

5 测试结果分析

按照上文进行软硬件设计之后,通过一系列实验对设计后的系统进行功能性能验证测试,主要包括36通道测试、系统本底噪声测试、信号一致性测试、传感器兼容接入测试、多通道信号并行采集测试。系统测试实验原理示意图如图8所示,测试仪器及工具见表2。其中对于36通道测试、信号一致性测试采用标准信号发生器作为系统信号输入,本底噪声测试使用50 Ω短路端子作为系统信号输入,传感器兼容接入测试使用两型传感器作为系统信号输入。

图8 测试实验示意图

表2 测试仪器及工具

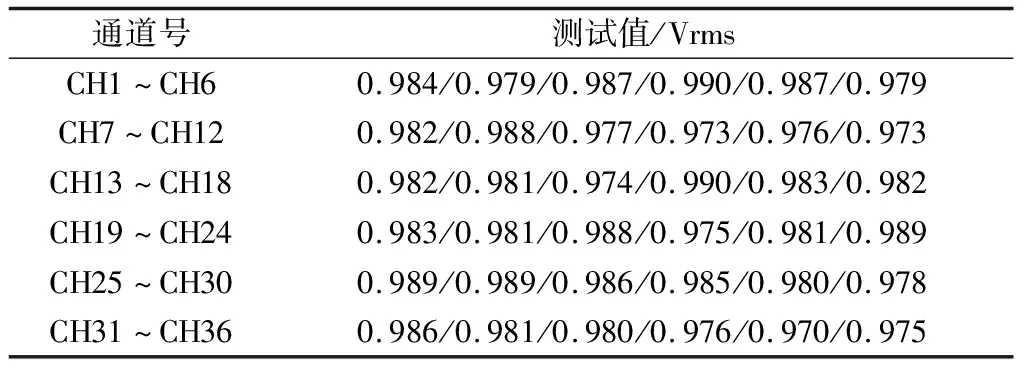

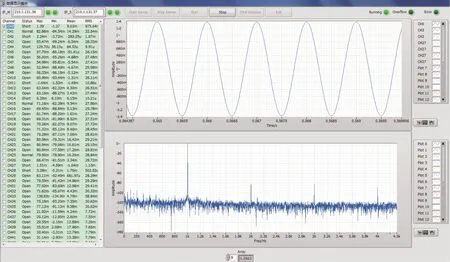

5.1 36路通道测试

按图8将标准信号(频率1 kHz,有效值1 V的正弦波)与系统信号输入接口相接,依次输入每个通道,用上位机软件将信号采集系统的采样频率设置为204.8 kHz,如图9所示,将fs设置为204800。软件开启采集,上位机能实时显示各通道数据和波形,如图10所示,RMS一列为各通道电压有效值数据,居中上部窗口为实时显示波形,下部窗口为频谱信息,下同。记录每个通道的电压值,如表3所示。

表3 36通道测试数据

图9 采样率设置界面

图10 各通道数据及波形显示界面

测试结果表明,信号采集系统能同时正确采集所有通道信号,并实时在软件上进行图形化显示。

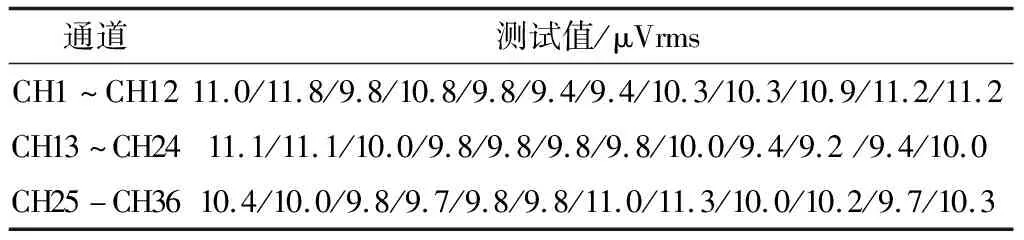

5.2 本底测试

按图8将50 Ω短路端子与系统信号输入接口相接,用于测试每个通道的本底噪声,同时将信号输入模式设置为IEPE激励模式如图9所示,记录每个通道的本底噪声,如表4所示。

表4 本底噪声测试数据

测试结果表明,信号采集系统每个通道本底噪声均小于18 μV,满足I型传感器的信号下限,因此,该信号采集系统最小能支持本底噪声电压值以上的微弱小信号采集,满足系统设计要求。

5.3 信号一致性测试

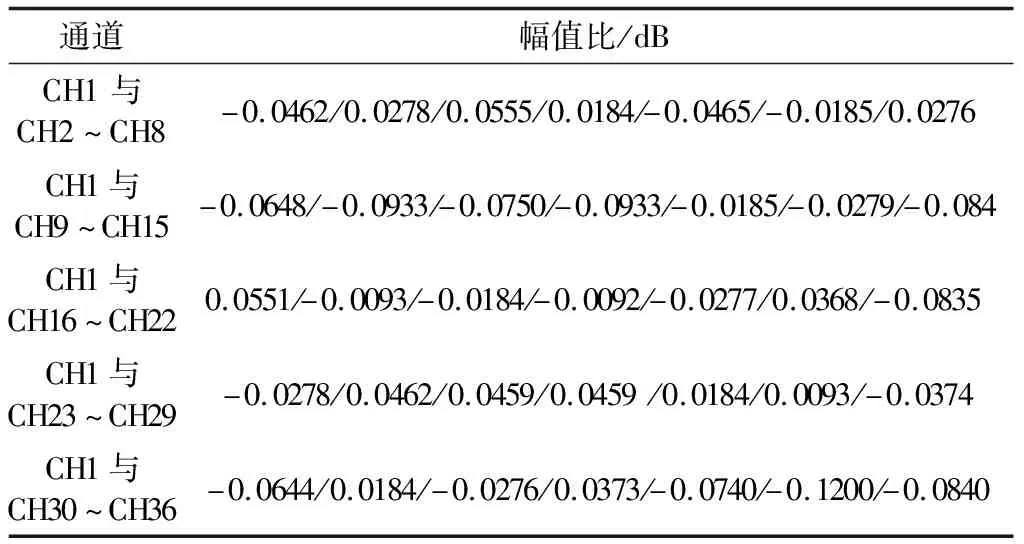

根据4.1节的数据和式(1),计算结果如表5所示。

表5 信号一致性测试数据

ΔG=20 log(ai/a1)

(1)

测试结果表明,ΔG在±0.3 dB以内,满足JJG834—2006《动态信号分析仪鉴定规程》中的信号一致性B级要求,具有良好的信号一致性。

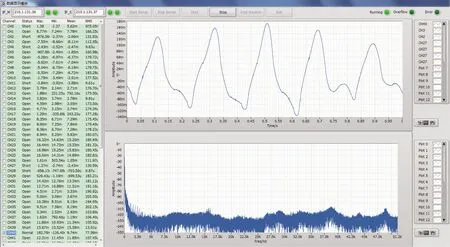

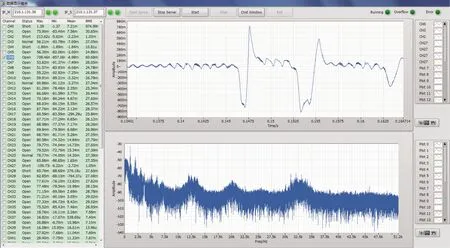

5.4 传感器兼容接入测试

按图8将I型传感器与系统信号输入接口相接,保持采样率不变,同时将信号输入模式设置为IEPE激励模式,如图9所示。软件开启采集,敲击I型传感器后,上位机能实时显示传感器信号波形,如图11所示。更换II型传感器,将信号输入模式设置为DC激励模式,如图12所示。软件开启采集,敲击II型传感器后,上位机能实时显示传感器信号波形,如图13所示。

图11 I型传感器信号波形显示界面

图12 II型传感器输入模式配置界面

图13 II型传感器信号波形显示界面

测试结果表明,信号采集系统能兼容两型传感器信号采集,只需要通过软件配置即可。

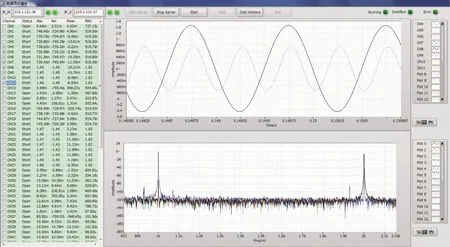

5.5 多通道信号并行采集测试

本系统为兼容两型传感器的36通道并行采集系统,为了验证本系统多通道信号并行采集能力,使用标准信号源对8路通道同时注入标准正弦信号,其中CH4~CH7注入频率2 kHz、有效值500 mV的正弦波,其中CH8~CH11注入频率1 kHz、有效值1 V的正弦波,上位机能实时显示各通道采集波形及频谱,如图14所示,RMS一列为采集到的有效值数据,从图中可以看出,信号采集系统可实现多通道信号的并行采集,并能正确显示注入信号波形与频率,并达到相应精度要求。

图14 多通道信号并行采集测试

6 结束语

介绍了一种基于 sbRIO的多通道多类微弱小信号采集与处理的方法,该方法通过在信号采集前端对恒压供电及ICP供电传感器进行电路上的统一兼容化设计,利用sbRIO内部多种成熟的模块资源对数据进行实时处理,同时以图形化的方式实时显示各通道信号数据,实现多通道多类传感器的实时监测。实验表明搭建的信号采集系统在高密度、传感器接入兼容性、本底噪声、信号一致性、带宽平坦度方面表现优异,可在204.8 kHz采样频率下采集36路18μV~1V(RMS)的微弱小信号,可为智能船舶相关数据采集系统设计提供技术基础。