基于FPGA的以太网双目图像采集系统设计

2021-09-04张谷祥王晓曼赵海丽杨威

张谷祥,王晓曼,赵海丽,杨威

(长春理工大学 电子信息工程学院,长春 130022)

图像处理技术广泛应用于各行各业,如医疗卫生、航空航天等,而图像采集是图像处理的前提保证,采集到原始图像的质量将直接影响到图像处理最终的效果[1]。目前在测量位姿的方法中,双目视觉测量是研究的课题之一,它是利用双摄像头拍摄同一场景,根据视差来获得三维信息,然后根据位姿解算算法得出位置和姿态数据。由于在双目视觉的位姿测量系统中要求两摄像头同步工作、并行运算,传统的串行器件CPU不能并行地控制两摄像头同步工作和处理数据,为了满足要求,故系统提出了一个基于FPGA的以太网双目图像采集系统。由于FPGA相比CPU拥有并行处理的特点,并且具有集成度高、实时性强,功耗低的优点,可在每个时钟周期完成多样的处理任务,因此FPGA满足控制要求。

本系统以EP4CE10F17C8现场可编程门阵列为主控单元、以CMOS图像传感器OV5640为图像采集单元,以SDRAM为数据存储单元,以PHY为以太网收发器单元,以PC为图像显示单元,实现了图像的采集、存储、传输和显示。

1 系统硬件设计

图1是系统的总体框图,主要有FPGA、图像采集设备、图像显示设备等组成。其中OV5640图像传感器负责图像采集,FPGA则是整个系统的控制核心单元,是负责图像数据的处理和各模块的控制等。

图1 系统总体框图

SDRAM用来存取采集的图像数据,PC机通过网口与FPGA通信来显示采集的图像数据。FPGA采用的是原Altera公司Cyclone IV E系列产品,该系列产品经过优化工艺,能够把内核工作电压降低到1.2 V,非常适合应用在对成本和功耗有较高要求的场合。根据串行摄像机控制总线SCCB来完成OV5640图像传感器的初始化和控制像素显示窗口范围、消隐行范围、增益范围。之后便通过摄像头DVP接口把输出的RGB565图像数据传给FPGA中的写FIFO模块,再由FPGA内部的SDRAM控制器模块对写FIFO模块中数据进行操作,目的是存入到外部SDRAM芯片上,当外部有读请求时,再通过读FIFO模块来进行数据读操作,并将读到的数据通过网线传输到上位机来完成数据的显示。

1.1 图像采集模块

图像采集采用的是OmniVision公司生产的一款1/4英寸、最高500 W像素图像输出能力的互补金属氧化物半导体(CMOS)图像传感器OV5640,其支持RawRGB、RGB(RGB565、RGB555、RGB444)、CCIR656、YUV(422/420)、YCbCr(422)和压缩图像(JPEG)输出格式,标准的SCCB接口,兼容IIC接口,有自动曝光(AEC)、自动白平衡(AWB)、自动消除灯光条纹控制功能,具有非常高的性价比。它通过定制的2线/3线制串行摄头控制总线(serial camera control bus,SCCB)进行控制,输出并行的10位图像数据,图像输出最高可达30帧/s,满足视觉流畅的需求。两片图像传感器OV5640负责图像的采集,并且本身可以输出10位数据,但大多数情况下采用高8位数据。输入参考时钟XCK由FPGA直接提供,不需要额外晶振提供[3]。图像采集电路示意图如图2所示。

图2 摄像头与FPGA的电路连接示意图

1.2 数据存储模块

系统采用的SDRAM存储器是HY57V281620芯片,该芯片总128 Mbit,4个bank,每个bank有32 Mbit存储单元,系统设置每个存储单元存储16 bit,则每个bank有4 096行×512列,对于SDRAM的读写是以突发的方式进行的,对SDRAM的操作是从一个指定的地址开始,并且按照编程好的数量的地址,顺序读写数据,其工作为3.3 V,拥有一个同步接口,SDRAM的所有信号都是在时钟信号的上升沿被寄存,芯片的工作时钟通过FPGA的PLL提供,为100 MHz。数据存储电路示意图如图3所示。

图3 FPGA与SDRAM的电路连接示意图

1.3 以太网传输模块

系统通过一片RTL8201以太网PHY芯片提供对以太网连接的支持,RTL8201是一片10 M/100 M自适应以太网收发器,提供MII/SNI接口MAC连接,MII接口的发送时钟,由PHY芯片产生,该系统工作在100 Mbps时,时钟为25 MHz,MII接口发送数据使能,高电平有效,每个发送时钟上升沿发送4位数据,RJ45采用的是HR91130C,该连接器自带隔离变压器和终端电阻,有利于改善系统的EMC/EMI性能[4]。以太网传输电路示意图如图4所示。

图4 FPGA与RTL8211的电路连接示意图

2 系统软件设计

软件设计主要有图像采集驱动模块逻辑设计、数据存储模块逻辑设计、以太网模块逻辑设计这三个部分。其中图像采集驱动模块逻辑设计来完成OV5640寄存器初始化和图像数据的获取;数据存储模块逻辑设计来完成图像数据的存储;以太网模块逻辑设计来完成图像数据的读取和传送。开发工具使用的是QuartusⅡ,程序编写使用的是Verilog HDL语言,仿真使用的是Modelsim工具。最终程序编译下载到FPGA开发版来进行上位机显示,以验证系统设计的正确性。

2.1 图像采集驱动模块逻辑设计

图像采集驱动模块逻辑设计分摄像头的初始化和图像数据采集,其中摄像头初始化在前,图像数据采集在后。图像传感器OV5640寄存器众多,并且寄存器地址不是连续的,用寄存器地址累加行不通,这里解决的方法是使用ROM查找表,查找表里存储的是寄存器地址和数据,ROM每个存储单位设置为24位,其中高16位用来存储寄存器地址,低8位用来存储该寄存器需要设置的初始值,当启动SCCB控制器写操作时,依次从查找表取出值写入到OV5640寄存器,直到寄存器写完。SET_CNT是设置需要初始化寄存器的个数,Comb_logic表示组合逻辑用来分开寄存器地址值和初始值。其初始化模块框图如图5所示。

图5 初始化模块框图

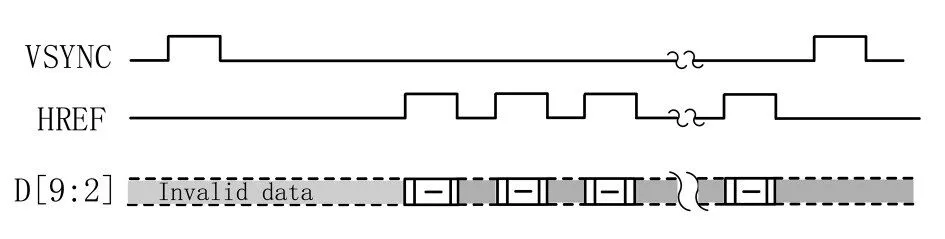

图像数据采集时当检测到帧VSYNC为上升沿时表示一帧图像数据传输的开始,在之后行同步信号HREF为上升沿时表示一行图像传输的开始,在HREF为高电平期间,一个像素时钟PCLK,输出8位数据,该系统设置每个摄像头的像素输出总大小为400×480,输出格式设置为RGB565,即每个像素是16位,每2个字节组成一个像素的颜色,底字节在前,高字节在后,这样每行输出总共有400×2个像素时钟,输出400×2个字节。如图6为DVP接口时序图。

图6 DVP接口时序图

根据DVP时序图编写Verilog HDL程序,通过Modelsim仿真得到图7图像像素捕获局部仿真图,该图并没有仿真全部的像素而是人为设定了部分像素数据,主要目的是来验证程序功能是否正常,其中Yaddr和Xaddr是行列计数器,在帧VSYNC为上升沿时都清零,当检测到行HREF为上升沿时Xaddr加一,一行结束时清零的同时Yaddr加一,循环往复,直到一帧结束时都清零,该功能用于记录当前的像素点几何位置,方便其他模块操作。当两个8位数据拼接成16位数据时DATAVALID为高电平,表示可以取出当前像素值来传输给下一个功能模块。根据仿真图显示程序功能达到了要求。

图7 图像像素捕获局部仿真图

2.2 数据存储模块逻辑设计

数据存储模块逻辑设计由两个写FIFO、两个读FIFO和SDRAM控制器模块组成。其中两个写FIFO是用来缓存采集的两个摄像头数据,摄像头的像素时钟为FIFO的写时钟,这里为24 MHz,摄像头的场信号作为FIFO的写请求,这样就保证了数据的采集缓存一致,不丢失数据。该系统设置写入的FIFO数据长度超过256个时,就可以读出写FIFO数据,读出的数据送入SDRAM控制器,再写入SDRAM,读取写FIFO时钟为100 MHz。读FIFO的写时钟同样为100 MHz,写请求是当写入的数据小于256时有效读FIFO的读请求由外部指定,读时钟和以太网发送时钟同样为25 MHz,保证数据同步操作,防止丢失数据。SDRAM控制器是用来完成SDRAM读、写等操作。

SDRAM上电后,系统处于空闲状态,在上电初始化完成后进入刷新状态,其上电初始化是来关闭SDRAM的BANK,使BANK处于空闲状态并且加载SDRAM模式寄存器来确定读和写采用何种方式,该系统设置的突发长度为8、运行模式设置为标准模式、突发类型设置为顺序、列选通潜伏期设置为2。刷新状态如果有读或写请求到来,状态将会转移到相应的读或写状态,其刷新状态是为了保证存储在SDRAM中的数据不丢失,刷新周期由定时器产生[5]。读或写状态各自主要负责读写数据操作,整个状态机中对刷新操作、写数据操作、读数据操作是有一个优先级的,也就是某两个或多个操作请求同时到来时先执行哪个操作是有事先规定的,这里规定的优先级是刷新操作>写操作>读操作[8]。其状态机转移图如图8所示。

图8 状态机转移图

通过仿真得到SDRAM控制器模块局部仿真图,如图9写操作和图10读操作所示,对SDRAM的操作,是通过命令来控制的,命令由sdram_cs_n、sdram_ras_n、sdram_cas_n、sdram_we_n这四个控制信号组合成不同状态来表示,同时地址总线sdram_addr和sdram_dqm总线作为辅助信号,提供与命令相对应的地址或者参数命令。使用的SDRAM仿真模型由镁光官网提供。通过仿真图可以看出突发长度为8并且写入的指定某个地址数据与该地址读出的数据相同,说明编写的SDRAM控制器模块功能是正确的。

图9 SDRAM控制器写操作局部仿真图

图10 SDRAM控制器读操作局部仿真图

2.3 以太网模块逻辑设计

以太网模块逻辑设计分以太网发送图像控制逻辑和以太网传输数据逻辑,其中以太网发送图像控制逻辑是用来从SDRAM中读取图像数据并写入到以太网传输数据逻辑。以太网发送图像控制逻辑以RTL8201芯片提供的25 MHz作为时钟。首先进行上电或者是复位计数,该系统设定当计数到65 024时产生一次帧同步信号frame_sync,目的是清除SDRAM读端口中的FIFO中的数据,保证从开始读一行完整的图像数据,之后计数到65 534时便使能图像发送信号send_en,在该信号使能的条件下,判断以太网传输数据逻辑中的双时钟异步FIFO是否有1 602个字节空间能够存储行号和图像数据,如果没有则继续等待,如果有则对外部发出读请求信号sdram_rdrep来读取SDRAM数据,同时根据读到的数据进行行列计数。当行hcnt计数到800时便从零开始重新计数,同时列vcnt自动加一,直到480列结束,也就是一帧的结束。每次根据行为零发送此刻的列数字作为行号,以便确定在二维平面中显示的位置,循环往复之后的每一帧都是这种处理过程。如图11所示为以太网发送图像控制逻辑局部仿真图,结果显示达到了数据传输要求。

图11 以太网发送图像控制逻辑局部仿真图

该系统的以太网传输数据逻辑是基于UDP/IP协议,虽然该协议是一种不可靠传输,即发送方只负责发送数据,对接收方是否正确的接收数据不关心,但是UDP实现起来简单、灵活、传输数据快并且在视频实时传输显示中图像数据仅仅显示在屏幕上,可以接受一定程度的数据丢包。要实现用户数据的传输,其核心是把各个层的数据相互封装起来[7-10]。如图12所示,应用层的用户数据构成传输层的数据段,传输层的UDP报头和数据段构成网络层的数据段,网络层的IP报头和数据段构成数据链路层的数据段,数据链路层的MAC帧头、数据段和帧校验在物理层MII接口下实现数据的传输[6]。MII接口协议是在使能高电平条件下在每个时钟上升沿传输4位数据,如图13所示。

图12 数据分层框图

图13 MII接口协议

以太网的MAC帧数据字段范围一般在46到1 500字节,这与该系统每次传输1 602个字节不相符,这里解决的办法是开通以太网的巨型帧,即可实现双目图像的传输。发送数据时,采用Wireshark工具进行抓包[9],如图 14所示,测试系统与电脑完成连接,由图14中可知,源MAC地址为(00:0a:35:01:fe:c0),源端口为 5000,源 IP为 192.168.0.2,目的端口为 6 000,目的 IP为169.254.67.8,UDP数据包中有1 602个字节。

图14 Wireshark抓包图

UDP发送模块检测到FIFO写满1 602个字节时,就将数据打包,通过MII接口总线发送给PHY芯片,PHY芯片再将数据通过网线发送至上位机来显示。

首先需要发送的是MAC帧头,即前导码(7个55H)、帧开始符(D5H)、目的MAC地址、源MAC地址、类型与长度(0800H),其次是帧的数据字段,最后是帧的校验序列。如图15所示为以太网传输数据局部仿真图,结果显示达到了数据传输要求。

图15 以太网传输数据局部仿真图

3 结果与显示

读取SDRAM两个读FIFO的数据,就可以读取到两个摄像头存储在SDRAM中的图像数据,该系统设置每个摄像头的像素输出大小为400×480,上位机设置分辨率为800×480,则需要读取某个摄像头某行数据后紧接着读取另一摄像头同一行数据传给上位机,如此上位机某行顺序显示了两个摄像头同一行数据。系统以读取读FIFO的时钟进行计数,当计数到400时变换读请求,即可达到变换读取图像数据的目的,在发送给上位机每行数据之前需要发送两个字节大小的行号,以辅助上位机在二维平面中显示的位置。如图16所示为单网口双目图像采集显示实例。

图16 双目采集图

4 结论

本文基于FPGA的以太网双目图像采集系统设计,完成了两摄像头的同步工作、并行运算数据的要求同时系统具有简单可靠、资源占用少、扩展能力好的特点,可便于后续双目视觉算法的研究与验证。