近场通信卡超高数据速率解调解码电路的实现

2021-08-20曾素馨肖时茂

曾素馨,肖时茂

(1.中国科学院微电子研究所智能感知研发中心,北京 100029;2.中国科学院大学电子电气与通信工程学院,北京 100049;3.南京中科微电子有限公司,南京 210018)

NFCIP-1标准和早期ISO/IEC 14443协议规定的数据传输速率最高达848 Kbps,随着芯片存储容量不断加大,近距离无线通信技术(near field communication,NFC)通信要求在低功耗的同时追求更高的数据速率。后来的ISO/IEC 14443 VHBR修正案[1]提出2ASK解调的理论最高速率能达到6.78 Mbps,英飞凌[2]在此基础上提出了超高数据速率(very high bit rate, VHBR)技术,使得近场通信技术能兼容更高的通信速率。文献[3]提出2ASK实现6.78 Mbps传输速率对天线等结构的要求很高,且有较高误码率,并不适用于实际应用;文献[4]中的m-ASK方法需要电路能精确地检测多种信号幅度,相比于2ASK方式,需要增加电路来补偿幅度的非线性失真,还可能会影响电源的稳定性;m-PSK方法在VHBR修正案中,理论最高速率可以达到27.12 Mbps,但接收器设计对相位噪声、码间串扰等问题的处理要求很高,在以低功耗、低成本为优势的NFC实际应用中竞争力并不强。为改进基于PICC接收电路,使接收数据速率可以覆盖标准的106~848 Kbps以及VHBR修正案中1.70 Mbps和3.39 Mbps要求,以适用于大多数NFC通信场景,现将先分析接收原理,再给出对应的改进方案。

1 电路原理及结构设计

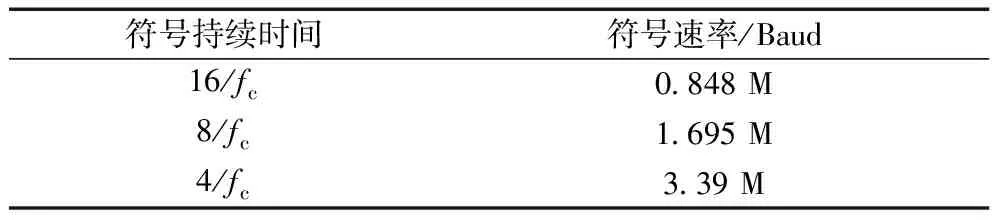

NFC应用中,VHBR主要通过提升符号速率或增加每个符号表示的比特数两种方式实现。如文献[1,4]提到,每符号多比特的m-ASK,m-PSK方法会较大增加硬件复杂度和功耗,同时也不利于与标准106~848 Kbps速率电路兼容,故采用2ASK方法,通过第一种提升符号速率的方式来实现。部分VHBR对应的符号持续时间和符号速率如表1所示,其中fc为载波频率,近场通信应用中载波频率为13.56 MHz。

表1 2ASK符号持续时间与速率

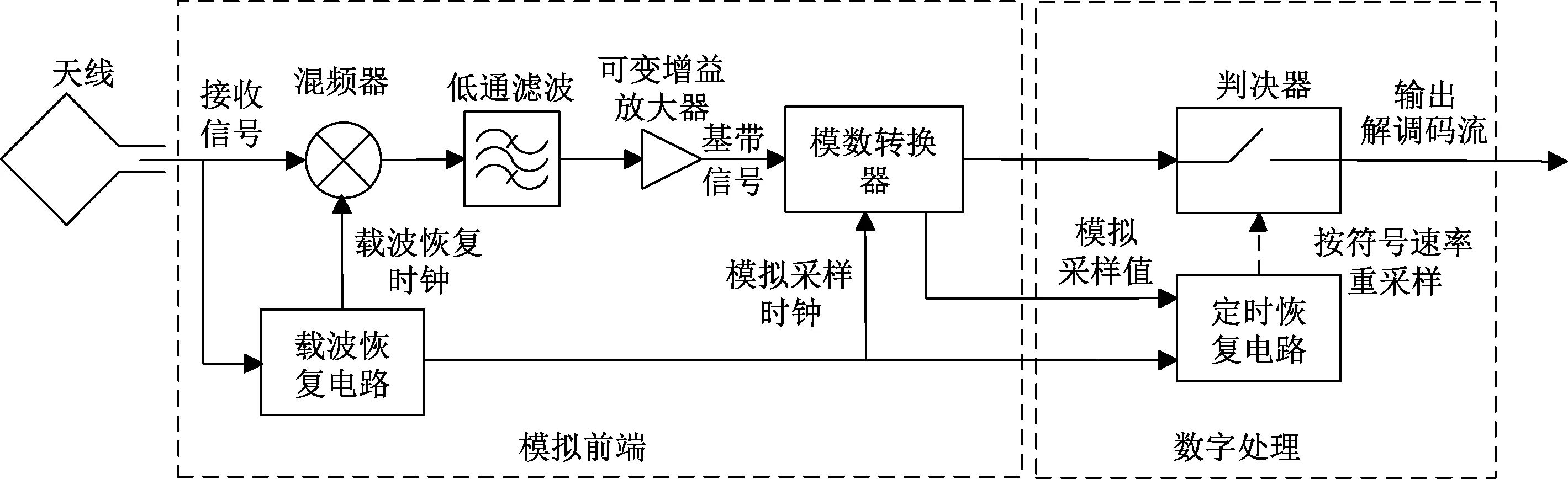

数据传输过程中,为正确恢复发送端信号,接收机需要找到每个符号的起止时刻,从而在符号中间最佳采样点处进行采样判决。由于信号传输过程中的时延τ未知,接收与发射信号的时钟也不同步,在接收端需要同步处理来得到正确的同步时钟。无线通信中,常用全数字方式的定时恢复[5],先是由固定采样率的本地时钟对接收信号进行采样,再将采样后的信号经过全数字处理实现定时恢复,此种方式对本地时钟的要求更低[6],且便于实现。基于将接收信号按本地时钟采样,再用全数字方式实现定时恢复的思路,设计电路模块简图如图1所示。

图1 基于幅移键控的超高速率接收器

带通ASK调制信号r(t)表示为

r(t)=A(t)ej(2πfct+φ)

(1)

式(1)中:A(t)、φ分别为接收信号的幅度和相位。

调制信号r(t)由天线接收,进入模拟前端,首先送入载波恢复电路,由载波恢复电路提取载波,送入正交混频器相乘,再经由低通滤波器滤去倍频项,可变增益放大器(VGA)补偿接收增益,得到模拟基带信号x(t),由数模转换器(A/D)按恢复的载波分频得到的采样时钟对x(t)进行采样,采样频率为fs=fc/2。采样得到的基带信号送给数字电路做信号处理[7]。由于信号在A/D的采样率与符号时序并不同步,不能保证在最佳采样点进行采样,需要定时恢复电路(timing recovery circuit,TRC)来提取正确的定时信息,按符号速率对信号重新采样,从而准确地恢复原始发送数据[8]。TRC与载波恢复独立,不受载波相位的影响[9]。TRC是接收端正确判决数据的基础,也是影响系统误码率的重要因素,其性能的好坏直接影响整个通信系统的性能。

2 TRC

定时恢复电路有数模混合、全数字等实现方式,其中全数字实现的方式更加节省资源与功耗;从设计结构上来说,有反馈(feedback)和前馈(feedforward)两种,其中前馈方式收敛快但精度较低,适用于突发通信,不适用于NFC中连续传输模式通信,故采用定时精度更高的反馈结构。全数字方式实现的定时恢复电路结构示意图如图2所示。

从模拟前端来的数字基带信号进入定时恢复电路,由于对信号x(t)的采样速率固定为fs=fc/2,与符号速率不同步,需要通过插值来调整定时,此后对插值的结果计算定时的误差,通过反馈通路来调整下一次的插值点,直到时钟同步。

插值器(interpolator)本质上是一种低通滤波器[8],其在信号值上而不是时钟上进行插值。假设信号采样间隔为Ts,插值器的采样间隔为Ti,第k个插值器采样点的基本指针为mk,分数指针为μk,插值滤波器系统函数为hI,插值滤波器的标号为i。根据文献[5]的插值算法推导,第k个符号插值点的计算可以表示为

(2)

式(2)中:I=I2-I1+1为滤波器长度;基本指针mk指示信号的采样点,分数部分μk指示滤波器的采样点。插值器采用线性滤波函数,即

(3)

式(2)和式(3)中各参数满足

(4)

式(4)中:int(z)为不超过z的最大整数。

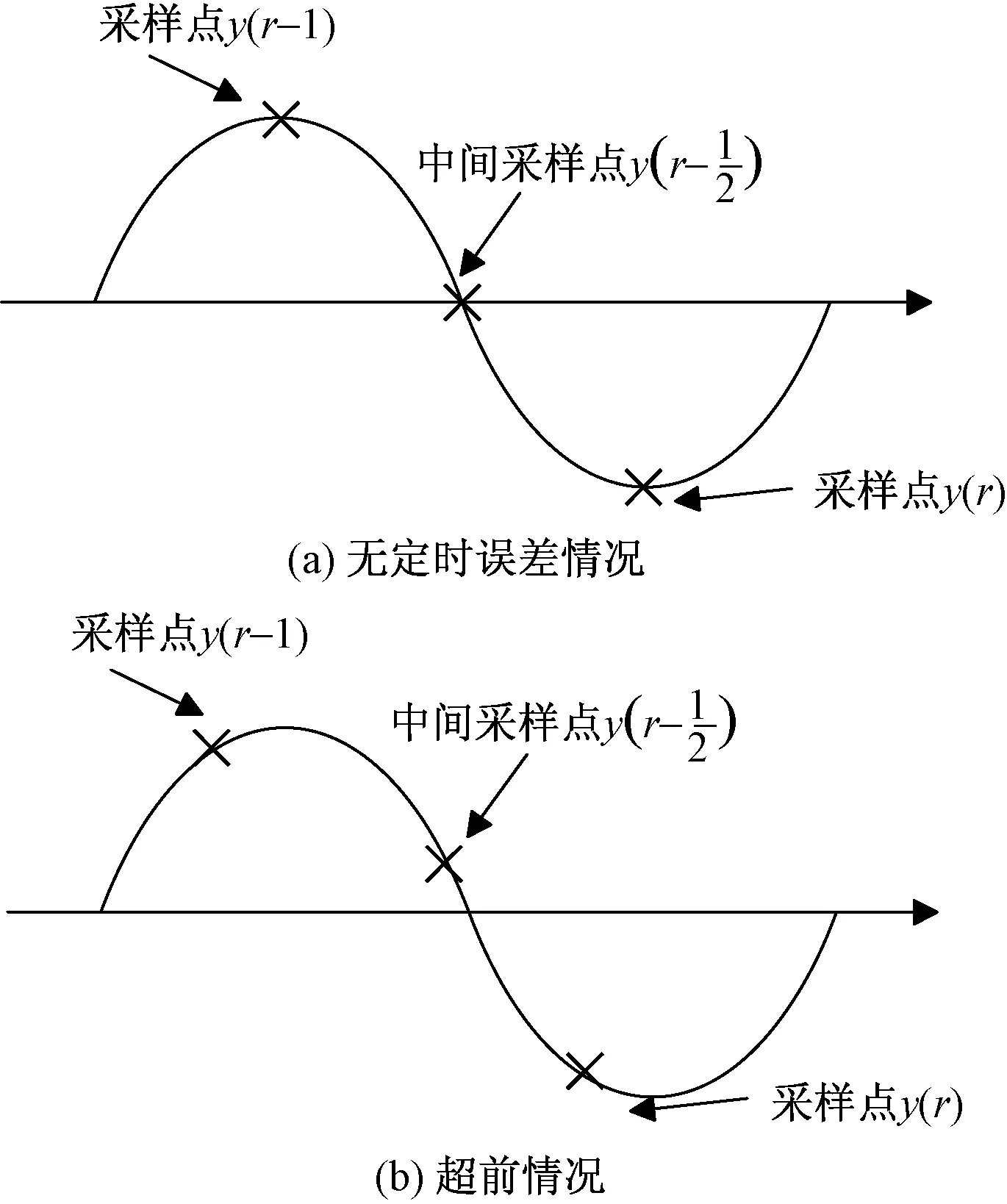

定时误差检测(timing error detector,TED)用于检测定时误差,确定正确的插值间隔。传统的波差法(wave difference method,WDM)等方法[5]在每个符号中需要有4个采样点,而Gardner算法将其减至每符号两个采样点,提高了电路的效率。TED采用典型的Gardner算法[5,10],此时定时恢复与载波相位是独立的。Gardner TED对每个符号有两个采样点,一个对应符号内最佳采样点,一个为相邻最佳采样点中间时刻的内插值,即中间采样点。

假设e(r)为第r个符号的定时误差,可以表示为

(5)

式(5)中:yI为同相分量;yQ为正交分量。

其中基带信号插值y(r)受传输时延和随机噪声影响,可以表示为

(6)

图3 采样位置

计算得到的定时误差e(r)序列进入环路滤波器(digital loop filter,DLF),输入噪声及高频分量被抑制,序列平滑处理后,得到用于调整定时误差校正电路的控制字W(mk)。在没有定时误差时,理论上e(r)=0,环路滤波器的输出也为0;而实际由于噪声的存在,环路滤波器的输出为噪声信号,从而引起TED定时抖动[11-12],故可以在DLF输出乘上一个小于1的环路系数G来减小定时抖动。

环路滤波器输出的控制字进入数字控制振荡器(digital control oscillator,DCO),为插值器提供计算所需的信息,即两个相邻的x(m)信号采样点集合,由mk标号;以及两个滤波器采样点集合,由μk标号。插值位置的控制由模1计数器控制,其工作的平均周期为Ti,当DCO寄存器复位重新进入循环时即计算新的插值点y(kTi)。假设DCO寄存器的内容为η(mk),那么控制字以及μk的提取公式为

(7)

3 设计实现

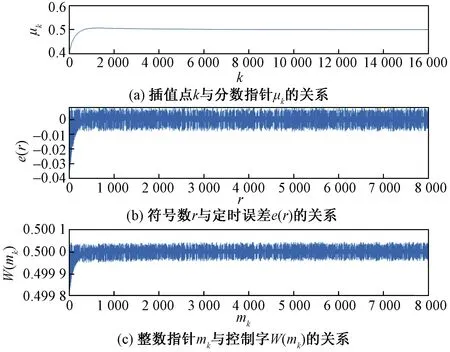

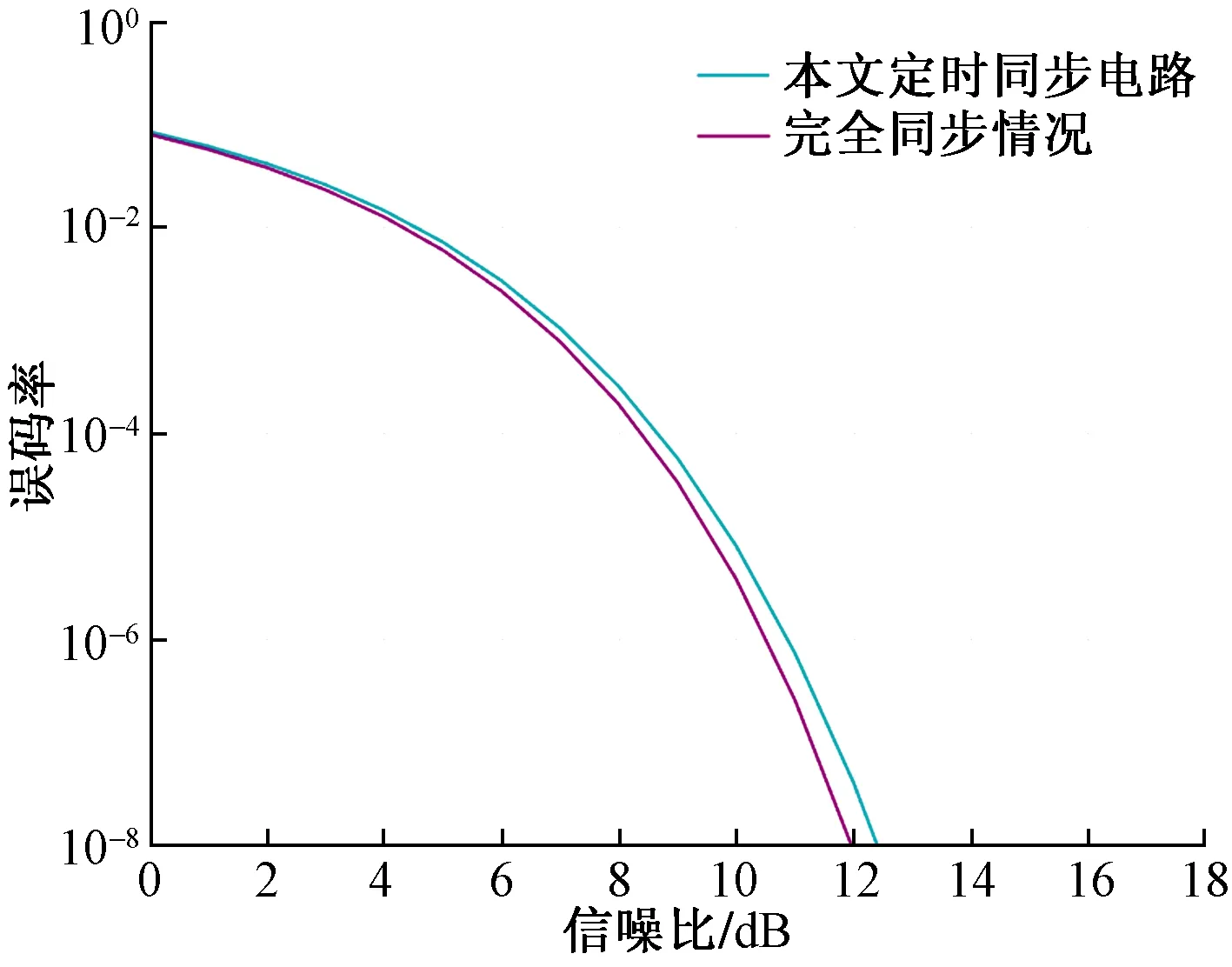

使用MATLAB对整个接收电路建模仿真,处理长度为8 000位的随机数据流。符号速率设置为3.39 Mbps,接收信号信噪比(signal-to-noise ratio, SNR)Eb/N0=30时,定时同步电路各模块输出随r的变化如图4所示,可见采样位置很快稳定在符号中间附近,定时误差e(r)在零值附近小范围波动;完全同步与本设计中的定时电路误码率随信噪比的变化曲线如图5所示,Eb/N0=12时,其误码率(bit error rate, BER)与理想曲线的差值量级在10-7,可见该电路具有较好的定时性能。

图4 定时同步电路模块输出仿真

图5 信噪比-误码率曲线对比

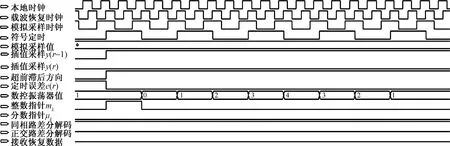

Verilog代码实现该模块,其电路仿真波形如图6所示。

图6 定时同步电路模块仿真波形

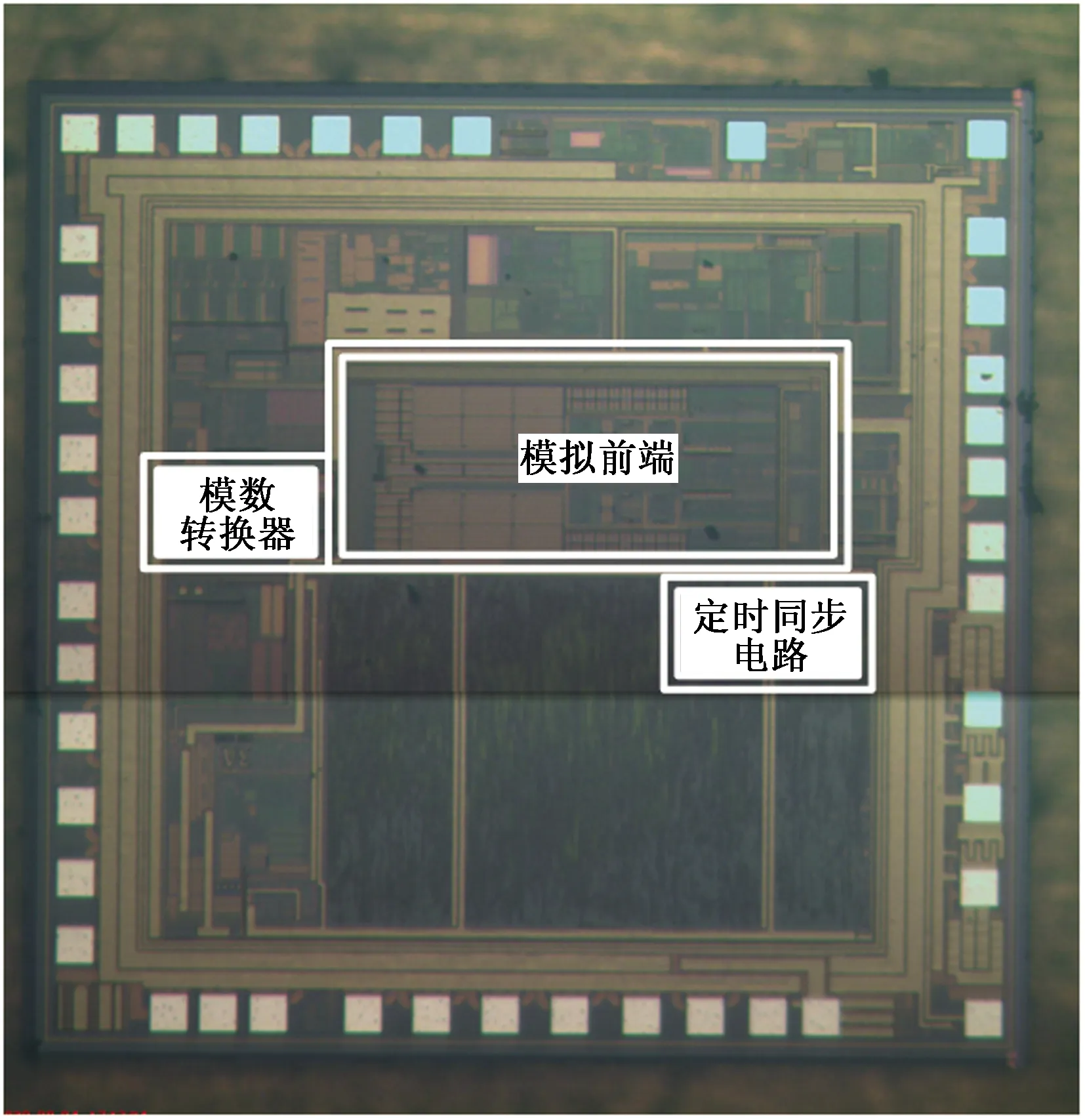

在0.18 μm标准CMOS工艺下流片,芯片照片如图7所示,设计的定时同步电路见其中的定时同步电路模块。

图7 NFC前端芯片照片

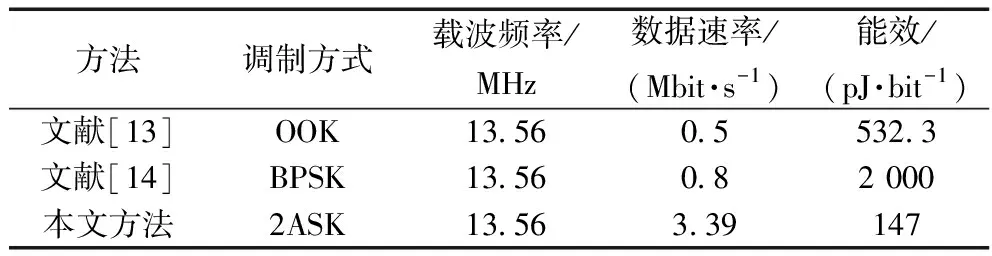

经测试验证,整个接收器正常工作时的功耗约为5.0 mW,与参考文献参数比较如表2所示。

表2 本文与现有参考设计的性能对比

其中开关键控(on-off keying, OOK)、二进制相移键控(binary phase-shift keying, BPSK)均为二进制幅移键控的特殊形式。通过对比可以看出,所提出的新型解调解码电路设计在速率和能效上具有较大的性能提升。

4 结论

提出了一种新型的13.56 MHz PICC解调解码电路设计,接收器由低功耗模拟前端解调2ASK信号,随后由低抖动的数字TRC对信号做定时同步处理,使其能够正确接收106 Kbps至3.39 Mbps的数据。设计最终由0.18 μm CMOS工艺流片实现,经验证符合设计要求,能效低至147 pJ/bit,有一定的能效提升,在大多数的NFC通信场景下均适用。