大功率高性能SiP的电热耦合分析

2021-08-19曾燕萍袁伟星张景辉

张 琦,曾燕萍,袁伟星,张景辉

(中科芯集成电路有限公司,江苏无锡214072)

1 引言

大功率高性能系统级封装(System-in-Package,SiP)具有功能极大化、尺寸微小化、多功能材料和丰富的有源或无源元件等特点。集成在SiP中的组件由于间距不断减小造成热流密度急剧增加,容易产生“热点”问题,对SiP的可靠性产生影响[1-3]。为实现电气互连,需要提高基板走线密度并增加平面、过孔的数量,大量的电流经电源分配网络最终流入各个组件的管脚。流过导体的电流将产生焦耳热从而影响SiP整体的温度分布,与此同时温度分布的改变将影响导体的导电率以及介质的介电常数,可能引发信号完整性问题并且影响到SiP的电压、电流分布。直流压降是电源噪声的一部分,而电源噪声会引起芯片纹波噪声门限和设计裕度降低[4],从而影响器件稳定工作,因此需要综合考虑电和热的相互影响,也就是电热耦合分析。文献[5]对视频处理电路进行电热耦合分析,发现焦耳热会提高器件的最高温度。文献[6]以一款LFBGA芯片为例进行电热耦合分析,以热阻和功率分布为基准来判断计算的收敛性,经多次迭代得到稳定的电热耦合结果。文献[7]对PCB进行电热耦合分析,讨论电路中走线、过孔分布以及焦耳热对温度分布的影响并提出热流控制概念,对PCB各向异性导热率进行优化。

目前,多数电热耦合仿真分析的对象是较为简单的组件,缺乏对大功率高性能SiP的研究分析,并且缺少对供电系统影响的讨论。本文对复杂的大功率高性能SiP进行电热耦合分析,充分对比电热耦合前后的温度分布以及电源压降,为设计出可靠的SiP提供指导。

2 SiP仿真模型

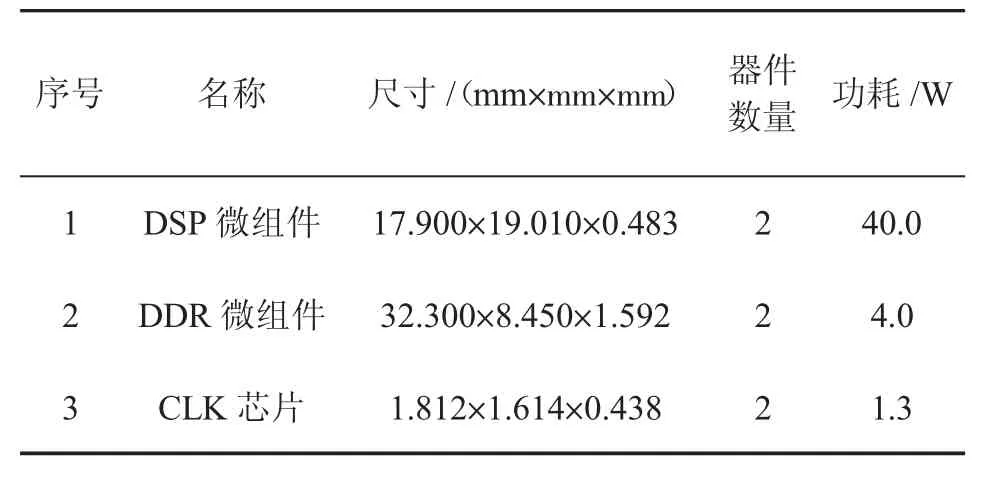

大功率高性能SiP包含DSP微组件、DDR微组件、CLK芯片、电阻电容、焊柱、气密性陶瓷基板以及盖板等,如图1所示。采用建模软件SpaceClaim对SiP进行三维建模,其中DDR单片功耗为0.5 W,每个DDR微组件是由8颗DDR裸片通过TSV堆叠而成。DSP单片功耗为20 W,每2颗DSP裸片通过RDL工艺形成一个DSP微组件。底部CLK单片功耗为1.3 W,SiP整体功耗高达90.6 W,主要的热源尺寸、数量以及功耗如表1所示。

表1 SiP中主要热源的尺寸、数量及功耗

图1 SiP模型示意图

SiP三维模型建立后,经Workbench平台转化至Icepak进行热仿真分析,按照JEDEC的标准设置仿真环境,环境温度设置为25℃。由于SiP整体功耗大,采用微通道冷却方案辅助散热。在仿真计算之前需要保证良好的网格贴体性,图2为仿真模型网格划分图,可以看出网格能够完整地表现SiP模型本身的特征,网格贴体性良好,在基板、芯片等关键组件进行网格加密,从而有效提高计算的收敛性和准确性。

图2 SiP网格划分示意图

3 仿真实验及结果分析

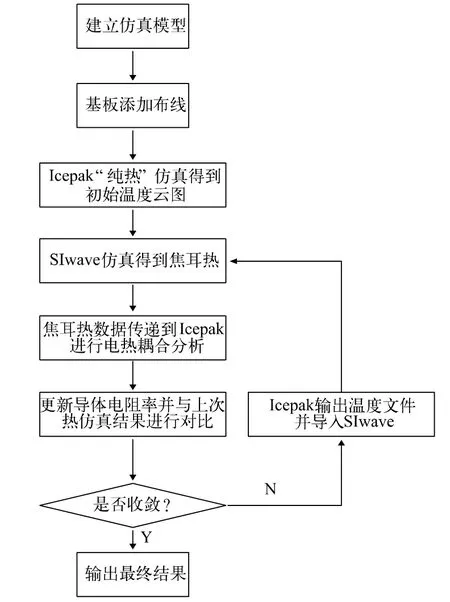

采用软件Icepak和SIwave实现SiP的电热耦合迭代分析,具体的仿真流程如图3所示。

图3 电热耦合仿真流程示意图

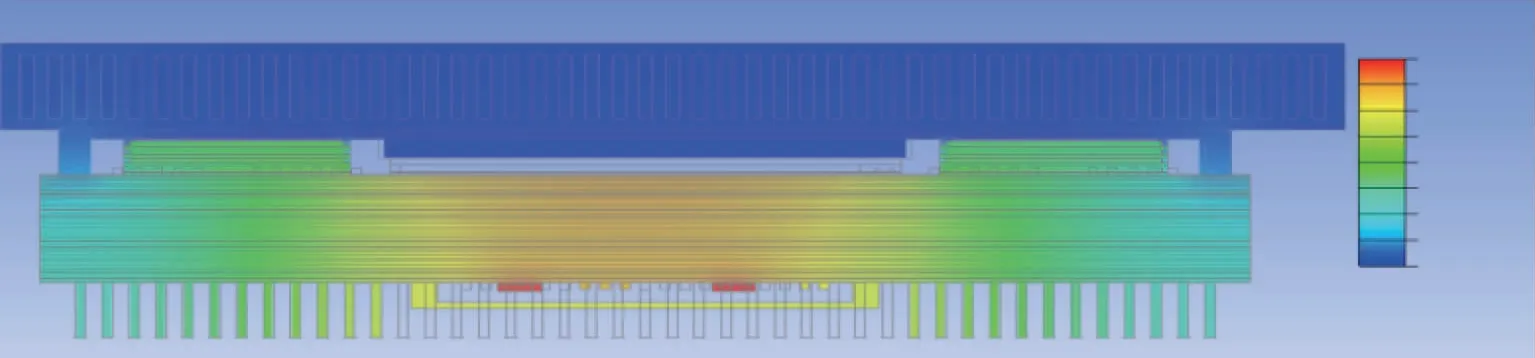

图4 是经Icepak仿真得到的未考虑电热耦合时SiP的温度分布云图,SiP最高温度为109.358℃,且出现在底部CLK芯片上,这是由于基板上表面的芯片产生热量后通过顶层的微通道水冷板迅速散热,底部的CLK芯片不仅受到上表面大功率芯片产热的影响,而且封闭在下盖板内,散热受限因而温度最高。

图4 未考虑电热耦合时的温度分布云图

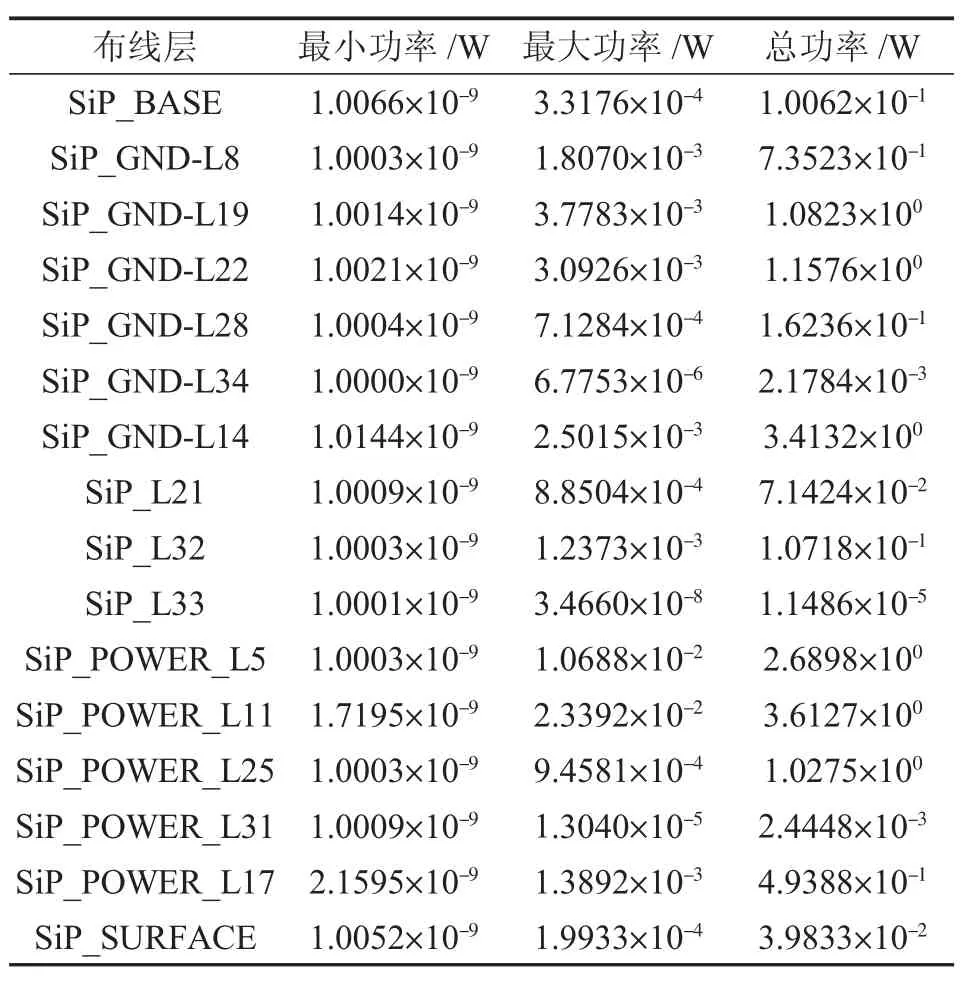

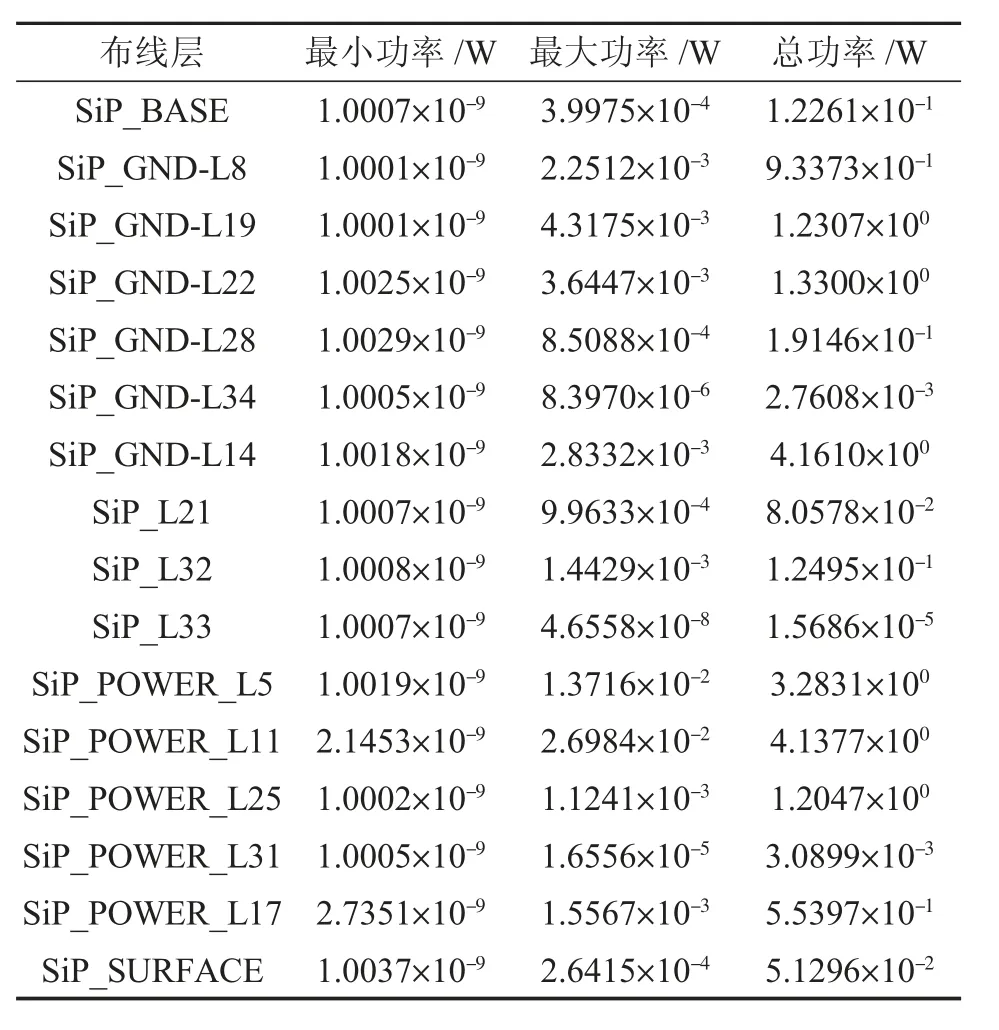

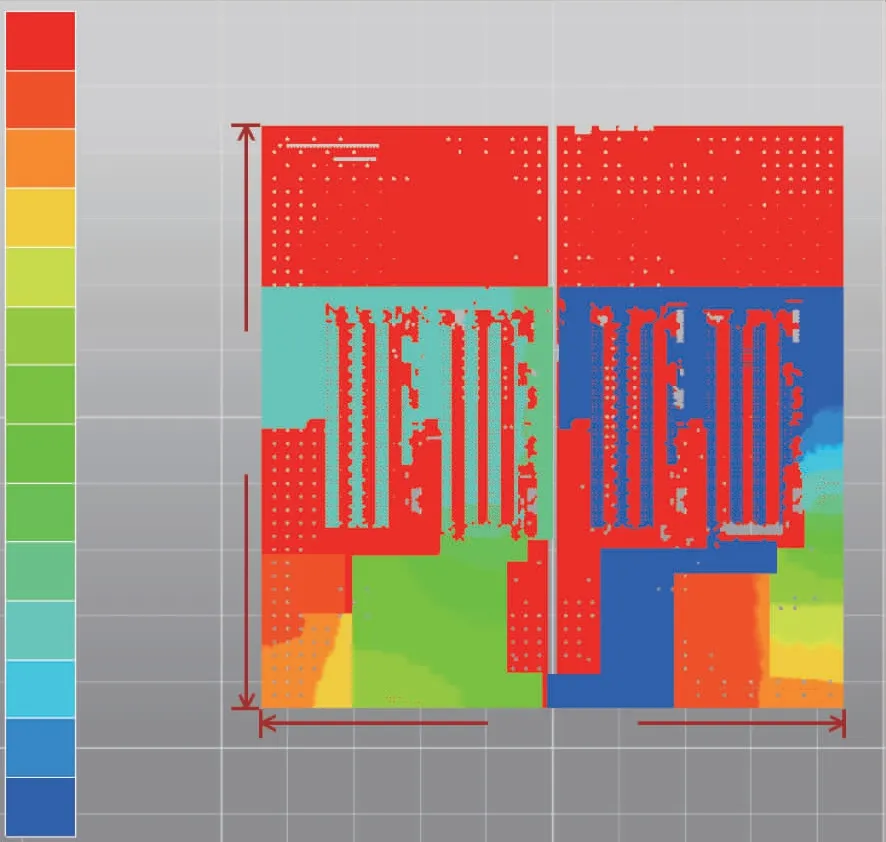

SiP主要的用电组件是DSP芯片以及CLK芯片,故选取的端口包括基板中DSP0_VDD、DSP2_VDD和CLK1_3V3、CLK2_3V3等,基板布线如图5所示。将表2中的电压、电流数据添加到SIwave进行基板的电仿真分析(DC仿真),得到功率分布统计和电压分布图,分别如表3和图6所示。表3中的功率导致基板上布线层产生焦耳热,从图6可知,此时用电端电源引脚处实际电压为0.6729 V。

表2 基板主要的电压、电流数据统计

表3 功率分布统计

图5 基板布线示意图

将SIwave DC仿真结果导入Icepak,进行首次电热耦合分析并得到SiP的温度分布云图,如图7所示。考虑电热耦合之后,SiP最高温度为115.116℃,比未考虑电热耦合的结温增加5.758℃。温度分布和电压分布都未稳定,按照电热耦合的分析流程进行下次迭代分析,最终的功率分布统计和电压分布分别如表4和图8所示。

图7 第一次电热耦合仿真后的温度分布云图

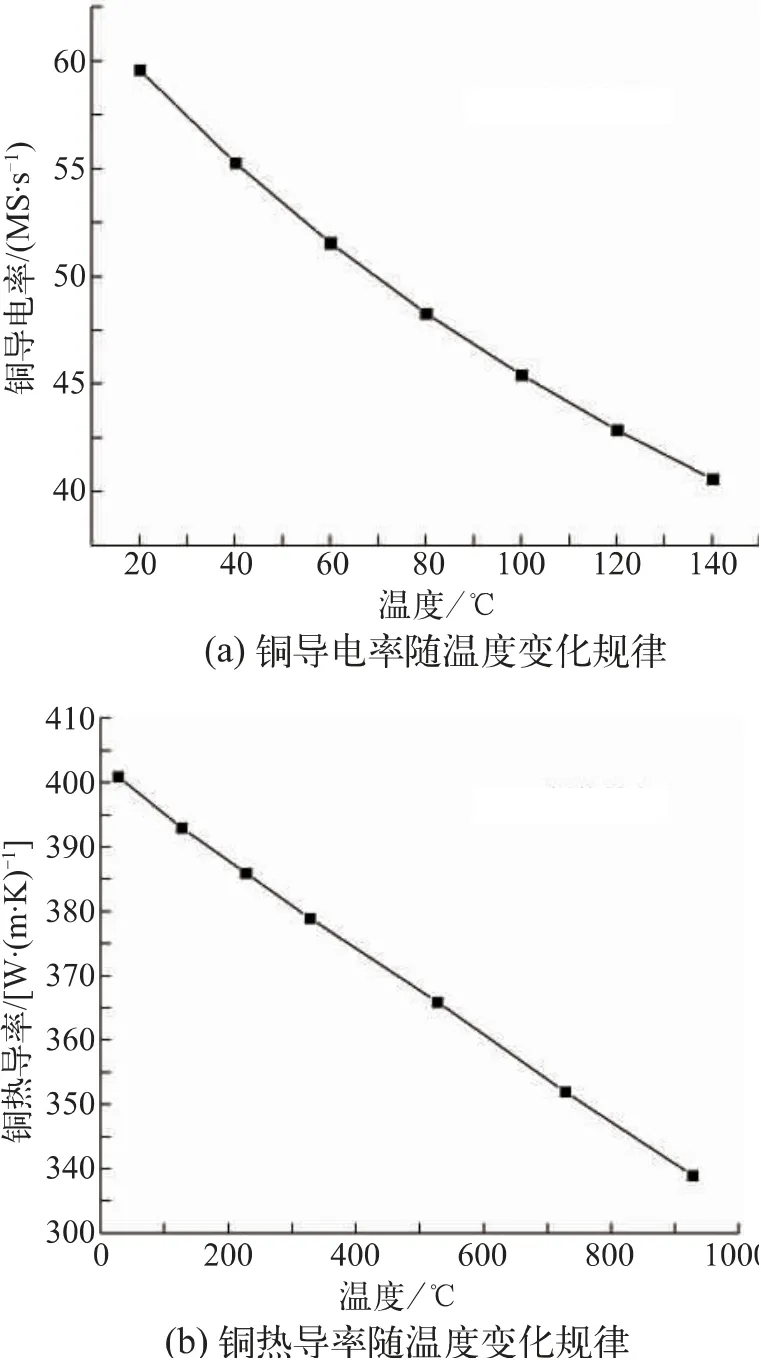

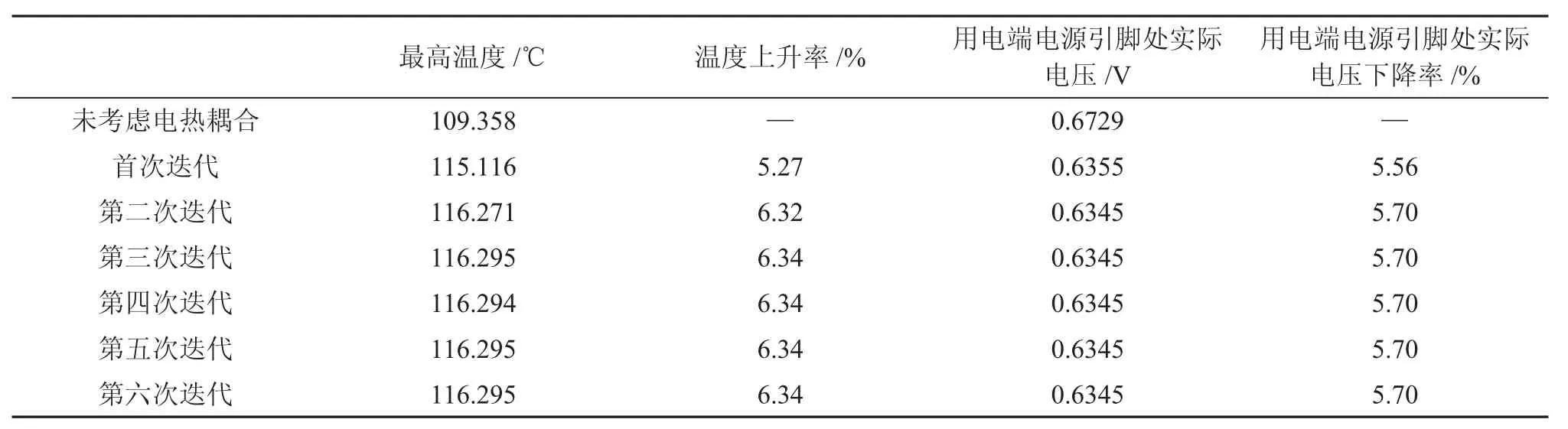

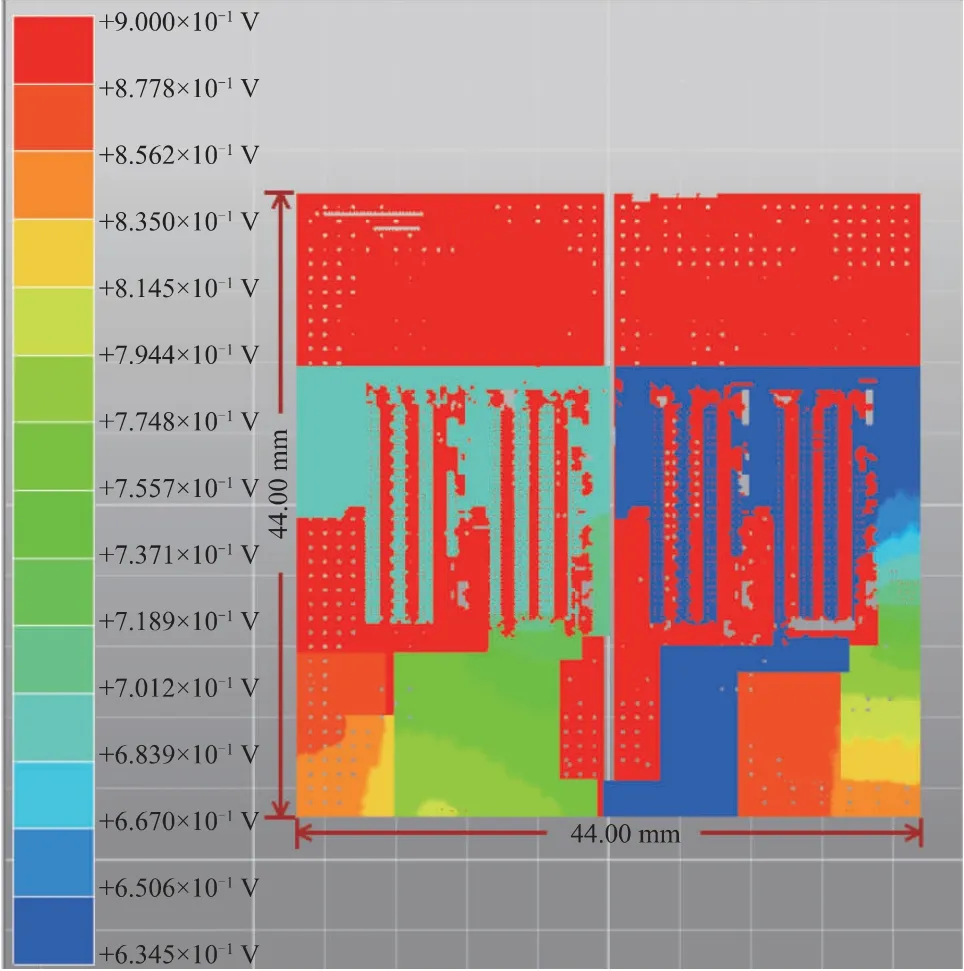

从表4可知,每层铜层上的功率都有所增加,引起焦耳热的增加,继而提高SiP的结温。表5是多次迭代过程中记录的温度和电压数据,与初始结温相比,经6次迭代后最高温度上升6.34%,且计算收敛。由图8可知,迭代后用电端电源引脚处实际电压为0.6345 V,与图6相比减少5.7%。温度的变化会影响导体的导电率,根据文献[7],可知铜的导电率以及热导率随温度的变化曲线如图9所示。从图9可知,随着温度的升高,铜层导电率下降,故铜层导电能力下降,引起更大的直流压降。通常芯片要求的电压变化范围是理想电平的±5%[8],仿真结果表明温度的变化严重影响供电系统的性能。综上,采用电热耦合的方法有效评估了SiP的设计可靠性,为减小用电端电源引脚处实际电压的改变量,可以从降低SiP结温以及优化电源分配网络等角度出发。

图9 铜的导电率以及热导率与温度之间的关系[7]

表5 电热耦合迭代分析的温度、电压数据记录

图8 6次迭代后的电压分布图

表4 6次迭代后的功率统计

图6 电压分布图

4 结论

本文对大功率高性能SiP进行电热耦合分析,充分考虑焦耳热以及铜层导电率等因素的影响,利用软件Icepak和SIwave实现电与热数据的交互。与单一的热分析和电分析相比,考虑电热耦合后SiP结温上升6.34%,用电端电源引脚处实际电压减小5.7%,需采用更先进的散热方案并优化供电系统,以满足SiP的可靠性需求。综上所述,采用电热耦合分析的方法,可以有效评估大功率高性能SiP设计的可靠性。