一种基于扇出晶圆级封装技术的控制模块设计

2021-08-19刘骁知曾小平冉万宁周佳明

刘骁知,曾小平,冉万宁,丁 杰,周佳明

(中科芯集成电路有限公司,江苏无锡214072)

1 引言

随着摩尔定律的放缓,以及先进封装技术和芯片制程技术的不断融合发展,半导体行业逐渐进入后摩尔时代。从最初的单片封装到最先进的晶圆级封装,单颗芯片的集成度不断提高,可实现的功能日趋复杂[1]。伴随着封装技术的进步,系统设计师们对于如何实现特定需求电路的小型化有了更多样的选择。通过选用合理的小型化技术,能有效提高系统集成度、提升系统能力。

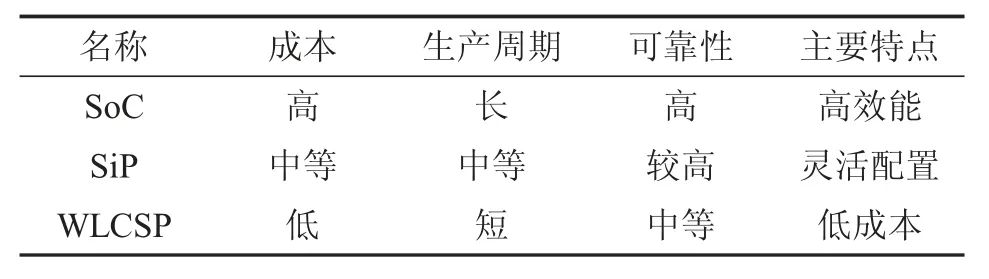

在实现产品小型化的技术中,最常用且具有代表性的有以下3种:SoC(System on Chip)、SiP(System in Package)、WLCSP(Wafer Level Chip Scale Package),各种技术致力于解决用户不同关注点的需求,其主要特点对比如表1所示。

表1 SoC、SiP、WLCSP技术特点对比

因实现成本较高,定制化的SoC在市场中占比相对较低,目前市场上应用较广泛的是SiP与WLCSP技术。WLCSP技术功能指向在更小的封装面积内容纳更多的引脚,SiP技术功能指向整合更多芯片,压缩单芯片体积,提升系统整体功能性和灵活性。SiP技术在很长一段时间内占据主流地位,但随着技术发展,台积电(TSMC)于2016年成功将集成扇出型封装技术InFo(Integrated Fan-Out)应用于苹果iPhone7手机的A7及后续型号处理器(如图1所示为苹果A10处理器的外观及纵向剖面照片),使成本下降了20%~30%,是首个较为成功的WLCSP技术,为RF、电源管理等类型芯片的封装提供了成功解决案例[2]。目前也有研究报告认为台积电的InFo技术既属于WLCSP中的FOWLP(Fan-Out Wafer Level Packaging)技术,也属于多晶片封装的SiP技术,预计2种技术在未来产品中将形成融合趋势[3]。

图1 苹果A10处理器外观及纵向剖面

通过研究国内特定行业已有的成熟案例发现,针对数模混合系统目前较为通用的技术为采用基板或塑封框架SiP封装技术进行小型化设计,FOWLP还未在数模混合系统的小型化工作中得到广泛使用[4-8]。因此,本文基于用户产品的实际需求,使用国内封装工艺,尝试使用FOWLP技术实现一款数模混合控制模块的小型化研制工作。

2 产品架构设计与验证

2.1 产品架构设计

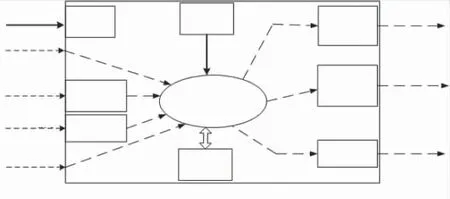

根据用户需求,使用公司自有芯片所搭建控制系统的架构如图2所示。本系统主要实现以下5种功能:

图2 控制系统架构示意图

(1)使用FPGA解析上位机发送RS485及RS422信号,并控制输出接口;

(2)内部具有FLASH及非易失型存储器,用于配置FPGA及储存数据;

(3)具有PLL接口,输出一路本振信号;

(4)具有DDS接口,输出一路中频信号;

(5)具有TTL电平的I/O接口。

2.2 系统验证

在完成芯片选型及架构设计后,首先使用独立封装的分立元器件对系统功能进行验证。在经过充分验证后,最终确定总计8个种类、11片裸片需要进行小型化封装集成,验证板架构及需要封装的器件如图3所示。

图3 验证板示意图

经过验证阶段的工作,梳理出芯片内部共有互联线253条,8种不同规格的电源网络,2种规格的地平面,芯片内部最大信号速率约为200 MHz,裸片到输出管脚的最大信号传输速率为2.1 GHz。按照传统的PCB设计方式,为了保持电源完整性及信号完整性,至少需要6层可布线空间。因此,在进行系统小型化工作时,如何在有限的尺寸内完成互联布线,同时兼顾电源完整性及信号完整性,在工艺实现层面提出了挑战。

3 初样工程实现

3.1 小型化技术路线选择

由于用户对于成本较为敏感,且要求尽快交付验证,同时出于后期量产的考虑,整个加工过程优先选择国内工艺线进行。当工程进入小型化阶段后,通过对比SiP、FOWLP 2种技术路线后可以发现(如表2所示),针对本产品可以选择FOWLP进行尝试。

表2 技术路线对比

3.2 技术路线存在的问题及改进

选定技术路线后,最初目标是将11片裸片通过FOWLP技术封装为1片芯片,芯片尺寸约为30 mm×30 mm×0.7 mm,计划使用极限的4P4M叠层进行布线。但是,通过仿真并结合工程经验分析发现,此方案带来了3个问题。

(1)国内工艺线对于小尺寸芯片FOWLP加工较为成熟,但是对于尺寸不小于15 mm×15 mm的芯片在加工时存在极大的技术难度。原因在于:根据工艺线现状,所加工的FOWLP芯片通常厚度仅为0.5 mm~0.7 mm,因此当芯片尺寸超过15 mm×15 mm时,尺寸越大,由于应力带来的翘曲和弯曲度越难以控制,将会直接影响后期贴装时的可焊接性。

(2)对于尺寸不小于20 mm×20 mm的芯片且使用4P4M叠层时,存在布线层数有限、同时要兼顾电源完整性及信号完整性、精度控制较困难等问题,较大概率会出现过孔定位偏差,极有可能造成地层与电源层短路等问题。

(3)由于单片包含的裸片较多,对于原料裸芯片的晶圆级测试提出了更高要求,以保证产品良率。由于目前未进入量产阶段,使用的原料裸芯片经过中测后,单个理论良率约为90%,则整个芯片封装后理论良率仅为31%(0.9011),不利于试制及量产。

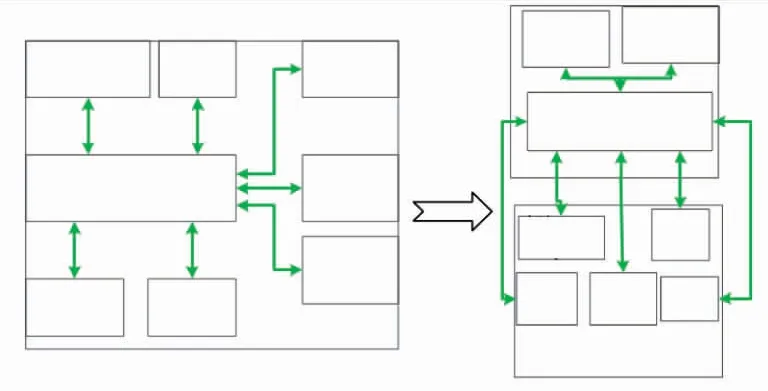

经过综合考虑,参考die-to-die设计思维,结合产线的实际加工能力及经验,按照功能将芯片拆分为2片FOWLP芯片进行试制,#1芯片包括主控单元(FPGA)、配置存储器(PROM)、非易失存储器(EEPROM),其余接口及输出功能的裸芯片封装集成为#2芯片,将单颗芯片内部互联线数量压缩到150条以内,采用4层布线形式,经过仿真可以满足完整性要求,工艺可实现。FOWLP芯片拆分如图4所示。

图4 按功能划分FOWLP芯片

3.3 FOWLP芯片加工过程简述

FOWLP芯片制造流程如图5所示,主要工序有7个。

图5 FOWLP芯片制造流程

(1)模具叠片;

(2)裸芯片粘片;

(3)注塑:将100~500片裸芯片(视大小而定)变为整张圆片形式;

(4)脱模;

(5)绝缘层加工及光刻;

(6)多层再布线和绝缘层加工;

(7)BGA植球及切割。

所有工序完成后即形成单个芯片。

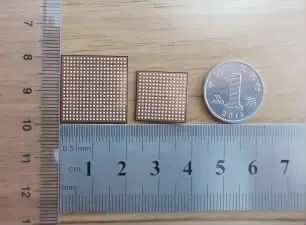

最终形成产品如图6所示,其中#1芯片尺寸为20 mm×20 mm×0.7 mm,#2芯片尺寸为15 mm×15 mm×0.7 mm。2款芯片在加工流程中均较好地控制了翘曲度,可以使用常规贴片机正常贴装到PCB上。

图6 #1、#2 FOWLP芯片实物图

4 测试及分析

4.1 测试

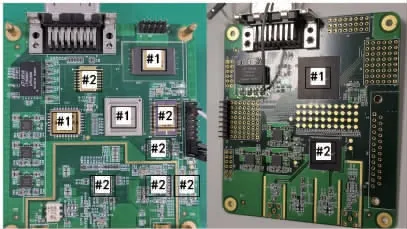

经过一系列小型化工作后,原理验证板与小型化后的实装板对比如图7所示(其中验证板背面芯片未展示),可以根据相同的编号直观看出集成关系。

图7 验证板与芯片测试板对比

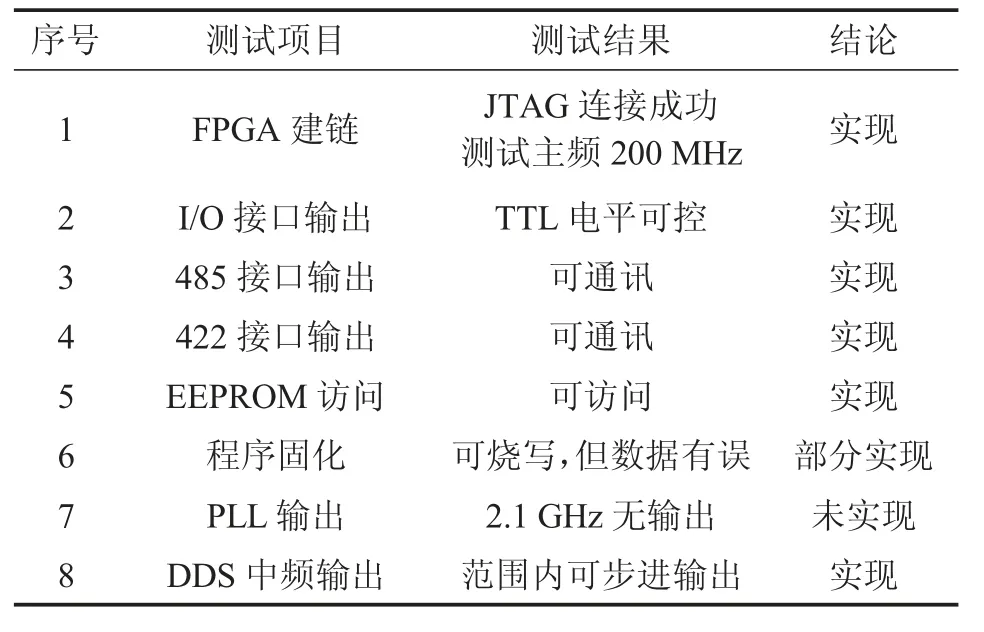

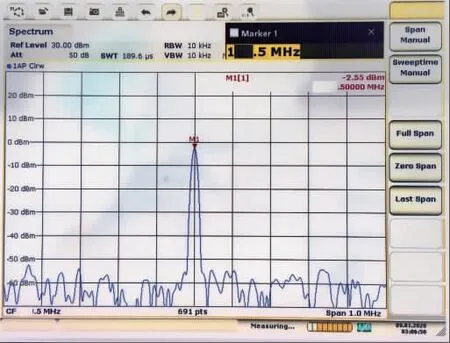

使用ISE14.7顺利通过JTAG与FPGA建立链接,对芯片主要的8项功能进行测试,各项测试结果如表3所示,芯片实现了约80%的预期功能。其中,第8项测试DDS中频信号输出测试如图8所示。

表3 测试项目及符合性对照表

图8 DDS中频信号输出测试

对可能导致此结果的原因分析如下。

(1)测试软件中管脚映射可能存在问题。验证程序工程基于带封装的363引脚FPGA编写,而芯片中使用FPGA裸片共有1700多个管脚,移植代码时,带封装的管脚定义与裸片的管脚编号需要重新映射。根据现有结果分析,功能未实现部分可能是由于映射关系不正确所致。

(2)芯片内部可能存在缺陷。虽仿真可行,但由于内部布线密度高,在芯片加工过程中,内部可能存在互联线定位不准、裸片PAD定位偏移、实物线间距过近产生耦合干扰等情况,导致数据出现误码、裸片互联关系发生错误。

经过对比,总体指标主要在以下几个方面有较显著的提升:

(1)芯片总面积从1204 mm2减小至625 mm2,不计算外围去耦电容也同步减少等的情况下,面积减小约50%。

(2)芯片总质量:11颗芯片总重量从约22.9 g降低至1.41 g,降低约93%。

(3)功耗:系统静态电流由1.1 A降至0.9 A,降低约13%。

4.2 待解决的问题

经过功能测试发现,目前存在的问题及后续需要解决的事项主要有以下几个方面。

(1)需要通过磨片等方式对芯片布线层进行逐层分析,进一步定位问题,排除故障以确保总体功能。

(2)芯片一致性有待提高。由于测试样本较少,尚无法验证发生的现象是否属于共性问题,同时由于暂时不具备对原料裸芯片进行充分晶圆级筛选的条件,芯片成品的良率及一致性存在一定问题。进入量产阶段时,应着重考虑对制造流程及工艺进行完善,提高良率和一致性。

(3)芯片还需解决一体化封装问题。在目前的工作中,重点在于对技术可行性进行验证,而采用了折中实现方案。后续目标为通过三维堆叠技术或采用基板双面贴装等方式,将2颗芯片整合为1颗,目标尺寸控制在25 mm×25 mm以内,便于量产测试及用户使用。

(4)芯片可靠性还可提升。由于芯片厚度较薄,如用于特定用途时还需考虑进行加固,以满足使用环境的力学要求,如可使用双腔陶瓷管壳实现2款FOWLP芯片的一体化集成,以提高芯片环境适应性及可靠性。

5 结束语

本文的研究是基于国内FOWLP工艺线能力的一次有益尝试,文中的芯片级数模混合系统基本实现了预期功能。通过研究与设计,形成了2个基本功能单元,可以用于其他类似的系统或接口单元。

整个研发工作中也存在很多亟待解决的问题。主要是由于FOWLP芯片良率对于封装工艺能力及晶圆级测试能力依赖较大,由于对原料测试覆盖率低,使得本批次芯片良率存在一定问题,后期还需在测试、工艺、版图设计等各环节开展更多的研究工作。同时,芯片初样存在一些功能性故障需要定位,环境适应性等整体指标也有待完善。

本文为其他类似小型化产品设计提供了参考,证明了使用FOWLP技术加工特定用途中小尺寸数模混合芯片的可行性,在特定领域具有较广泛的应用前景。