基于非线性PD 和DAPD 的锁相环频率合成器实现

2021-08-06陶思言

陶思言 ,李 莺

(1.四川轻化工大学 物理与电子工程学院,四川 自贡 643000;2.四川轻化工大学 自动化与信息学院,四川 自贡 643000)

锁相环(Phase-Locked Loop,PLL)电路是一种用途十分广泛的单元电路,主要用于将本地振荡器与独立的输入信号同步,在串行数据链路和射频无线通信中得到了广泛应用[1-5]。

频率合成器作为现代电子系统的一个重要组成部分,是决定系统性能的关键部件。随着现代电子系统的快速发展,对频率合成器的输出频率、输出带宽、频率稳定度、频谱纯度、捷变频速率、频率范围以及输出频率点数量等指标都提出了越来越高的要求;在单片机、可编程门阵列电路、数字信号处理器等数字电路系统中,由频率合成器提供的信号可用作这些电路的同步时钟和系统时钟,在通信电子系统的射频前端电路中,频率合成器产生的信号可作为各种收发射机的基带调制信号和本振(载波)信号,还可完成载波恢复和时钟恢复等功能;在军用通信、雷达等具有抗干扰要求的系统和电子对抗领域,具备捷变频功能的频率合成器是其关键部件;同时,频率合成器还广泛应用于医疗系统如核磁共振波谱仪、广播电视设备、电动调节以及信息网络等领域;因此,频率合成技术成为电子技术研究的热点领域。

关于各类PLL 以及由PLL 实现的频率合成器的研究,已见诸多文献报道[6-11]。文献[6]通过改进鉴频鉴相器(Phase Frequency Detector,PFD)的电路结构,增加一个控制模块自适应调整电荷泵的充放电电流大小,设计了一种可快速锁定的宽频带电荷泵锁相环电路,从而增加环路带宽,减少环路滤波器的电阻值,实现快速锁定并保持环路稳定性不变。文献[7]设计了一种基于自动变模控制的全数字锁相环电路,电路由异或门鉴相器、K 变模可逆计数器、脉冲加减电路以及自动变模控制模块构成。其中自动变模控制模块实时控制可逆计数器的模值,当输入信号和本地参考信号的相位差较大时,降低KMode 值,增大步进校正量,缩短捕获时间;当相位差较小时,增大KMode值,使捕获过程变慢,即延长锁定时间,提高捕获精度。文献[8]提出了一种在全数字锁相环(All-Digital PLL,ADPLL)中实现超高速频率采集的方法。在每次变容器组切换过程中,对鉴相器输出进行调零,为动态环路带宽控制在频率锁定期间增加一个相位误差,实现ADPLL 超高速采集。文献[9]设计了一种基于低压控制器的ADPLL。设计中采用基于控制器的环路拓扑来控制相位和频率,以确保ADPLL 输出信号的可靠处理,采用带Δ-Σ调制器的数字控制振荡器来实现高频率分辨率。文献[10]提出了一种低抖动电荷泵锁相环频率合成器设计方法。该方法采用一种新型自动调节复位脉冲的鉴频鉴相器结构,可以根据压控振荡器反馈频率自动调节不同的脉冲宽度,以适应不同的输出时钟。文献[11]采用改进型宽摆幅低噪声电荷泵结构,结合2 位开关电容阵列技术与RC 低通滤波技术,设计了一种低相位噪声锁相环频率合成器。文献[12]提出,为了优化环路性能,环路带宽应尽可能窄,以使由外部噪声引起的输出相位抖动最小化;为了使由内部振荡器噪声引起的输出抖动最小化,或者为了获得最佳的跟踪和捕获性能,环路带宽应尽可能的宽。显然,这两方面的性能要求是相互对立的,为了解决这个矛盾,可以采用一个辅助鉴别鉴相器(Discriminator-Aided Phase Detector,DAPD)来构成PLL。辅助鉴别鉴相器通路有助于使PLL 快速锁定。一旦PLL 处于锁定状态,就可以维持较好的带宽,同时可把辅助鉴别鉴相器断开。

对此,本文提出了一种新的基于DAPD 实现的频率合成器设计。DAPD 基于非线性鉴相器(Phase Detector,PD)的特性,从而减少捕获时间,提高PLL的开关速度,同时保持相同的噪声带宽和避免调制衰减。实验结果表明,设计的电路能获得预期的理想性能。

1 非线性特性PD 结构及其分析

通常,一个简单的电荷泵PLL 由4 个主要模块构成:PD、电荷泵电路、环路滤波器和压控振荡器(Voltage-Controlled Oscillator,VCO)[13-14]。图1(a)所示为基于电荷泵PLL 的频率合成器的线性模型,其闭环传递函数可以表示为:

在PLL 中,传统的PD 是与电荷泵环路滤波器一起实现的,如图1(b)所示。为了确定PD 的传递函数,假定PD 中的2 个输入信号R和V之间存在一个时间间隔τ,电荷泵电路的输出电流是一个持续时间为τ的脉冲,电荷泵电流的振幅是Ip0。在连续时间近似下,每个输入信号周期T的平均值可以表示为:

图1 线性PLL 频率合成器及其采用电荷泵滤波器的PDFig.1 Linear PLL frequency synthesizer and its PD with charge pump filter

式中:θe=θo-θi。线性PD 的传递函数曲线如图2(a)所示,其中垂直轴表示在输入信号的一个周期期间注入到环路滤波器的电荷;图2(b)所示为一个非线性PD,其特性可以划分为2 个区域[15],锁定区域与线性PD 具有相同的特性,但捕获时间会随着锁定区域以外的陡峭特性而减少。在设计一个非线性PD 锁相环时,首先要确定中心斜率,以满足采用标准PD 的锁相环对噪声和调制的要求。然后,逐渐增加θe=θAD附近的斜率,以提高捕获速度。本文所提出的非线性PD 采用延迟单元和标准的PD 电路来构建,如图2(c)所示。标准PD 是一个数字电路,由输入参考信号R和输出反馈信号V的正边沿触发。考虑到延迟单元具有θAD的延迟,则PD 决定了这两个区域之间的相位差θe的位置。根据θe的值,电荷泵将输出相应的由上行信号或下行信号控制的电流。非线性PD 的行为模型可以用图2(d)的波形来解释。根据两个输入信号Vi和Vo之间的时间差,上行信号U用来增加信号Vo的频率,下行信号D用来减少信号Vo的频率。这样,非线性PD 总是产生正确的信号来均衡两个输入信号的频率作为传统的PD。时间间隔τ为正(负),这时Vi超前(滞后)Vo。当τ大于τAD(τAD=2πθAD)时,UAD可能出现“高电平”;当τ小于-τAD时,DAD可能出现“高电平”。当采用非线性PD 时,在不同的时间间隔τ内会出现2 种情形。

图2 线性PD 和非线性PDFig.2 Linear PD and nonlinear PD

情形1:0<|τ|≤τAD时,注入电荷Q=Ip0·|τ|;

情形2:|τ|>τAD时,Q=Ip0·τAD+(Ip0+IPAD)(|τ|-τAD),当τAD非常小时,可以近似为(Ip0+IPAD)|τ|。

一般来说,具有电荷泵电路和环路滤波器的PD总的传递函数可以表示为[16]:

式中:Ip是电荷泵电路的泵电流;阻抗ZLF(s)是电容CZ和电阻RZ的串联再与一个附加电容CP并联,该滤波器的阻抗为:

式中:τZ=RZCZ;τP=。PLL 的开环增益为:

它有一个交叉频率:

这个PLL 的开环增益可以用式(7)计算:

而且它的相位裕量可以根据式(8)确定:

为了维持相同稳定的环路增益和相位裕量,随着ω增加k倍,即环路带宽增加k倍,则在锁定区外的电荷泵电流变成k2Ip,而不是Ip,环路滤波器电阻会变成RZ/k,而不是RZ。这样可以加快PLL 的开关能力,一旦PLL 锁定在正确的频率,它将返回到低噪声工作。

2 基于DAPD 的频率合成器实现

2.1 结构

所设计的频率合成器是将PFD、DAPD、电荷泵电路、双模预分频器和VCO 集成在一个单一的CMOS芯片上实现,环路滤波器是离片的,结构上类似于一个传统的整数N频率合成器,如图3 所示。通过增加一个倍频器模块(如图3 中倍频器×2),输出频率可达900 MHz(来自于VCO 的450 MHz)。其中非线性PD、电荷泵电路和环路滤波器采用第1 节给出的设计,下面给出各模块的具体设计。

图3 基于DAPD 的频率合成器原理框图Fig.3 DAPD-based block diagram of frequency synthesizer

2.2 采用非线性PD 的DAPD 和电荷泵滤波器

DAPD 的电原理图如图4 中的虚线框所示。DAPD的输出信号FLD依赖于2 个输入信号的相位差是否大于θAD。考虑到延迟单元有τAD的延迟,虽然这个延迟非常小,但不能忽略,DAPD 决定环路滤波器的带宽。当Vi超前Vo时,时间差τ大于τAD,UAD为“低电平”,DAD为“高电平”。否 则,当Vi落后Vo时,τ小于-τAD,UAD为“高电平”,DAD为“低电平”。总之,如果两个输入信号之间的时间差τ的绝对值大于τAD,FLD可能出现“高电平”,而且电荷泵电流变为k2Ip0,环路滤波器的电阻变为RZ/k,即RAD//RZ,直到τ的绝对值在τAD内,而且UAD和DAD都为“高电平”,因此带来FLD为“低电平”,则电荷泵电流和电阻分别返回到Ip0和RZ,得到具有更好噪声抑制且更窄的带宽;然而,延迟单元的采用是根据VCO 的噪声。假设信号Vo的相位特性是θ0±Δθ,θAD应大于Δθ来使DAPD工作。

图4 采用DAPD 和电荷泵滤波器的PD 电原理图Fig.4 Schematic of PD with DAPD and charge-pump filter

在本文的设计中,PLL 的环路带宽ωc大约等于2 π·40krad/s,把环路增益零点ωz=1/τz和极点ωp=1/τp分别放置在ωc以下和ωc以上的4 倍上;另外,采用电荷泵电流Ip0=560 μA,并选择参数k=3。电阻RZ、RAD的值分别为470 和235 Ω,电容CZ、CP的值分别为33 和2.2 nF。

2.3 相位频率检测器

相位频率检测器(Phase Frequency Detector,PFD)用来比较2 个输入信号的相位差。PFD 是一个时序电路,它不仅可以检测相位误差,而且当环路失锁时,还可以提供一个频率敏感的信号来辅助捕获。一些传统的PFD 的缺点是在相位特性存在一个死区,这个死区会在输出信号中产生相位误差。为了解决这个问题,本文采用一种动态的CMOS PFD,如图5(a)所示,它由2 个半透明寄存器[17](如图5(b))和一个NAND 门构成,由输入信号的负边沿触发。PFD 的时序图如图5(c)所示。虽然输入信号是同相的,但由复位通路引起的误差总是存在的。因此,在DAPD 中加入额外的滤波器,以消除误差的影响。

图5 PFD 的实现Fig.5 Implementation of PFD

2.4 双模预分频器

双模预分频器是频率合成器中的高频构建模块,本文的实现电路如图6(a)所示。它基于受控信号模式的逻辑值[18]将VCO 输出信号的频率按32 或33 的因子进行分频,它包括一个同步4/5 分频计数器作为第一级,一个异步8 分频计数器作为第二级。第一级电路为全差分电路,第二级采用单端逻辑电路。为了减少电源噪声,在高速级中采用了类似于射极耦合逻辑(Emitter-Coupled Logic,ECL)的差分逻辑。在4/5 分频电路中,DFF 是一个差动触发器,图6(b)给出了一个差动NAND 门逻辑触发器的电原理图,将逻辑门与触发器合并在一起可以节省功率并提高工作速度。切换触发器是由在差动到单缓冲器后的真正的单相时钟DFF 进行的,缓冲器用于实现在低速级的轨对轨输出信号。

图6 双模预分频器及差动NAND 门触发器Fig.6 The dual-modulus prescaler and the differential NAND-gate flip-flop

2.5 VCO

VCO 是频率合成器中的另一个高频构建模块。一个类似于电流模式差分对的ECL(如图7 中的方框所示)可用来作为一个延迟单元,以获得一个4 级环形振荡器中的高共模抑制。环形振荡器的中心频率的粗调谐是通过偏置Vbpo1实现的(或采用一个数字-模拟转换器),而对于PLL 电压控制通路需要一个微调技术。振荡器需要的增益很容易通过M1 和M2 的比值作为电流增益来决定。本文所提出的延迟单元具有较好的噪声性能,因为电路的工作是通过差分信号来实现的,差分信号不会对电源和衬底注入噪声源;下面另一个偏置电路调节整个范围上的负载对扫描电源电流的响应,它确保延迟单元的输出摆幅保持不变,并取得一个可变的偏置电流以覆盖不同输出频率的合适范围;对于下面的偏置和电压参考电路来说,旁路电容也是一个重要考虑因素。可以采用片上旁路电容器来帮助偏置和电压参考电路降低它们给环形振荡器延迟单元带来的噪声。

图7 压控振荡器的电原理图Fig.7 Schematic of VCO

3 实验结果

采用0.18 μm CMOS 工艺实现了本文提出的频率合成器,图8 所示为所制作的频率合成器的微缩版图。环路滤波器是离片的,VCO 的输出信号连接到源跟随器。在电源电压为3.2 V、参考信号频率为14 MHz 下对频率合成器进行测试。图9 所示为通过改变控制电压所测得的VCO 的传递函数。由图9 可见,VCO 有一个435~485 MHz 的单调频率范围,在460 MHz 中心频率处的增益约为32.4 MHz/V。

图8 所设计频率合成器制作的微缩版图Fig.8 Miniature layout of designed frequency synthesizer

图9 实验测得的压控振荡器传输曲线Fig.9 Experimentally measured VCO transfer curve

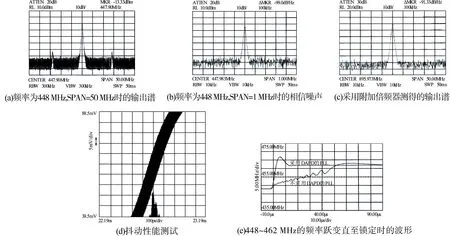

锁定后使用HP8560A 频谱分析仪得到中心频率为448(447.9) MHz 的输出信号的频谱(图10(a))以及在100 kHz 偏移时的相位噪声为-99 dBc/Hz(图10(b));然而,通过增加一个外部倍频器,测得在中心频率为896(895.973) MHz,100 kHz 偏移时的相位噪声为-91.33 dBc/Hz,如图10(c)所示。同时,采用CSA803 通信信号分析仪测得的抖动性能如图10(d)所示,峰-峰值抖动值为110 ps;另一个重要参数是当通道切换时PLL 锁定到一个新频率需要的时间。图10(e)所示为采用HP53310A 调制域分析仪测得的采用DAPD 和不采用DAPD 的PLL 从448 MHz 到462 MHz的频率跳变直至锁定的开关波形。显然,从图10(e)可见,采用DAPD 时明显提高了PLL 的开关速度,最后锁定在462 MHz 时需要的时间要少于不采用DAPD的时间,而且性能也很稳定。

图10 频率合成器的性能测试结果Fig.10 Performance testing results of the designed frequency synthesizer

最后,实测芯片尺寸为30 mm×2 mm,包括焊盘区,功耗为100 mW。

4 结论

本文提出了一种基于非线性PD 构成的DAPD 的PLL 频率合成器设计,并用0.18 μm CMOS 工艺来实现。当在锁相环中加入DAPD 时,它可控制电荷泵和环路滤波器,并维持环路的稳定性,仍然保持和稳定状态时相同的相位裕量,可以用于提高锁相环的开关速度,同时能够有效地保持噪声带宽。采用这种结构实现的原型频率合成器在448 MHz 和在100 kHz 偏移时的输出相位噪声为-99 dBc/Hz。通过增加一个倍频器,频率合成器可以工作在896 MHz,且在100 kHz 偏移时的输出相位噪声为-91 dBc/Hz,峰-峰值抖动为110 ps。所以,从理论设计和实际应用来说,本文提出的基于DAPD 设计的PLL 频率合成器都是可行的。