基于4G通信的车载真彩色LED信息屏控制系统设计

2021-08-04张建军

张建军

(广州通达汽车电气股份有限公司,广东 广州 510700)

0 引言

公交车作为城市重要交通工具,数量庞大,线路繁多,在公交车车尾安装LED信息屏,作为信息发布的平台,可以美化城市市容,做好城市亮化的形象工程。企业商家利用公交车平台做广告,凭借公交具有广播、电视、报纸、杂志都不具备的流动性,其良好的广告传播效果,能让企业及其产品在市场上长期维持品牌形象,提升知名度。

基于4G通信的车载真彩色LED信息屏可以充分展现广告绚丽多彩的视频效果,同时可以通过巴士在线广告发布平台远程发布广告内容,方便运营商灵活的更新广告内容,满足市场灵活多变的广告需求。内置GPS定位模块,实现广告对特定区域的精准投放,取得更好的广告效果。

1 LED信息屏系统的总体设计

LED信息屏系统包括信息发布管理平台和车载LED信息屏。车载LED信息屏由LED显示屏[1]和LED控制器组成,LED显示屏由发光二极管陈列组成;LED控制器负责与信息发布管理平台进行数据通信,接收需要发布的信息内容,同时按照特定要求将信息内容在LED显示屏上展示。

信息发布管理平台包含访问层、应用层、中间层、基础设施层。访问层为用户提供系统访问接入,发布管理平台主要以浏览器方式登录后台管理系统的WEB服务器。应用层为用户提供资源管理、数据统计、GPS定位等服务。中间层提供身份验证、访问控制以及报表、数据挖掘。基础设施层主要包含通信接口服务、协议解析服务、数据库访问和服务定制。

2 LED信息屏控制器的系统设计

2.1 控制器硬件设计

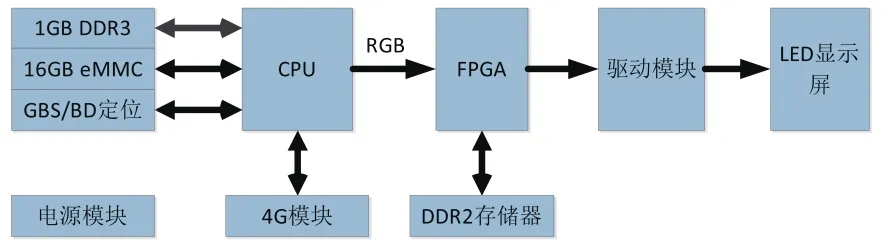

LED信息屏控制器的硬件框图如图1所示,由电源模块、CPU最小系统、4G通信模块、FPGA模块和驱动模块组成。CPU运行嵌入式操作系统Andriod6.0,应用程序通过4G通新模块和信息发布管理平台进行数据通信,接收信息发布管理平台发布的广告内容,将广告内容存储在eMMC存储器中,按照客户要求,在指定的时间和位置将广告内容解码后,通过RGB数据流送到FPGA模块,经过FPGA模块处理后送到驱动模块,最后在LED屏显示。

图1 LED信息屏控制器的硬件框图

2.1.1 电源模块

电源模块采用二级电源转换电路,第一级采用MP9457将24V电源转换12V,第二级电源电路采用RK808、MP2235、TPS51100等多个电源芯片。电源模块还增加共模电感滤波电路、车载TVS保护电路,可以通过车载EMC标准。

2.1.2 CPU最小系统

主控CPU选取瑞芯微RK3368,八核64位A53架构,主频高达1.5GHz。CPU最小系统由RK3368、16GB大小eMMC、512MB大小DDR3、时钟单元、RK808专用电源模块等组成。

2.1.3 4G通信模块

4G通信模块采用龙尚U9300C,工作在LTE-TDD/LTE-FDD/TD-SCDMA/UMTS/EVDO/EDGE/GPRS/GSM/CDMA等多种制式,上下行速率可以达到50Mbps和150Mbps。

2.1.4 FPGA模块

FPGA模块由FPGA芯片和DDR2芯片组成。FGPA芯片采用Xilinx公司的XC6SLX9-2FTG256,具有9000多个逻辑单元、1152KbRAM。

对于企业来说,时间管理是财富之源。时间是一种独特的稀缺资源,它没有弹性,无法再生,更没有替代品。对于企业的管理者来说,他们在面对亟待解决的问题时,需要在有限的时间里,以非凡的统筹能力来合理安排和利用时间,应对企业面临的各种挑战和激烈的市场竞争。

2.2 控制器软件设计

控制器软件主要由广告更新模块和广告播放模块组成。广告更新模块接收平台下发的广告和配置文件,广告播放模块按照特定的规则进行广告播放。

2.2.1 广告更新模块

平台向控制器发送更新广告指令,控制器使用HTTP协议或者FTP协议下载广告媒体文件和配置文件,下载完毕后,使用MD5校验,并判断广告配置文件是否合法,如果广告无异常,则更新广告,并反馈平台更新广告成功。控制器有文件缓存功能,下载文件时,先比对本地是否存在,只有本地不存在的文件,才从平台下载,可以节省流量和减少更新文件时间。

2.2.2 广告播放模块

控制器支持时段独播、按次播放、时段轮播等多种播放规则,播放优先级别为时段独播、按次轮播、时段轮播。

时段独播,在设定的时间段内,单独播放设定的广告,一个时间段内,只能下发一条时段独播广告。后下发的广告会覆盖先下发的广告。

按次轮播在设定的时间段内,根据设定的广告次数,尽可能平均播放下发的广告。一个时段可以下发多条按次轮播广告,终端根据下发的广告进行轮播。在设定的时间段内,根据设定的广告次数,尽可能平均播放下发的广告。

控制器支持广告播放记录,每次播放完毕,会自动将本次播放的素材ID、开始时间、结束时间、播放时长保存到本地,定时上传到后台,平台进行统计分析。

3 LED信息屏控制器的FPGA设计

3.1 真彩色LED显示屏原理

LED显示屏是由许多相同结构的LED模组级联而成,本文选用的模组是16行64列的模组,由16×64个LED点阵组成,每个点由R、G、B三基色组成,每种基色的灰度级等于10bit[2],能显示 10.7G 颜色。公交车上的384×128分辨率[3]显示屏组成如图2所示,总共由48个16×64个LED点阵的模组组成,总共分为8大行,每个大行是级联的,级联顺序按图中模组序号增长顺序。据模组结构可知,LED显示屏采用1/16动态扫描,每2个大行由FPGA内部的一个扫描模块扫描,先扫描16行中第1行,接着扫描第2行,依次扫描到最后一行第16行,一个扫描周期完成。

图2 384X128模组结构

3.2 FPGA总体设计

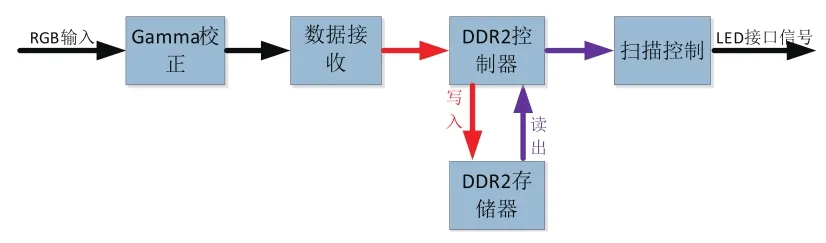

FPGA总体结构如图3所示,主要由Gamma校正、数据接收、DDR2控制器、扫描控制等模块组成。Gamma校正、数据接收、DDR2控制器写入逻辑构成数据输入通道,将主控RK3368送来的RGB数据,按照行同步信号写入FPGA内部的FIFO缓冲区进行缓存,然后按照LED模块结构分模块写入特定的DDR2存储器位置。扫描控制逻辑和DDR2控制器读出逻辑构成数据输出通道,按照扫描顺序和位置从DDR2存储器取出相应数据送到外部驱动模块。DDR2显示存储器采用A、B双显存结构,数据接收模块对A区进行数据写入操作时,扫描控制模块就读B区进行数据显示,反之也一样,可以避免前后2帧数据部分重叠显示在LED显示屏上,影响显示效果。

图3 FPGA结构图

3.3 数据输入通道设计

人眼对外界光源的感光值与输入光强是呈非线性关系的,而是呈指数型关系的,需要将CPU送来的图像进行gamma校正。Gamma校正实际上一系列非线性运算过程,FPGA不能直接按公式计算,一般采取查找表的方式,本文按照Gamma系数2.8生成一个校正表,将该表作为RAM的初始数据。

为提高DDR2的利用率,采用突发模式进行显示数据写如,每次写入数据为256Byte。RGB输入数据按照行、场同步实时刷新,第1行第一个数据写的显存地址0。数据接收通道将RGB数据顺序写入内部的4KByte的fiforam缓冲区,缓冲区内的数据大于256Byte时,触发一次DDR2存储器的写操作。

3.4 数据输出通道设计

由图2可知384X128模组总共只有8大行,每2行用一个扫描模块去控制,总共4个模块即可完成扫描控制,每个扫描模块的DDR2中显存地址不一样,扫描控制逻辑都是一样的。

10位分辨率数据采用“21场原理”[4],即10位数据用21场显示完,每位数据的权重用显示时间长短表示。其中D9位数据表示显示8场,D8位数据表示显示4场,依次递减,D0位数据显示1/64场。每个数据位代表权重值离散的出现在21场中,如D8位在第3、8、13、18场显示,如D2位在第2场显示,如D1位在第10场显示,如D0位在第19场显示,这样可以使得显示亮度均匀,减少闪烁感。

每一场开始前,先将第1行显示数据从外部DDR2存储器读入到FPGA内部的双口RAM,按照当前场序号进行权重标记后,写入到双口RAM,颜色输出模块读取双口RAM中的权重标记输出对应的脉冲时间,控制显示控制信号,完成当前场第1行数据显示。重复上述步骤,直到当前场第16行刷新完毕,当前场所有行刷新完毕,然后进入下一场刷新。

4 结束语

该方案在广州通达汽车电气股份有限公司的320×64真彩色液晶屏上已经批量使用,总共销售上万套,显示效果清晰、不闪烁,完全达到彩色LED的显示效果。