MVB多功能车辆总线仿真与检测系统的设计及应用

2021-07-28王健

王 健

(上海地铁电子科技有限公司 上海 200237)

0 引言

MVB(多功能车辆总线)作为列车通信网络(TCN)的一部分,负责一个车厢内设备或者一个固定的车辆组内设备的数据通信。具有实时性强、可靠性高、传输数据快和传输距离远等优点,目前在高铁和地铁中的应用非常广泛[1]。

为了实现对多功能列车总线的状态监测、故障诊断和一致性测试,以及在车载设备的研发和调试过程中,模拟多功能列车总线的数据传输过程,设计了一套系统,主要实现了以下功能:(1)MVB仿真发送功能;(2)总线波形实时采集功能;(3)数据分析功能;(4)Linux系统下Python控制程序设计。

1 整体设计

在MVB数据通信中,具有以下特征:通信传送方式采用主从帧应答,帧发送方式采用周期性广播,帧标识符具有帧头和帧尾标识以识别帧的开始和结束,帧编码采用曼彻斯特编码,数据传输速率为1.5Mbit/s。为了仿真MVB总线通信,需要仿真主站发送主帧数据,仿真从站发送从帧数据,仿真接收主帧数据和从帧数据。通过对MVB通信总线波形的实时采集,并进行逻辑分析,分析网络中的帧数据、帧响应时间、撞帧、丢帧、位错误及网络干扰等,从而可以实现对网络通信质量的判断和网络设备的一致性测试[2]。在该设计中,利用通用逻辑芯片FPGA实现MVB仿真和波形采集功能;在嵌入式Linux系统下,利用Python编程实现整体控制和数据分析;FPGA和嵌入式系统通过USB实现数据交互,系统结构如图1所示。

图1 系统结构

设计中,仿真功能和采集功能采用Altera公司的FPGA芯片实现;USB模块采用CY7C68013A控制芯片,实现USB2.0/3.0转并行总线的功能;嵌入式Linux系统采用beagleboard-black控制板,该控制板为ARM CortexTM-A8内核,利用其扩展的USB接口,对MVB仿真与采集板进行数据交互和控制;嵌入式Linux系统对外的USB和Internet接口,可实现数据的远程传输及上位机软件的控制。

2 仿真功能设计

仿真功能依托FPGA芯片,实现的逻辑功能包括:帧数据的发送、端口地址的设置、所发送的主帧数据和从帧数据设置、总线数据接收与端口地址比较和发送状态的反馈。仿真功能结构如图2所示。

图2 仿真功能结构

其中,接收模块和发送模块采用VerilogHDL语言设计。仿真发送的主帧和从帧数据以及状态反馈数据,均存储在各自的FIFO存储器内(FPGA内部)。所设置的端口地址,存储在RAM存储器内(FPGA内部)。

仿真功能工作方法如下:(1)接收模块实时检测MVB总线信号,当检测到数据帧起始信号时,向发送模块反馈总线忙,检测到数据帧结束信号后,向发送模块反馈总线空闲;(2)接收模块接收到MVB总线主帧数据时,将接收到的数据与所设置的端口地址进行比较,比较相同时,触发发送模块发送从帧数据;(3)在总线空闲时,发送模块不断检测主帧数据FIFO,当有要发送的主帧数据存在时,发送模块发送主帧数据,发送结束后,向状态反馈FIFO写入主帧发送成功的状态;(4)在发送模块接收到触发发送从帧信号时,读取从帧数据FIFO,若存在从帧数据,发送模块发送该从帧数据,发送结束后,向状态反馈FIFO写入从帧发送成功的状态。

2.1 接收模块

接收模块需要检测MVB总线上的帧起始位、帧结束位和主帧数据,MVB总线数据格式为:起始位+帧头序列+帧数据(包括校验)+结束位,总线传输速率为1.5 Mbit/s,每一位的数据宽度为667 ns,采用曼彻斯特编码方式[3]。

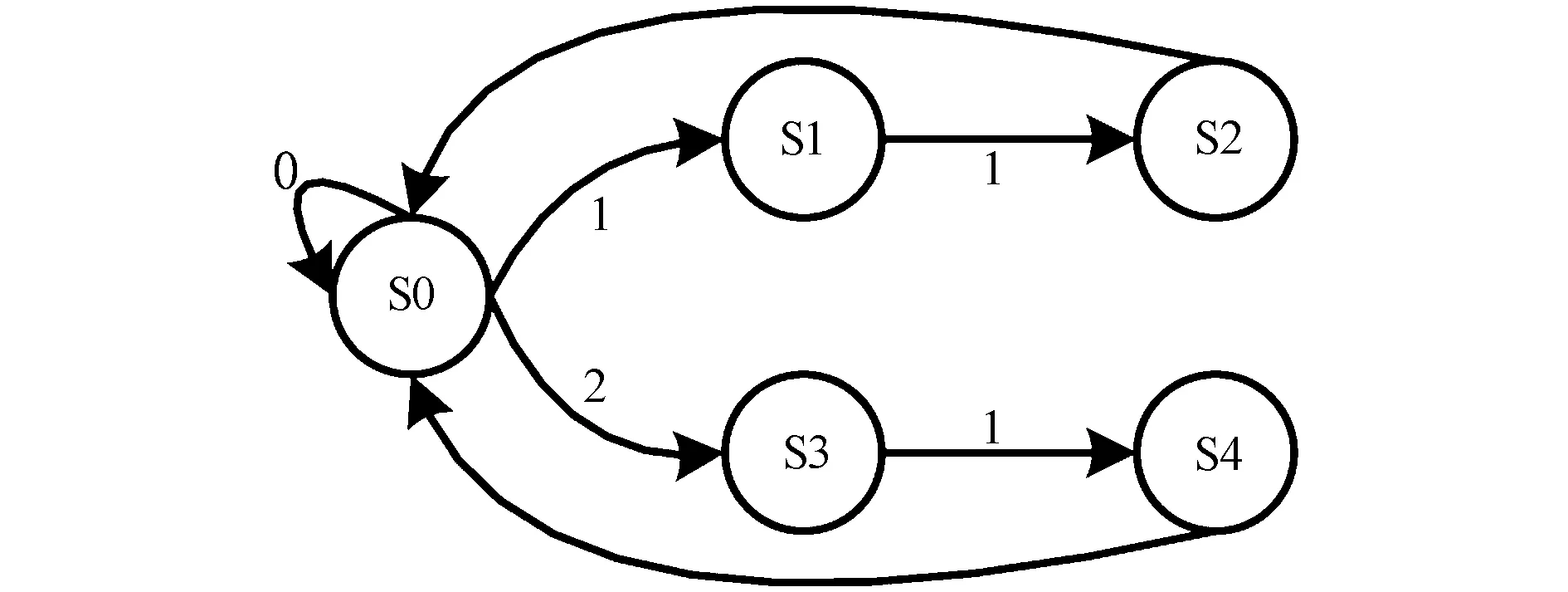

该设计中,MVB网络信号的逻辑采样频率设置为24 MHz,即一位MVB数据宽度为16个周期。将逻辑信号电平及其宽度所占周期数,作为8位分析数据元,数据的最高位为逻辑信号的电平,低7位表示为信号宽度的周期数,将编码信号转换为分析数据元。采用有限状态机方式实现接收模块的功能,其状态转移如图3所示。

图3 接收模块状态转移

S0:接收数据帧起始位,接收到有效的帧起始位后,状态转移至S1,同时总线忙信号有效。接收到有效的帧结束位后,总线空闲信号有效。

S1:接收主帧帧头序列,接收到有效的主帧帧头后,状态转移至S2,否则,状态转移至S0。

S2:接收主帧数据,成功接收主帧数据后,状态转移至S3,若出现数据位错误或数据校验错误,状态转移至S0。

S3:接收帧结束位,接收到有效的帧结束位,状态转移至S4,同时总线空闲信号有效,否则,状态转移至S4。

S4:比较接收到的主帧数据与设置的端口地址数据,相同则触发发送从帧数据信号,状态转回S0。

2.2 发送模块

发送功能实现的方式如下:将8位数据,从最高位到最低位移位输出,移位频率为3 MHz。对待发送的帧数据(字节为单位),进行编码转换[4]。采用有限状态机方式实现发送模块的功能,其状态转移如图4所示。

图4 发送模块状态转移

S0:发送模块在MVB总线空闲时,检测主帧FIFO,检测到有效的主帧数据后,状态转入S1;在发送从帧信号有效的状态下,检测从帧FIFO,检测到有效的从帧数据后,状态转入S3。

S1:读取主帧FIFO数据并发送,结束后,转入状态S2。

S2:向状态反馈FIFO写入主帧发送成功的状态,状态转回S0。

S3:读取从帧FIFO数据并发送,结束后,转入状态S4。

S4:向状态反馈FIFO写入从帧发送成功的状态,状态转回S0。

3 采集功能设计

采集功能由FPGA芯片实现,对MVB网络通信波形进行数据采集,采样频率为24 MHz,采样的数据以字节为单位,数据的最高位为逻辑信号的电平,低7位表示为信号宽度的周期数,采集功能结构如图5所示。

图5 采集功能结构

采集功能工作方法如下:(1)系统工作频率为48 MHz,采样频率是24 MHz。在每个采样周期,对MVB网络波形进行逻辑采样;(2)当逻辑电平变化时,记录前一电平状态及所持续的周期数,形成一个字节的采样数据。同时清零计数,开始新的计数周期;(3)当电平周期数达到0x7F时,记录电平状态及周期数,形成一个字节的采样数据。同时清零计数,开始新的计数周期;(4)网络采样数据按照先入先出的原则,存入数据存储FIFO。

4 系统控制设计

系统控制是在嵌入式Linux系统中,利用Python语言编程实现。系统控制主要完成的功能如下:仿真设置设备端口地址、仿真设置发送主帧数据、仿真设置发送从帧数据、仿真帧数据发送次数设置、采集网络数据分析、采集网络帧数据提取、采集网络质量分析和系统工作状态监测[5]。

4.1 仿真控制程序设计

系统程序通过将仿真设备端口地址数据写入端口地址RAM,实现设置端口地址功能;通过将仿真发送主帧数据写入主帧数据FIFO,实现发送主帧功能;通过将仿真发送从帧数据写入从帧数据FIFO,实现发送从帧功能;通过读取状态FIFO数据,实现仿真帧数据发送次数控制[6]。

4.2 采集分析程序设计

系统程序通过读取采集数据存储FIFO内的波形数据,可分析网络帧数据、帧响应时间、撞帧、杂波、丢帧、数据位错误和帧校验错误等,从而可实现对网络质量的判断。数据分析采用有限状态机方式实现。

5 试验与应用

5.1 仿真功能逻辑设计试验结果

采集功能采用Altera公司的FPGA芯片实现,为了验证该功能,利用QuartusII的仿真软件,模拟发送主帧数据,触发发送从帧数据,仿真结果如图6所示。该结果图为采集功能所采集到的帧数据波形,第一帧数据为发送的主帧数据;第二帧数据为接收到主帧数据后,触发发送的从帧数据。

图6 发送主从帧数据仿真波形

实际调试试验利用开发的上位机软件,设置发送主帧数据设备端口号和从帧数据,仿真发送主帧数据,设备端口号与接收到的主帧数据中端口号相同时,触发发送从帧数据。

5.2 实际应用

利用仿真功能,对上海地铁4号线VCU控制器进行了离线测试,模拟发送主帧数据功能,对所有地址进行扫描,成功扫描到VCU系统设备地址,并可读取其设备状态。

仿真设备通过MVB通信线与VCU设备连接,上位机软件控制发送主帧数据,同时,记录通信总线数据。对所有端口地址扫描后,分析系统记录的总线数据,可得到VCU设备地址及其反馈的状态数据。

6 结束语

MVB网络在高铁和地铁车辆控制领域应用得非常广泛,本文所设计的仿真与检测系统,为MVB网络调试、网络设备检测和维修、网络设备一致性测试和网络质量的判断,提供了一种智能的方法。同时,为网络协议分析和设备开发提供了手段,也为MVB网络应用的推广提供了参考。