满足TDRSS测控需求的箭载中继终端小型化设计

2021-07-27廖彦杰叶琪玮周林

廖彦杰,叶琪玮,周林

(中国西南电子技术研究所,四川省 成都 610036)

关键字:TDRSS;箭载中继终端;小型化;芯片;自主可控

0 引言

跟踪与数据中继卫星系统TDRSS是利用同步卫星和地面终端站,对中、低轨飞行器进行高覆盖率测控和数据中继的测控通信系统,它具有跟踪和测轨和数据中继两个功能,是一种先进的天基测控系统。基于中继卫星系统的天基测控技术为新型运载火箭的遥测遥控和数据通信提供了先进技术途径,不仅从根本上解决了地基、海基测控通信覆盖率低的问题,还解决了高速测控通信等技术难题[1]。

通常情况下,箭载中继终端应具备接收火箭遥测数据,并对数据进行成帧、编码、调制、变频输出;能根据火箭姿态、位置信息,结合中继卫星经、纬、高等信息计算出相控阵天线的波束指向角;同时能对前向控制命令进行变频输入、解调、解析等功能。

自2012年9月,箭载中继终端成功运用于长征三号甲系列运载火箭实现首飞以来[2],运载火箭配备箭载中继终端进行天基测控已经常态化。新一代的火箭测量系统在体积,功耗,可靠性,性能上都提出了新的需求,基于目前传统的箭载中继终端的解决方案,难以满足在低功耗、小体积、高稳定性和灵活的开发模式等方面的需求。

因此,如何实现箭载中继终端的小型化、低功耗是目前亟待解决的关键技术,并且这也是我们为之不懈努力的奋斗目标。

1 传统箭载中继终端的设计架构

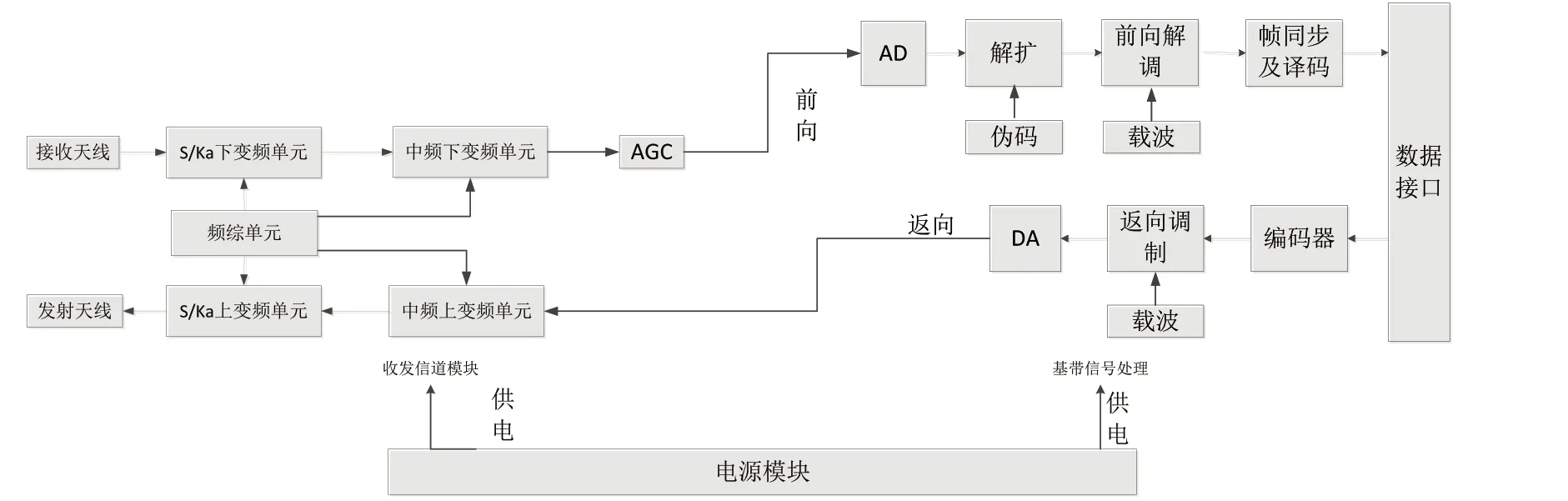

如图1所示,传统的中继终端一般由三部分组成:电源模块、收发信道和基带信号处理三个部分组成。电源模块的功能是为中继终端提供各模块所需的、稳定的二次电压,并且满足相关电磁兼容规范的要求。

图1 传统箭载中继终端组成架构图

收发信道模块共包含S/Ka上下变频单元、中频上下变频单元、频综单元和AGC。S/Ka下变频单元主要实现射频输入信号的放大、滤波和变频至L频段的功能;S/Ka上变频单元主要实现L频段的信号到S/Ka频段的上变频及S/Ka频段信号的放大、滤波功能;中频上下变频单元主要实现基带输入的中频信号到L频段的变频功能及S/Ka下变频单元输出的L频段信号到中频信号的变频功能;频综主要输出接收信道和发射信道所需的本振信号。AGC的作用是保证输出电平的稳定。

基带信号处理模块完成基带信号的数字化处理,即完成前向遥控指令信号的接收,解调和译码,输出指令信号给执行控制单元;同时将状态信息以及遥测等返向数据编码、调制到中频载波上[3]。同时具备各个数据接口功能。

2 小型化设计思路

随着我国集成电路技术产业链的发展,工艺的提高,为实现高性能的专用通信芯片解决方案提供了可能。

传统的箭载中继终端构成主要包括了由微波器件组成的模拟电路和以FPGA为架构的大规模数字电路。目前微波器件的制造工艺主要分为以 CMOS 或锗硅(SiGe)为代表的硅基半导体工艺和以砷化镓(GaAs)或氮化镓(GaN)为代表的 III-V 族化合物半导体工艺两大类。砷化镓(或氮化镓)工艺器件的优势在于可以获得较大的输出功率和较低的噪声特性,但其缺点是集成度低、成本高、无法集成大规模数字电路、工艺一致性较差。CMOS工艺,虽然在最大输出功率和噪声性能方面逊于 GaAs 工艺,但具有集成度高、功耗低、成本低等优势,已成为制备大规模集成电路的主流工艺技术[4-5]。基于 CMOS 工艺的高集成度片上系统(SOC)可以在同一芯片上集成模拟电路、数字电路和射频电路等具有不同功能的模块,已广泛应用于无线移动通信、光纤通信、数字信号处理、数据存储等军用和民用领域[6]。随着 CMOS 工艺的发展,器件特征尺寸的减小使得器件工作频率不断提高,使其在微波电路制造上的应用逐渐成熟,采用基于 CMOS 工艺的集成芯片化设计方法是实现箭载中继终端小型化的有效技术途径。

因此,本文针对箭载中继终端的收发信道和基带信号处理模块,通过设计专用芯片,将上变频信道、下变频信道以及基带信号处理分别进行单片集成,最终达到小型化的设计目标。

3 小型化设计

3.1 架构设计

小型化的箭载中继终端架构如图2所示。其核心架构依托于上变频信道集成芯片、下变频信道集成芯片及基带芯片,再加上给芯片提供所需电源的电源模块和简单的外围及接口电路,就能实现传统箭载中继终端的所有功能。

图2 小型化箭载中继终端组成

3.2 上变频信道芯片

上变频信道芯片基于CMOS集成工艺,设计上采用两次上变频结构,将中频输入信号与 L 频段和 S/Ka 频段的本振信号进行两次上变频,至射频发射频率,再经过射频放大器放大后输出至芯片外,为实现更高的系统集成度,将本振信号产生电路、变频器、滤波器等模块全部实现单芯片集成。

按此原理架构通过合理的设计、布局,从模块到通道、再到芯片的过程逐级完成。流片后的上变频信道芯片尺寸为3.2mm×2.1mm,芯片功耗0.3W。

3.3 下变频信道芯片

下变频信道同样基于 CMOS 集成工艺,采用两次下变频结构,将接收射频信号与 S/Ka 频段和L 频段的本振信号进行两次下变频,至中频输出频率。为适应接收信号的输入动态范围,下变频信道芯片将集成自动增益控制放大器以保证输出电平的稳定,降低基带芯片的动态适应要求和设计难度。

同样,按此原理架构通过合理的设计、布局,从模块到通道、再到芯片的过程逐级完成。流片后的下变频信道芯片尺寸为5.2mm×4.4mm,芯片功耗0.22W/通道,AGC动态范围优于25db,可开环工作,开环增益可通过控制接口进行外部控制。

上下芯片由于模数混合,对供电比较敏感,所以供电必须经过DC/DC和LDO后再提供给芯片,以保证芯片工作的稳定,不恶化相噪等重要指标。

3.4 专用通信基带芯片

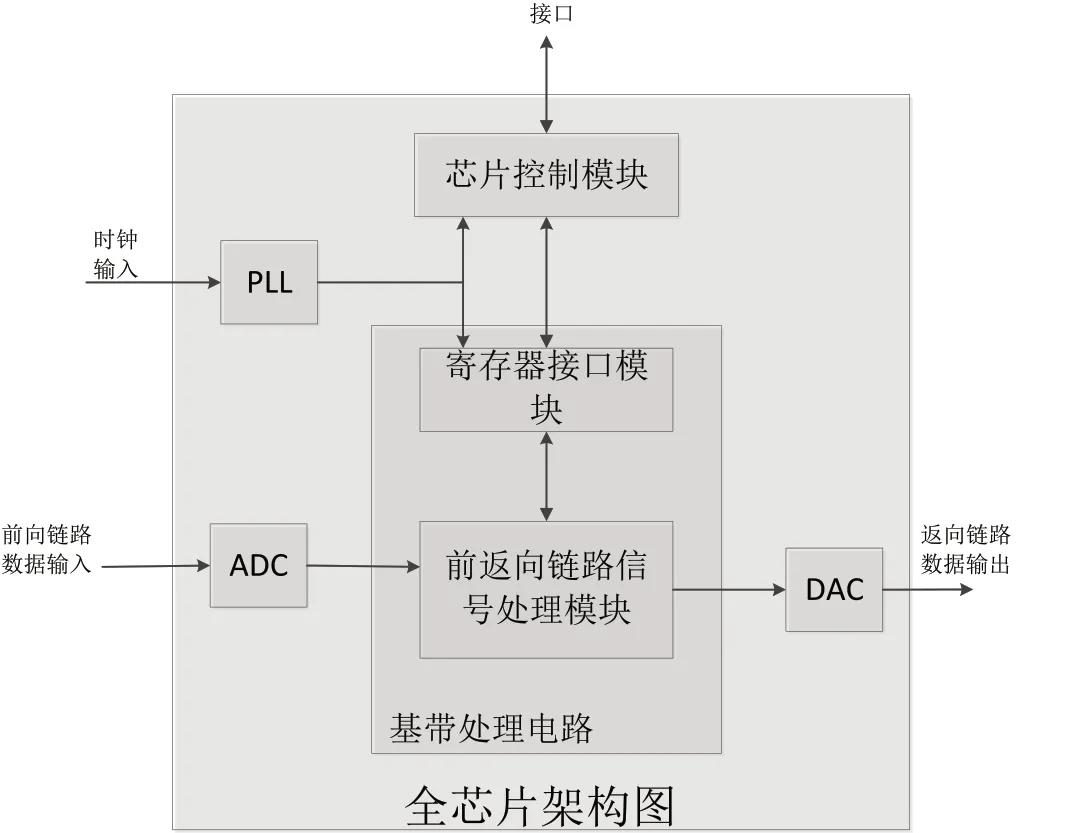

专用通信基带芯片在设计上,首先考虑到调制/解调、编译码、快捕、等前返向链路信号处理相关功能,传统的都是基于FPGA平台的软件无线电算法实现。因此,对于该部分算法对应的可编程逻辑电路进行流片,为了保证芯片工作的稳定性,以及降低流片难度,将基带处理中数字部分和模拟部分分开处理,数字部分(数据的组帧、编译码、调制解调模块等)采用COMS工艺进行单独流片,模拟部分(AD,DA)采用成熟的商业化产品,最后进行SIP封装,集成为一颗芯片,架构如图3所示。同时,在芯片的设计过程中,不仅考虑了低功耗、低成本和高稳定性要求的芯片架构设计;还要兼顾数字模拟电路高度集成在一个芯片上,数模信号、时钟信号及芯片内部之间的抗干扰设计;再者还要满足协议演进和功能增强对芯片设计灵活性的要求。

图3 专用基带芯片架构框图

如图5所示,专用基带芯片在架构上主要分为两大功能模块,芯片控制模块和前返向链路信号信号处理模块。

为了动态配置前返向链路参数,在芯片中集成了ARM处理器。根据上位机提供的系数或者存储在NAND FLASH里的参数,经过一定算法处理,得到前向链路以及返向链路的参数配置,并通过APB总线配置到相应的寄存器;其次每隔一段时间,如1秒,读取前向链路和返向链路的寄存器值,并可以通过UART串口发送给上位机。芯片控制模块的接口具有丰富的扩展性,支持UART,SPI以及GPIO接口,既满足了芯片的当前的要求,也为将来的扩展预留了接口。

专用基带芯片的核心是其软件算法,不仅要实现基带信号处理的各种功能,同时仅通过外部参数配置就能适应中继传输规范的不同的工作模式。所以在流片前需对基于FPGA平台的软件算法进行全方位的测试和验证。流片后的专用基带芯片尺寸为30mm×30mm,功耗小于3W。

4 小型化成果

采用本文所述方法设计出的小型化箭载中继终端,整机体积110mm×60mm×40mm,重量520g,功耗9.6W。同时具备S和Ka信道,且扩频码速率、数据码型、编码和调制方式等内容可配置,根据任务需求进行灵活选择。

图4 小型化中继终端实物图

5 结论

本文给出了一种基于专用芯片的小型化箭载中继终端的设计方法,在芯片的设计上,充分考虑了芯片的高集成度、低功耗、高性能、抗干扰、低成本、合理散热等内容,使得小型化箭载中继终端在体积、重量、功耗上比传统的小了百分之89%,74%,49%。并且专用基带芯片能摆脱对国外FPGA的依赖,实现自主可控,具有很高的战略意义。该小型化箭载中继终端可通过软件重构配置、能适应中继卫星传输规范的所有应用模式,因此具有非常广泛的应用前景和非常高的工程应用价值。