单元数字化收发SIP的研究

2021-07-17陈利杰

唐 亮,陈利杰

(中国电子科技集团公司第三十八研究所,安徽 合肥 230088)

0 引 言

随着相控阵雷达的发展,射频与微波收发模块经历了从分立多通道模块到多通道模拟阵列模块以及现在多通道数字阵列模块的发展历程。未来高性能相控阵雷达的发展也对数字阵列模块提出了更高的要求,而系统级封装集成技术的发展使其实现成为可能[1,2]。半导体技术的快速发展推动了微波系统集成技术在军事和民用领域的快速发展。在物理尺寸方面,具备独立能力的微波芯片体积向纳米量级发展;在功能方面,实现在有限条件下芯片和系统能力的最大化。单元数字化收发SIP是应用先进的系统级封装技术,集模拟、数字以及高速传输的多功能芯片等器件,将接收支路和发射支路有机结合起来的核心模组[3]。

本文介绍了一种S频段单元数字化收发SIP模块的研制,SIP使用器件包括CMOS、GaAs、GaN以及MEMS等。通过单元数字化架构设计、AlN基板一体化设计、腔体架构和器件布局,实现了SIP的小型化并达到了优异的指标。

1 SIP设计

1.1 总体设计

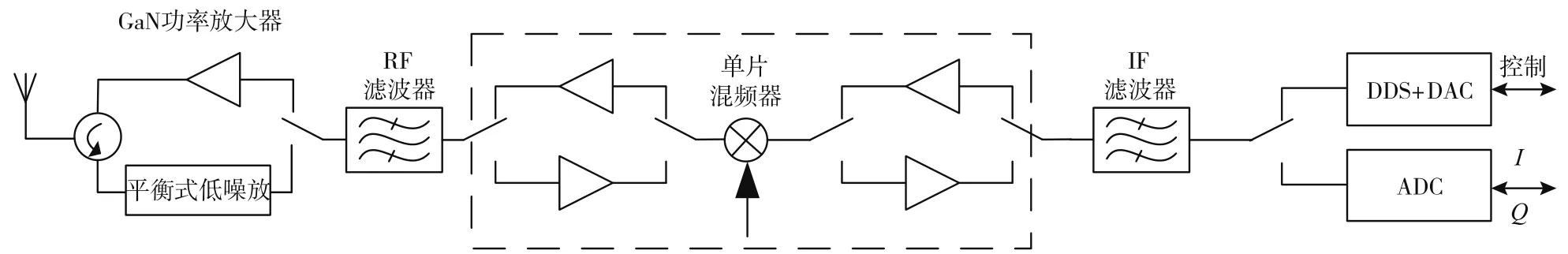

单元数字化收发SIP功能包括低噪声放大、功率放大、上下变频、高速采集、波形产生以及调制电源等,实现框图如图1所示。收发之间采用环行器,在接收支路采用平衡式低噪放,天线端的反射信号被平衡式低噪放中电桥的负载吸收,从而保证了收发状态良好的驻波匹配[4]。

图1 数字化收发单元实现框图

单元数字化收发SIP集成度高,电磁兼容性复杂,采用了新材料和新工艺,这些应用都提高了数字收发单元设计、制造及工艺装配的难度。SIP通过MCM高密度微组装工艺,集成低噪声放大、GaN功率放大、变频以及调制电源等芯片,实现模拟射频前端的功能,同时搭载了高速ADC、DDS及电源等元件,实现了单通道数字高速采集和波形产生等功能[5]。

1.2 接收支路设计

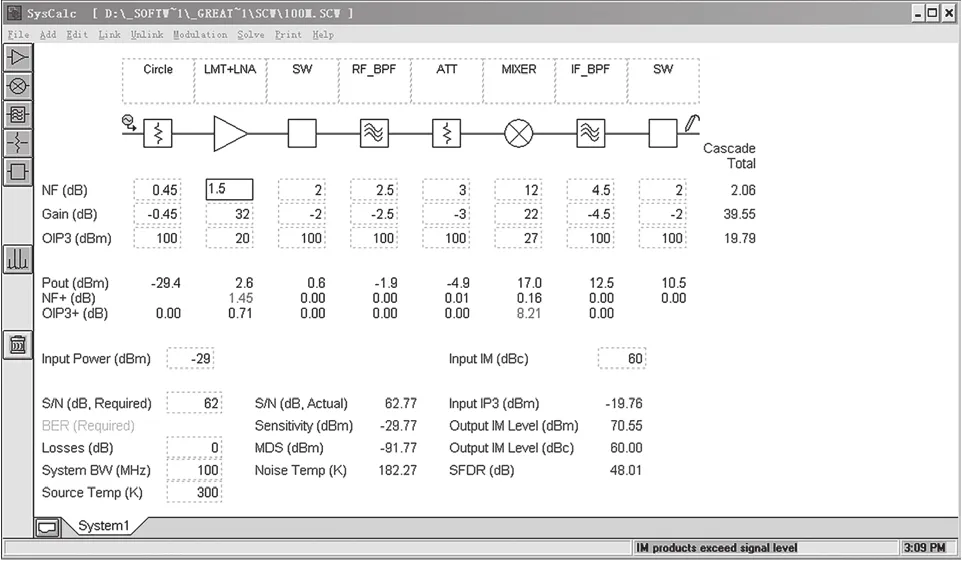

SIP接收支路主要完成信号的低噪声放大,并对射频工作频带外信号进行滤波,经过频谱搬移后,对中频信号进行模数转换,完成信号采集,送FPGA进行处理。对接收支路具体增益分配如图2所示,可计算出接收模拟前端的噪声系数NF=2.06 dB

图2 接收支路指标分配

综合考虑ADC对接收机噪声系数的影响,将ADC看成是一个附加噪声源,通过计算出接收模拟前端与ADC的组合噪声系数,根据组合噪声系数的变化来衡量ADC量化噪声对灵敏度的影响[6]。由经典的噪声系数定义,可推导出系统组合噪声系数为:

式中,M为接收机的输出噪声功率与ADC的量化噪声功率的比值,NF为接收机自身的噪声系数。由式(1)可知,M值越大,ADC的量化噪声对接收机与ADC组合后的总噪声系数的影响就越小。SIP集成14位ADC,其典型满刻度输入信号电平VFS是2VP-P(600 Ω阻抗),SNR为69 dB,求得M为67.4。

1.3 发射通道设计

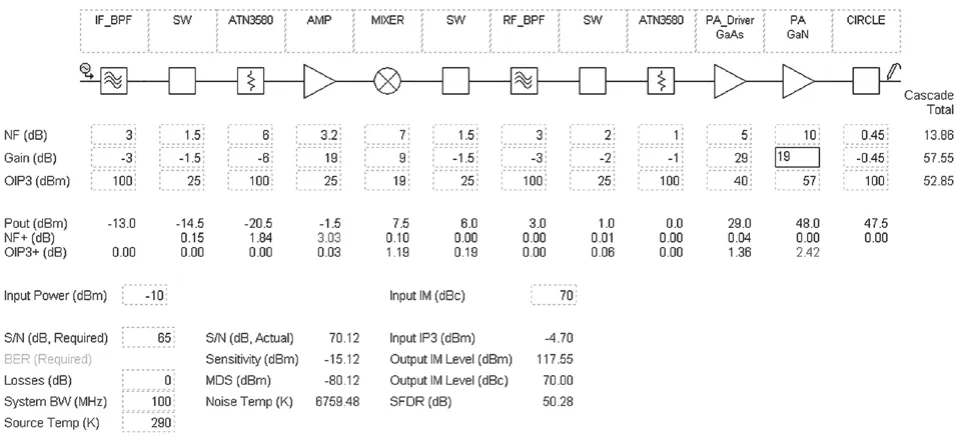

DDS产生中频激励信号,输出功率为-10 dBm,末级发射功率要求>50 W(47 dBm),所以发射支路的增益要求大于激励57 dB。发射支路的增益分配如图3所示。

图3 发射支路的增益分配

30%占空比下,单个数字收发SIP电源和功耗统计如表1所示。设计总输出功率为50 W,按30%占空比状态下平均功率36.946 W折算总输入功率为123.153 W,计算数字收发单元的效率等于组件总平均输出功率和组件总平均输入功率之比为40.6%。

表1 30%占空比下数字收发SIP电源和功耗统计

1.4 电磁兼容性设计

单元数字化收发SIP涉及到微波小信号、大功率发射、高速采集和波形产生以及调制电源等多种形式,而且电路集成度高,电磁兼容性复杂。因此从腔体效应、电源完整性以及收发隔离等几个方面进行电磁兼容性设计[7]。

腔体效应是数字化收发SIP EMC设计中一个重要环节,腔体的谐振频率和高Q值会导致组件工作不稳定,而且腔体内部具体的场分布特征也可能导致组件整体上的失败或成品率的低下等。设计优化的目标是腔体的谐振频率在工作频带之外[8]。另外,在热耗严重的地方(如末级功率芯片)不能有高强度的场分布,避免出现自激振荡,同时增强末级功率放大器的抗失配比对发射支路的稳定性也有很大的实际意义。

电源的完整性设计对组件的正常、稳定工作至关重要。造成电源不稳定的根源主要在于两个方面,一是器件高速开关状态下瞬态的交变电流过大,二是电流回路上存在电感。通过改变组件内部的接地方式,尤其是多层基板内部的接地方式,可以在多层布线结构要求和地平面阻抗之间找到平衡点,对各种电源之间进行地的隔离等来改善电源之间的干扰等[9]。此外,保证组件发射支路和接收支路之间无干扰,采用收发电源分时工作,确保收发之间完全隔离。

1.5 结构设计

单元数字化收发SIP由壳体、盖板、SMP连接器、差分连接器、微带板以及各种元器件组成。壳体采用50%硅铝材料气密封装,壳体底部材料采用高热导率的铝硅,热流密度较大的末级功率放大器芯片底部烧结热导率更高的金刚石铜,以提高散热效率。数字化收发单元的对外接口(SMP连接器、差分连接器)排布在壳体底部,与多通道一体化数字收发电路垂直盲配连接,以方便维修更换[10]。单元数字化收发SIP结构示意如图4所示。由于采用易于加工的硅铝合金,壳体整体加工成形,衬底与壳体表面改性后钎焊,盖板与壳体激光封焊。该工艺方案的特点是铝硅材料密度小,热物性能与碳硅铝相近,与碳硅铝相比材料具有可加工性,盒体可以整体加工,重量更低。此外,采用激光焊的工艺方法同平行封焊工艺方法相比,焊缝质量更加可靠。

图4 单元数字化收发SIP结构示意图

2 指标与测试结果

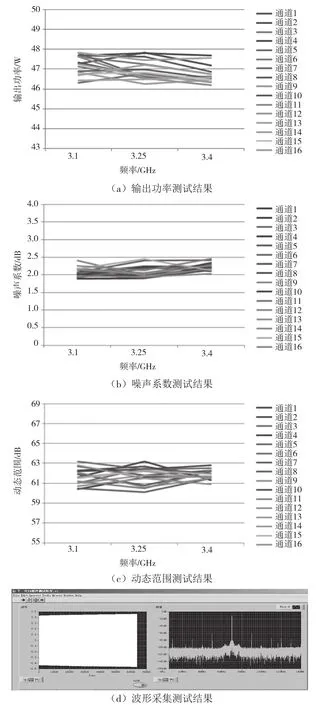

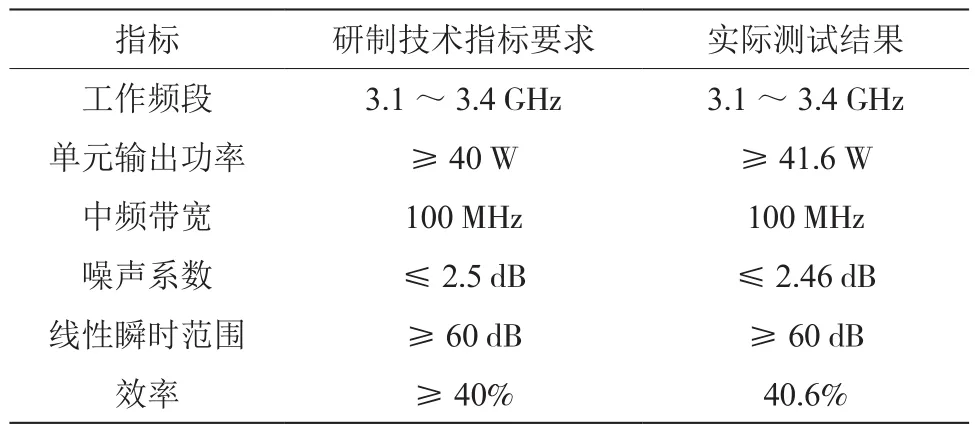

根据上述设计,研制S波段单元数字化收发SIP。图5为数字收发SIP的实物照片,对SIP的电信指标进行测试,测试曲线如图6所示,数字收发单元研制技术指标要求和实际测试结果具体如表2所示。SIP在工作频带内100 MHz信号带宽工作时,输出功率≥40 W、噪声系数≤2.46 dB、瞬时动态范围≥60 dB、效率≥40.6%。同时基于单元数字化收发SIP完成了数字阵列体制瓦片式天线阵面的样机研制,可满足多功能雷达系统的需求。

图5 单元数字化收发SIP实物图

图6 测试结果

表2 数字收发单元研制技术指标要求及测试结果

3 结 论

采用单元数字化方案和基于AlN陶瓷基板一体化集成设计,本文成功实现了一个满足典型雷达探测系统需求的S波段单元数字化收发SIP。经测试,该SIP在大信号带宽工作模式下实现了较好的电气性能,输出功率、效率以及传输速率等关键指标均有提升,同时实现了射频和数模信号的混合集成和组件小型化。可广泛应用于雷达探测和测控通信等数字阵列体制的电子系统中。此外,在该SIP的研究过程中,对单元数字化、小型化LTCC滤波器、MEMS滤波器、基于AlN的高密度集成、宽带信号采集和数据传输以及电磁兼容技术均做出了有益的尝试,积累了设计经验,并取得了良好效果,对后续数字收发组件设计也具有重要的借鉴意义。