基于FPGA的电压信号采集卡研究

2021-07-08崔文超郭瑞民董贺伟

李 东,崔文超,郭瑞民,董贺伟

(中国计量科学研究院环境计量中心,北京 100029)

0 引言

数据采集系统是信息处理系统的重要组成部分[1],其通常由模数转换器(analog to digital converter,ADC)和控制芯片组成。ADC决定了采样率和分辨率,控制芯片为ADC提供驱动时钟并接收ADC的采集数据。传统数据采集系统多采用单片机或数字信号处理芯片(digital signal processing,DSP)作为控制芯片[2-3]。单片机或DSP芯片提供的时钟速率较低,限制了ADC的采集上限。除此之外,采用单片机或DSP芯片进行数据采集,成本较高。近年来,现场可编程逻辑门阵列(field programmable gate array,FPGA)芯片由于其内部逻辑电路独特的可编程性,有效降低了研发成本,被广泛用作数据采集的控制芯片[4-6]。FPGA片上资源不受固化模块的占用,可被各个功能模块调用,灵活性高。

本文设计了一种基于FPGA的高速模拟信号触发采集系统,其电路部分主要由2片A/D芯片、1个FPGA芯片和1个USB通信芯片组成。研究中,通过时序设计控制2片A/D交替工作,并将采集数据存储到DDR2中,采集结束后由USB通信芯片传输到计算机(PC)。该采集系统分辨率为12位,采样率最高达到130 Msps,可应用在μs量级、0~5 V瞬时电压信号的采集。

1 采集触发装置设计

1.1 硬件电路设计

本文研究的数据采集系统电路原理图如图1所示,主要包括模拟信号调理电路、A/D转换电路、FPGA控制模块、USB通信电路和延时触发电路。

图1 数据采集系统电路原理图

模拟信号调理电路主要由运放AD8065和比例放大偏置电路组成,将0~5 V的输入电压转换为1~3 V电压,以满足A/D输入端的输入范围。模数转换电路主要包括2个模数转换器AD9226,其分辨率为12位。在65 MHz时钟的驱动下,2个AD9226交替进行信号采集,并将数据通过12位并行数据线输出给FPGA芯片。

FPGA控制电路由FPGA芯片(型号:EP4CE15F23C8)、DDR2芯片和Flash芯片构成。研究中,通过对FPGA芯片进行编程,设计FPGA内部逻辑控制电路。DDR2芯片(型号:MT47H64M16)和Flash芯片(型号:M25P64)作为储存芯片与FPGA相应管脚连接。其中,DDR2芯片有1 G的储存量,用于临时存储采集的数据。Flash芯片用来存储编写的控制程序,确保FPGA芯片启动时,能够正常加载芯片代码,完成FPGA内部控制电路的设计。

USB通信电路主要由USB芯片构成,并与FPGA相应管脚相连。通过外接USB接口,实现FPGA与计算机的通信。图1中,延时触发输出电路通过缓冲器和电平转换芯片与FPGA的3.3 V电压输出管脚相连,其末端输出1.7 V电压信号用于控制触发信号的输入输出。

1.2 FPGA程序设计

FPGA程序功能图如图2所示,主要包括锁相环(phase locked loop,PLL)模块、AD读取模块、触发模块、USB通信模块、控制模块和DDR2模块。首先,编写FPGA程序,并对编写的程序进行联合仿真。

进行程序设计时,采用外部晶振产生50 MHz信号作为系统时钟,输入到PLL模块。PLL主要功能是产生系统所需的3类时钟信号,频率分别为130 MHz、50 MHz和65 MHz。其中130 MHz信号用作USB模块及DDR2模块的写入信号源,50 MHz信号为DDR2模块的工作信号源,65 MHz信号提供给2个AD9226芯片。

AD读取模块划分为3个子模块:信号-节拍模块、信号-位宽转换模块和触发模块。在130 MHz时钟信号驱动下,信号-节拍模块将两路AD交替采集的电压信号组合为一路电压信号,数据位宽为12位[7-8]。程序设计时,通过信号-位宽模块将该12位数据拓展为32位数据,并输出给触发模块,其中低12位为有效数字。在触发模块中,采集的电压信号与设定的阈值电压相比较,若大于阈值电压,触发模块则输出低电平延时使能信号;若小于阈值电压,触发模块保持高电平输出。本研究中,设定的阈值电压和触发延时时间分别为1.5 V和1 ms。

DDR2模块由先入先出(first input fist out,FIFO)控制模块和DDR2控制模块构成[9-10]。其中,DDR2控制模块用来响应FIFO控制模块发出的数据写读请求,并控制DDR2芯片数据的读写。DDR2芯片的工作频率为166.7 MHz,PLL输出给DDR2模块的时钟为130 MHz,两者速率不匹配。本文采用FIFO控制模块作为信号缓冲池,将需要写入、读出DDR2的数据储存在FIFO中,实现外部数据与DDR2芯片数据读写速率的匹配。本研究中,在FIFO控制模块中建立了一个数据宽度为32位,深度为1024的写FIFO和读FIFO。

USB通信模块用于FPGA芯片与USB芯片(型号:CY7C68013A)之间的通信,接收来自USB芯片的指令,并传输从DDR2中读取的数据[11-12]。控制模块是整个系统的核心,用于向每个模块发出工作指令、控制数据流的方向以及响应PC的控制指令。控制模块的输入信号包括时钟信号,复位信号,启动信号和触发信号。

1.3 采集时序与工作流程

采集时序如图3所示,读取时钟为130 MHz,AD的工作时钟为65 MHz。如图3所示,2个AD9226工作在相位完全相反的时钟源下,接收数据的相位也完全相反。在130 MHz信号-节拍模块的驱动下,2列65 MHz的数据等效为1列时钟为130 MHz的数据。

图3 等效时钟时序图

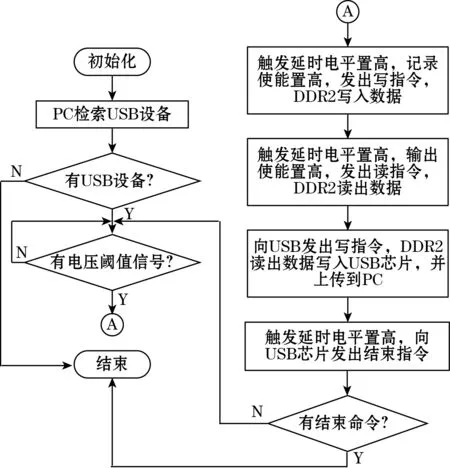

数据采集系统的工作流程如图4所示,主要包括模块初始化部分、触发信号产生部分、DDR2数据写入/读出部分和USB芯片到PC的数据上传部分。

图4 采集系统的工作流程

数据采集过程由图2所示的控制模块控制运行,首先进行系统初始化,并在PC端检索USB设备。接着使控制模块的复位信号置低,开始信号置高,使控制模块处于待触发状态。此时,记录使能信号和输出使能信号均为低电平。当采集的电压信号高于设置的阈值电压时,触发使能信号变为高电平,记录使能信号置为高电平,但输出使能信号依旧在设定的延迟时间内保持为低电平。在130 MHz时钟的驱动下,控制模块将2个65 Msps的AD9226数模转换器采集的数据交叉写入DDR2芯片,完成触发采集过程。当设定的延迟时间结束后,记录使能信号置为低电平,输出使能信号置为高电平,且保持另一长度的延迟时间。

在触发延迟信号与记录使能信号为高电平时,控制模块发出写指令,将采集的数据写入DDR2芯片。等触发延迟信号与输出使能信号为高电平时,控制模块发出读指令,读出DDR2中的数据,并向USB芯片发出写指令,将读出的数据写入USB芯片,上传到PC。控制模块进入待触发状态,等待新一轮的数据采集过程。

本研究中,记录使能信号为高电平,同时输出使能信号为低电平的延迟时间为50 μs。记录使能信号为低电平,同时输出使能信号为高电平的延迟时间为500 μs,以确保DDR2的写入时间和读出时间之和小于触发模块的触发延迟时间。

2 结果与讨论

2.1 正弦波信号采集结果

为了测试该采集系统的性能,采用信号发生器产生标准信号,同时利用示波器和该采集系统对标准信号进行采集并进行对比。信号发生器(型号:Agilent,33500B)生成的标准正弦信号频率分别为50 kHz、100 kHz、500 kHz和1 MHz,幅值为4 V。示波器(型号:Agilent,DSO5054A)的采样率为4 GS/s。本文设计采集装置的采样率为130 Msps,采集结果如图5所示,其中连续直线代表示波器采集的信号,点线为采集装置采集的正弦波信号。由图5可以看到,两者采集的波形完全重合,且采集的信号电压值与实际信号电压值一致性较好。

(a)50 kHz

2.2 标准衰荡信号采集结果

在光腔衰荡光谱(CRDS)技术相关研究中[13-15],需要利用采集卡收集从衰荡光腔透射的成指数衰减的光信号。以往的CRDS装置数据采样率低,大多数在10 Msps以内。为了进一步评价本论文设计的采集卡性能,采用信号发生器产生标准衰荡信号,通过比对采集卡和示波器的采集结果,验证该装置在CRDS装置中的应用潜力。

研究中,信号发生器产生时间长度为10 μs的标准衰荡信号,示波器的采样率为4 GS/s,本文设计采集装置的采样率为130 Msps。结果如图6所示,其中连续直线为示波器采集的信号,点线为采集卡采集的信号,两者完全重合。采用指数衰减函数分别对采集卡和示波器采集的数据进行拟合,所得的衰荡时间分别为1.609 9 μs和1.596 6 μs,两者相差约0.83%,可用于CRDS研究中的衰荡信号采集。

图6 指数衰减信号

3 结束语

本文设计了一种基于FPGA芯片的高速数据采集系统。系统硬件包括模拟信号调理电路、模数转换电路、FPGA控制模块、USB通信电路和延时触发电路。编写的FPGA内部程序包括锁相环模块、AD读取模块、触发模块、USB通信模块、控制模块和DDR2模块。采用等效时钟原理,控制2片采样率为65 Msps的数模转换器交替工作,实现了130 Msps的采样率。利用该系统采集50 kHz~1 MHz的正弦信号和时间长度为10 μs的衰荡信号,采集结果与示波器一致。本文设计的采集系统,可用于CRDS装置中的衰荡信号采集。