高速电力线载波信道分析模块的设计与实现

2021-06-30郝伟琦王贤辉肖德勇陈奎熹

郝伟琦,王贤辉,李 铮,肖德勇,陈奎熹

(北京智芯微电子科技有限公司,北京 102200)

0 引言

电力线载波通信(Power Line Communication,PLC)是一种使用电力线作为物理通信介质的通信方式。利用电力线等媒体传输数据信息,可以降低运营成本、减少构建新的通信网络的支出[1]。而相比窄带载波,高速载波具有速率高、抗干扰能力强等优点,可以应用于用电信息采集、智慧能源等多场景,作为解决“最后一公里”问题的有效传输模式,是组成电网信息物理系统的基础底层网络构件[2]。但与传统通信介质相比,电力线上各类电力负载的接入及其接入的变化就造成了复杂多变的电力线信道特性[3-4],影响电力线信道通信质量的特性有线路阻抗、噪声等[5],其中噪声是影响低压电力线载波通信质量的重要因素[6]。

当前载波通信领域正在研究各种抗噪声方法以提高抗噪声干扰能力[7]。传统抗噪声研究的一般流程为现场采集,实验室仿真,最后进行现场测试。该方式在实验室难以还原现场复杂的噪声环境,而在现场验证费时费力,覆盖噪声场景有限,难以应对大规模高速电力线载波现场调试运维需求。

为此,本文提出了一种高速电力线载波信道分析模块,可实现噪声采集、噪声分析、数据存储、信道测试等功能,并且可在实验室模拟真实现场环境。本信道分析模块基于现场可编程门阵列(Field Programmable Gate Array,FPGA)和模拟前端(Analog Front End,AFE)芯片实现,成本相对较低,便于携带,解决了高速电力线载波通信中噪声研究和现场运维测试的难题。

1 噪声分析模块架构设计

1.1 功能指标定义

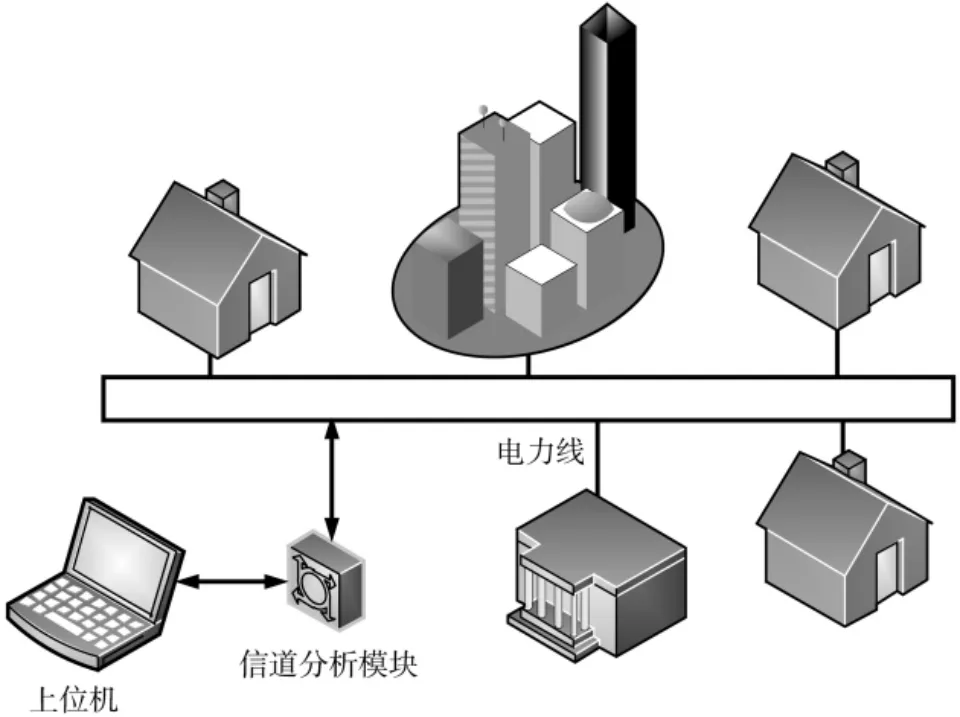

信道分析模块的连接示意图如图1 所示。图中所示为一个典型的电力线环境,信道分析模块通过电力线耦合接口连接至电力线,可以从电力线采集或向电力线注入噪声。数字通信接口连接至上位机,可由上位机控制模块的工作状态。

图1 信道分析模块连接示意图

为满足高速电力线载波通信中噪声研究和现场运维测试的需求,噪声分析模块需具备以下主要功能:

噪声采集功能:采集带宽0.2~25 MHz,单次采集时长大于20 ms;支持单次采集、多次采集、随机延时盲采等多种方式。

噪声分析功能:现场噪声频谱的FFT 实时分析,找出干扰频点分布。

噪声录波回放功能:支持回放噪声信号的装载、循环回放,多种噪声切换等。

噪声信号发生功能:白噪声、脉冲噪声、窄带噪声、扫频噪声等。

信道测量功能:支持单频、扫频等测量信号发生,测量信号的接收和分析,进行信道衰减测试。

1.2 模块架构设计

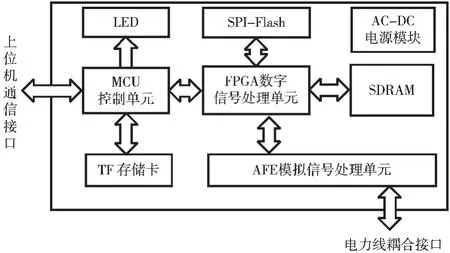

信道分析模块架构分为模拟信号处理、数字信号处理和主控制器三部分;模拟信号处理电路基于AFE 芯片AD9866 搭建,采样率为50 MS/s,采样位宽为12 bit,可采集并重建覆盖高速载波通信频段的噪声信号。数字信号处理和主控制器基于FPGA 及MCU 设计,两者采用SPI 总线互联,实现模拟信号的高速采样、FFT 分析与回放功能。FPGA 与MCU 协同工作,由FPGA 硬件逻辑处理高速数据的采集及缓冲,MCU 负责对FPGA 的控制及文件系统处理。

信道分析模块原理结构框图如图2 所示。模拟信号处理电路将来自电力线的模拟信号放大后转换为数字信号,经由FPGA 进行处理,并且可将FPGA 输出的数字信号转换为模拟信号,注入电力线进行发送。FPGA 主要进行高速数字信号的处理工作,SDRAM 存储器实现采样数据缓存,MCU 控制器实现了文件及控制接口,SPIFlash 用于保存FPGA 的配置文件,AC-DC 电源模块用于为系统供电。

图2 信道分析模块原理结构框图

2 主要功能模块实现

2.1 FPGA 逻辑模块划分

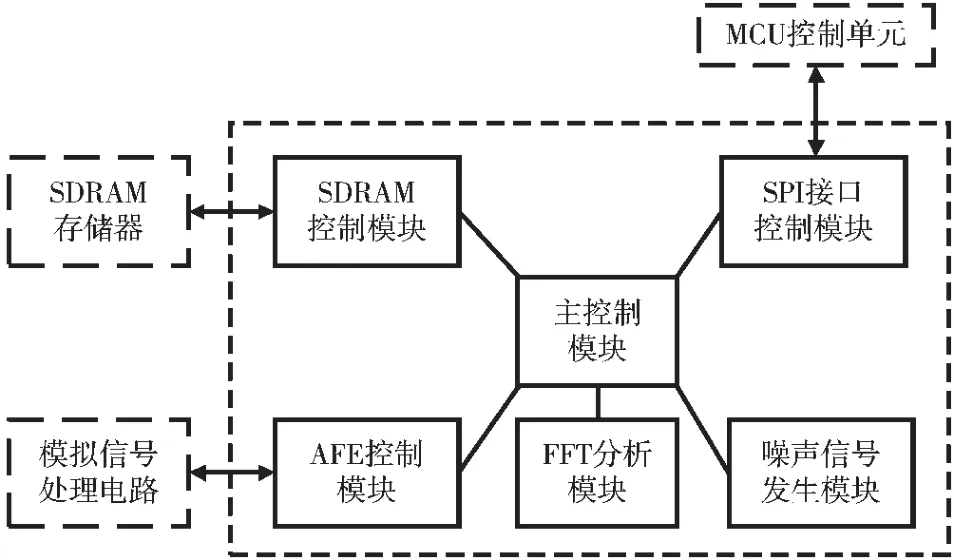

依据系统功能及架构,模拟信号的采样率选择为50 MHz,在12 bit 位宽下数据吞吐率为600 Mb/s,需要使用SDRAM 进行数据缓冲。根据系统功能需求,FPGA内部逻辑模块的划分如图3 所示。

图3 FPGA 内部逻辑模块

主控模块:运行主状态机,协调FPGA 内部各个模块工作,解析MCU 通过SPI 下发的指令码。

SDRAM 控制模块:控制外部SDRAM 存储器,实现数据存储、读取及刷新逻辑。

AFE 控制模块:控制AD9866 芯片实现模数及数模转换,实现模拟信号的接收及发送。

信号发生模块:控制可编程噪声信号数字激励的生成,用于波形发生功能。

FFT 分析模块;用于实时分析采集到的信号频谱信息,用于噪声实时分析及信道衰减测试。

SPI 接口控制模块:作为控制命令及数据交互通道,对外接口符合SPI 接口标准[8]。

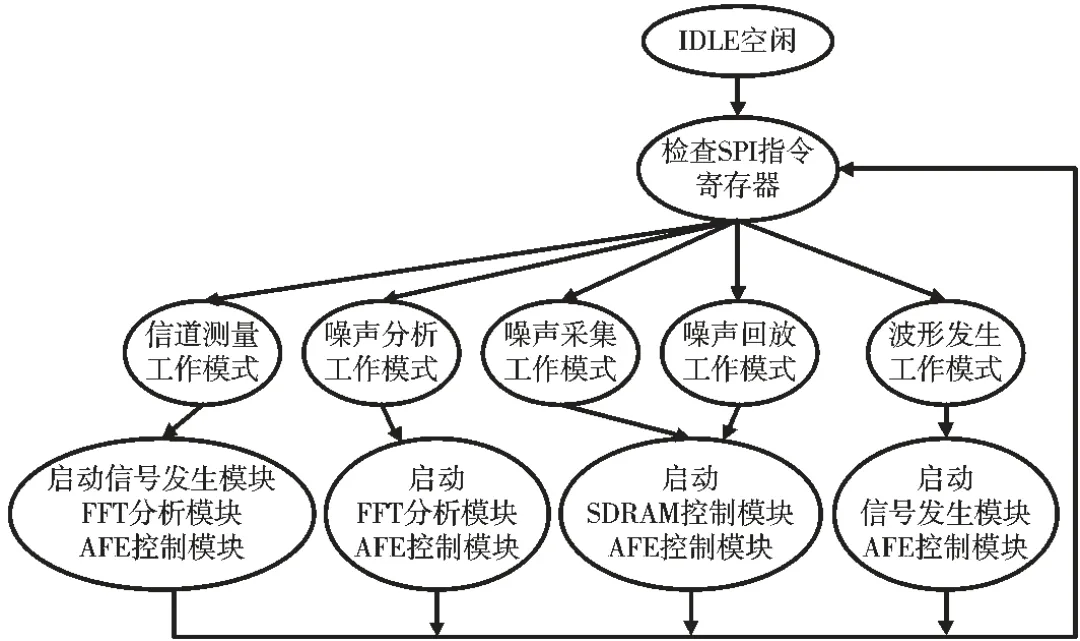

2.2 主控模块

主控模块主要功能为协调各个逻辑模块正常工作,根据不同的工作状态控制数据的接收及发送模块。主控模块的逻辑状态机如图4 所示。

图4 主控模块逻辑状态机

2.3 SDRAM 控制模块

SDRAM 控制模块使用状态机实现SDRAM 芯片的读写逻辑接口[9],其状态机包括初始化、数据读写、数据刷新等操作[10-11]。模块启动稳定后开始对SDRAM 芯片进行初始化操作,配置工作模式。读写时,首先进行激活,读写数据操作后自动进行预充电,并对行地址进行复位的操作。

由于在电力线噪声采集及噪声回放过程中数据流是连续的,但SDRAM 芯片需要定期执行数据刷新,不能持续读写,故需要使用FIFO 对数据进行缓冲[12-13]。

AFE 控制模块采集的数据首先写入FIFO 中,读写逻辑电路从FIFO 中读取数据写入SDRAM。写完一页数据后执行数据刷新动作,然后等待再次触发SDRAM 写入动作。如此往复,完成对采样数据的连续写入。在噪声回放模式时,数据流向相反,实现采样数据流的连续输出及噪声重建。

2.4 信号发生模块

信号发生模块可以发生周期性的噪声信号,基于XILINX公司的DDS IP 核以及数字逻辑实现[14]。信号发生模块能够发送白噪声、脉冲噪声、窄带噪声、扫频噪声信号,可用于电力线载波设备的定量抗噪声测试。

2.5 FFT 分析模块设计

FFT 分析模块基于XILINX 公司的FFT IP 核实现,可对采样数据流进行快速傅里叶变换[15],获取信号的频谱特性。

输入离散信号数据流通过FFT 模块计算,可得出傅里叶变换实部及虚部,并储存在FPGA 内部寄存器组,供MCU 进行读取,获取实时的频谱分析数据。

3 MCU 控制程序设计

MCU 的主要功能为控制FPGA 工作模式、接收上位机指令、执行文件管理相关功能。

3.1 主程序流程

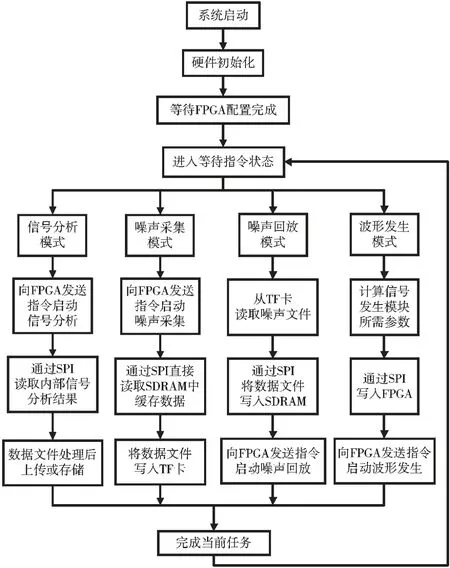

MCU 与FPGA 协同工作可以发挥各自优势[16],MCU嵌入式软件主要程序执行流程如图5 所示,系统启动后执行硬件初始化,等待FPGA 完成配置,由上位机发送指令进入不同的工作模式分支。

图5 MCU 主程序流程

3.2 噪声采集模式工作流程

MCU 向FPGA 写入指令码启动噪声采集,支持单次采集、多次采集、随机延时盲采等多种定制采集方案。

3.3 噪声回放模式工作流程

MCU 读取TF 卡中的数据文件,将数据写入SDRAM中,然后向FPGA 写入指令码启动信号回放。FPGA 模块循环回放SDRAM 中缓存的数据文件,输出录制的噪声信号。

3.4 信号发生模式工作流程

MCU 将扫频频率、步进时间、步进频率等控制参数写入FPGA 内部的信号发生模块,为电力线信道测试提供激励源[17]。

3.5 噪声分析功能工作流程

噪声分析功能用于实时分析现场噪声干扰频域特性,FPGA 循环采样噪声数据并进行FFT 计算,从而分析当前信道噪声的频域特性。

3.6 信道测量功能工作流程

信道测量功能依托于信号发生功能与信号分析功能实现,测量时,需要使用两个信道分析模块协同工作,其中模块1 工作于信号发生模式作为激励源,模块2 工作于信号分析模式测量信道。

信道测量方法如图6 所示。模块1 在载波信道发送端接入电力线,循环发送覆盖电力线通信频段的扫频噪声信号;模块2 在信道发送端使用最大保持模式接收信号、测量信号频谱特征并记录为发送端频谱数据1。然后模块2 在信道接收端使用最大保持模式测量信号频谱特征并记录为接收端频谱数据2。将频谱数据1 与频谱数据2 在上位机进行矫正计算,即可得出该通信频段载波信道的衰减特性。

图6 信道测量功能示意图

4 实现及测试结果分析

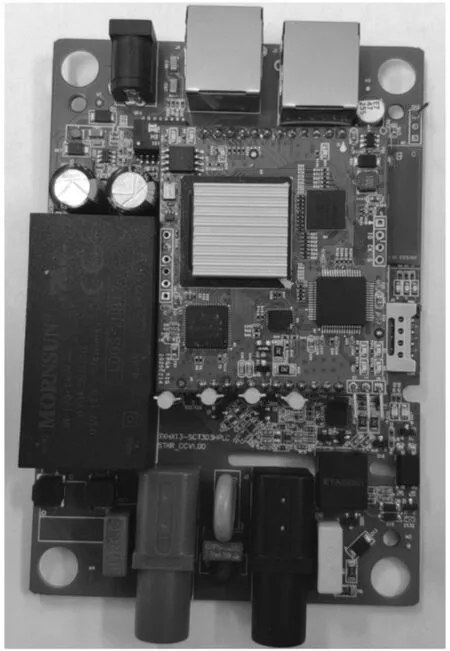

按照前述章节设计实现的信道分析模块样机实物如图7 所示,模块整体外形尺寸为12 cm×8.2 cm,可使用电力线或外接直流电源供电。

图7 信道分析模块样机

4.1 噪声信号采集功能测试

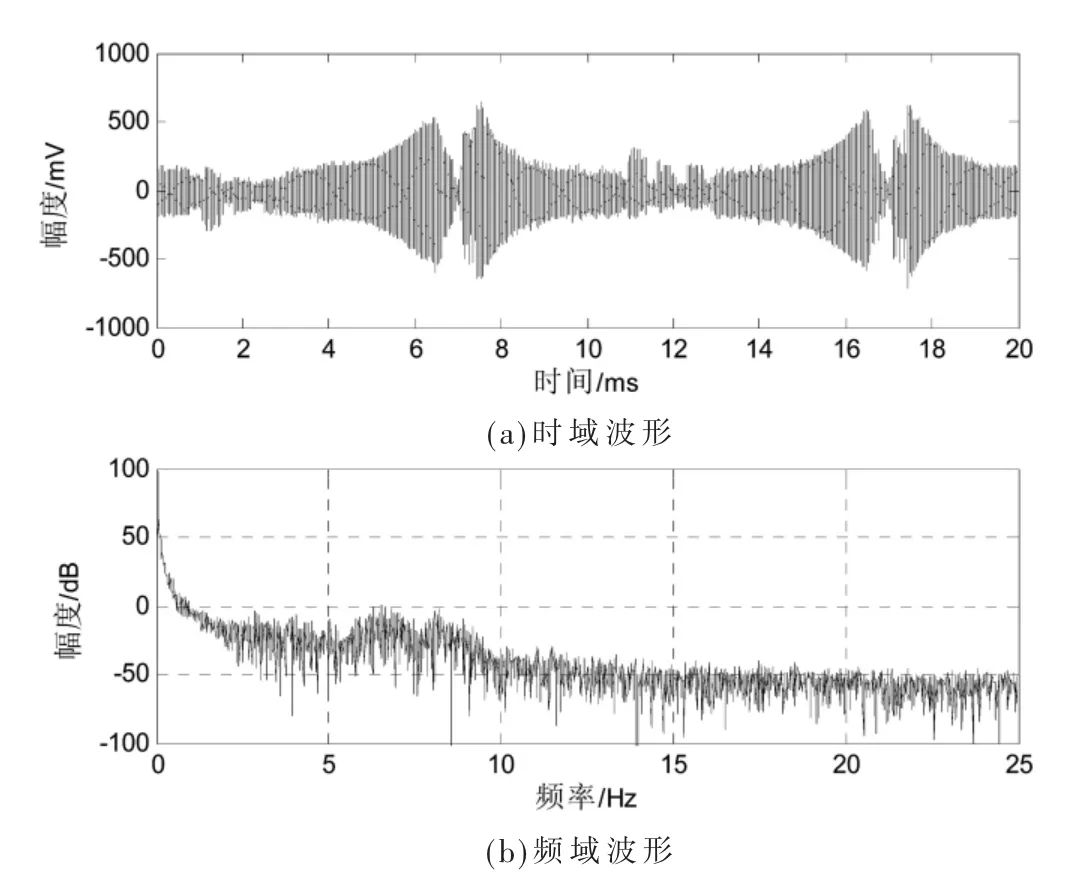

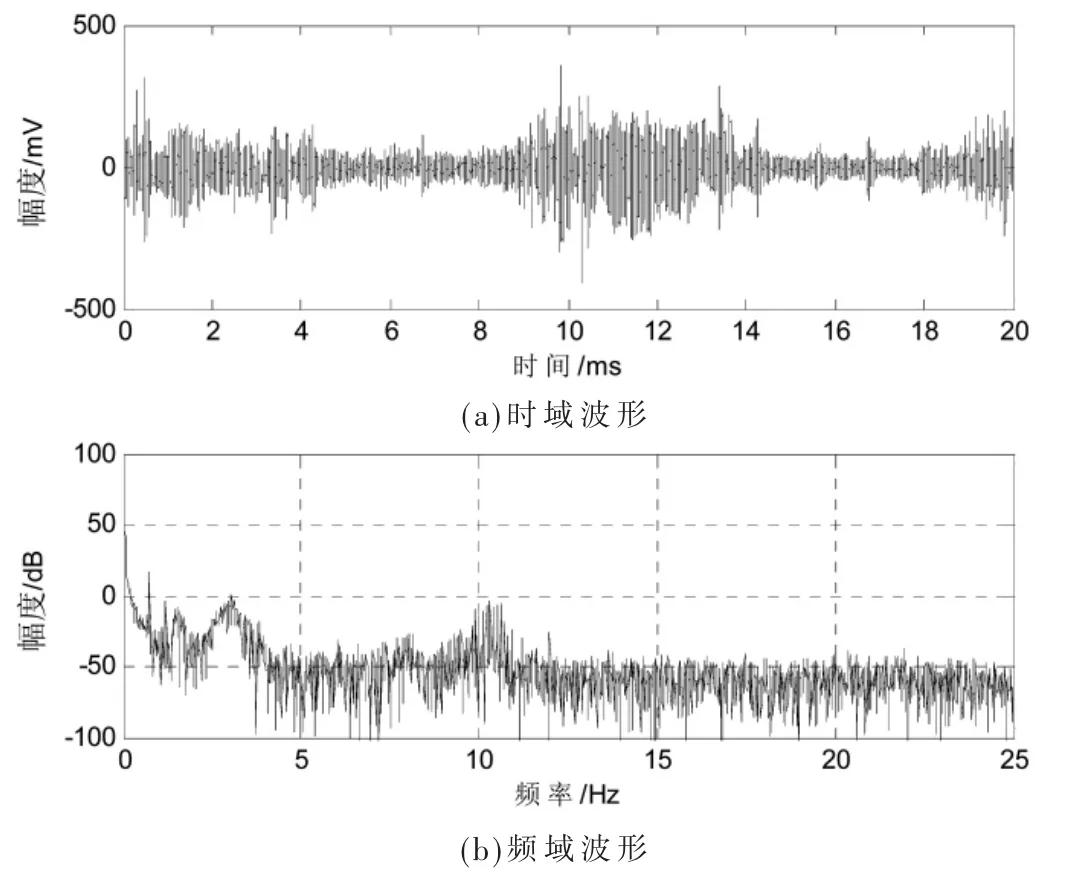

将信道分析模块接入实验室环境,电力线采集到的噪声数据经软件可视化处理后的时域图形及频域图形如图8 所示,采样长度为20 ms。

图8 实验室环境电力线噪声时域及频域波形

将噪声分析模块接入某现场台区配电室,采集到的噪声数据经软件可视化处理后的时域图形及频域图形如图9 所示,采样长度为20 ms。此环境为居民用电小区,用电负载较为复杂,包括一些大功率居民用电设备。

图9 现场环境电力线噪声时域及频域波形

4.2 噪声信号回放功能测试

使用信号回放功能回放采集的数据文件,将信道测量模块输出接至示波器,输出录制的噪声波形信号,可观察到输出的噪声信号与采集信号的波形一致。

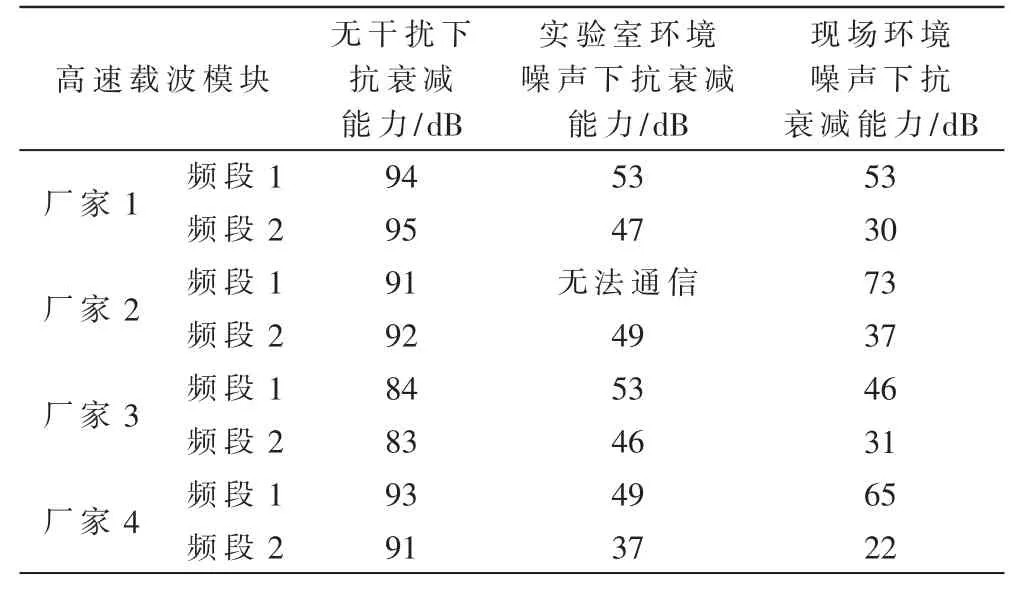

将不同环境下噪声注入电力线载波通信测试平台,使用不同厂家标准HPLC 载波模块在此环境下进行载波回传测试,测试模块的抗噪声能力,测试条件为TMI=4,PB=1,测试结果如表1 所示。

表1 不同厂家模块在典型噪声环境下抗衰减能力

4.3 噪声信号发生功能测试

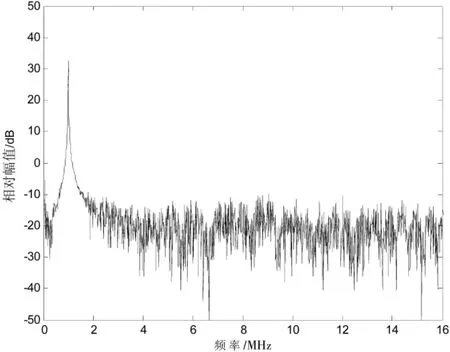

对扫频噪声波形发生功能进行测试,扫频参数为起始频率1 MHz,结束频率12 MHz,此参数配置下Pico 示波器采集到的频谱尖峰保持数据经过可视化处理后的频域图形如图10 所示。可观察到波形扫频起始频率、截止频率与设定相同,表明波形发生功能正常。

图10 信道分析模块扫频模式输出

4.4 噪声分析功能测试

使用信号源向信道分析模块注入1 MHz 频率的单频噪声信号,使用信号分析模式输出采集的频谱数据,经过可视化处理后可观察到接收信号的频谱信息,如图11所示,可观察到1 MHz 的单频噪声信号频谱,表明模块噪声信号分析功能工作正常。

图11 信号分析功能输出信号频谱

4.5 信道测量功能测试

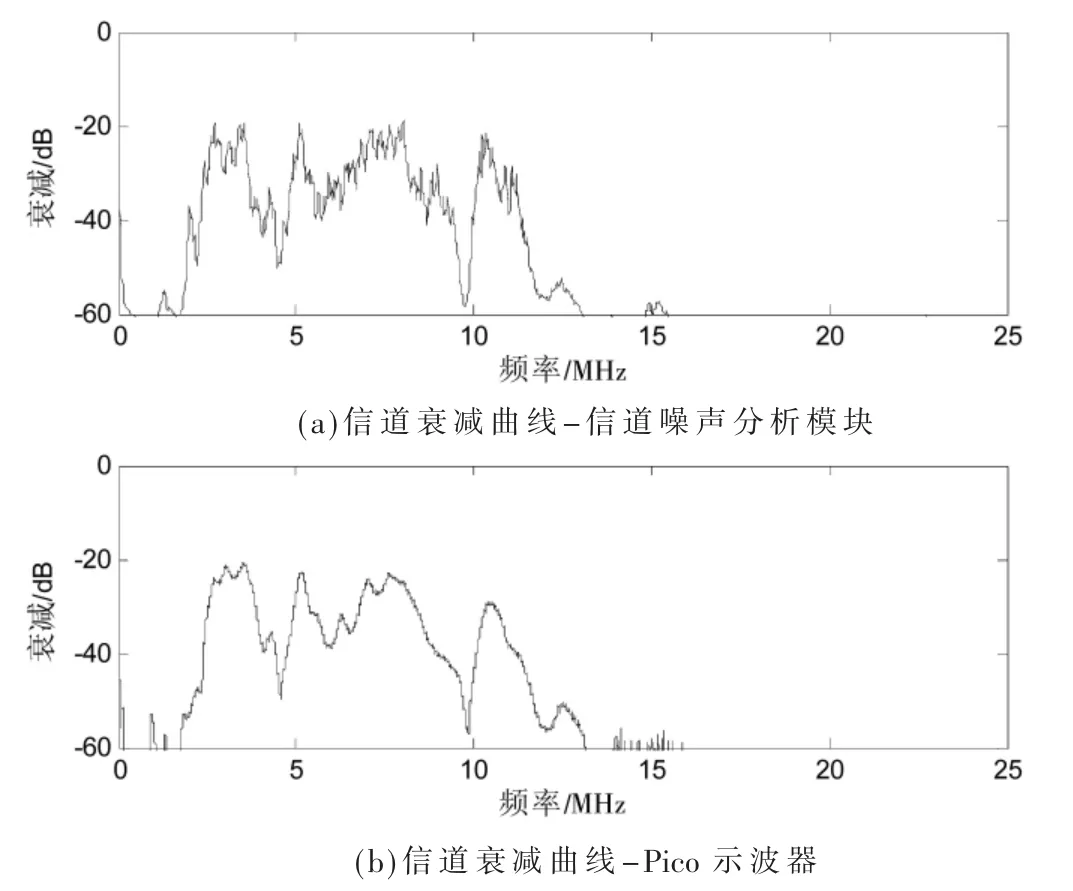

将一个模块配置为扫频信号发生模式,将信号注入电力线,使用另一个信道分析模块在另一位置采集此信号并输出频谱最大保持数据,经过软件可视化处理后可生成信道衰减曲线,如图12(a)所示。图12(b)为Pico 示波器在同一接收位置采集的频谱最大保持数据经过标定后输出的信道衰减曲线。从图中可观察到,电力线信道上衰减导致接收端信号频谱不完全平坦,存在某些衰减较大的频点。通过对载波信道的衰减特性分析,有助于选择合理的载波通信频率,并为中继器的安装位置选取提供理论依据。

图12 电力线信道接收端信道衰减曲线

5 结论

通过上述测试,表明本文设计的高速电力线载波信道分析模块各功能工作正常,噪声采集及回放功能达到了预期指标,可应用于现场噪声样本的采集及分析,并且能够在实验室电力线测试信道注入现场环境噪声,模拟现场工作环境,解决了高速电力线载波通信中噪声研究和现场运维测试的难题,对高速电力线载波技术的应用推广具有重要意义。