基于FPGA 的LVDS 无时钟数据传输方案设计与实现*

2021-06-30毕彦峰胡陈君

毕彦峰 ,李 杰 ,胡陈君

(1.中北大学 电子测试技术重点实验室,山西 太原 030051;2.苏州中盛纳米科技有限公司,江苏 苏州 215123)

0 引言

常规弹药制导化改造试验过程中,事后回读弹载数据记录仪所记录的各种指令参数是测试反馈中重要的方式。在靶场测设发射导弹之前,数据回读也是监测弹药状态的一种十分重要的方式。随着科技的进步,数据存储设备愈发趋近小型化、高速化,所能提供的数据回读接口也越来越少,导致对采集存储设备进行数据回读时无法同时满足速度快和接口少的条件[1-2]。

在采集侵彻或冲击信号时,由于所需要的采样频率较高,产生的数据量较大,普通的低速并行接口无法进行高速数据传输,LVDS 接口采用高速串行差分协议,抗干扰能力强,可以满足高速传输的需求[3-4]。但是由于弹上测量设备空间有限,而传统的LVDS 接口包含一路差分数据和一路差分时钟,系统中一般采用主控芯片外挂LVDS 传输芯片的模式[5-6],当多路LVDS 接口同时使用时会过多占用弹内有限的空间。因此,本文提出一种基于FPGA 的无随路时钟的高速数据传输方案,仅使用一对差分引脚传输一路LVDS 差分数据就可以实现1 Gb/s的板间数据通信,无需外挂LVDS 芯片并将通信接口的数量减半,当系统中有多路LVDS 接口时可以很大地减少接口数量。具体来说,该方案的主要内容体现在以下几个方面:(1)用板载时钟模拟传统差分时钟实现无时钟LVDS 传输数据,以达到精简接口的目的;(2)利用SERDES 内部鉴相器解决每次上电时板载时钟和差分数据初始相位处于随机状态所导致的误码问题;(3)提出利用8B/10B 编码解决传输连续相同电平时鉴相器失效的问题;(4)扩展SERDES 的反序列化比例至10:1 来完成8B/10B 编码后的数据反序列化。

1 系统总体设计

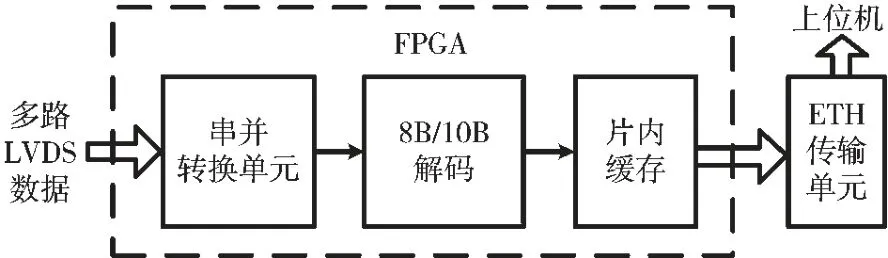

如图1 所示,系统主要由串并转换单元、8B/10B 编码、片内缓存和以太网传输单元四部分组成。串并转换单元负责模拟LVDS 随路时钟,参照鉴相器提供的相位关系对齐模拟时钟和LVDS 数据,并将高速串行数据转换成为10 bit 并行数据。8B/10B 解码模块主要负责将接收到的10 bit 并行数据转换成为有效的8 bit 数据。经过片内RAM 缓存,通过以太网将数据传输到上位机。

图1 系统总体设计

1.1 模拟随路时钟设计

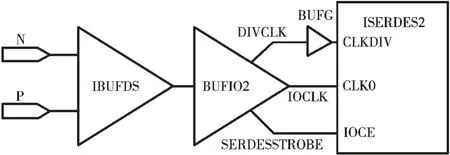

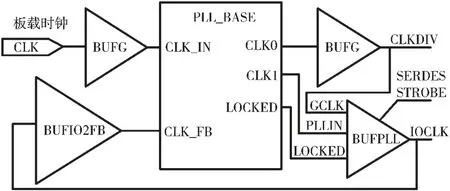

传统的LVDS 数据传输总线包含一路LVDS 差分数据和一路LVDS 差分随路时钟。差分数据在传输时需同步于差分时钟,数据在进行反序列化时也需要参考随路时钟。但很多弹载数据存储设备由于接口数量有限,无法同时提供LVDS 差分数据和随路时钟。考虑到在实际数据传输时,链路双方采用已知的固定时钟频率进行数据传输,即可以采用一种回读系统自己提供时钟的方式来模拟随路时钟,并将数据按照此时钟进行串并转换。这种时钟需要模拟真实的随路时钟,为串并转换模块提供参考时钟和选通脉冲STROBE。传统的随路时钟处理方式如图2 所示,差分随路时钟通过IBUFDS 和BUFIO2为ISERDES 提供CLKDIV、IOCLK 和SERDESSTROBE 3 个信号[7-8]。在模拟随路时钟时同样需要产生这3 个信号,如图3 所示,利用板载时钟通过锁相环倍频产生CLKDIV,并通过BUFPLL 可以产生IOCLK 和SERDESSTROBE 信号。

图2 传统随路时钟处理方式

图3 板载时钟模拟随路时钟

1.2 相位调整技术研究

利用FPGA 内部提供的ISERDES 对数据进行反序列化时需要参考CLKDIV 时钟,但由于CLKDIV 时钟是根据板载时钟通过PLL 生成的,因此CLKDIV 时钟的相位与板载时钟保持一致。而每次上电时,LVDS 差分数据与CLKDIV 的初始相位关系处于一个随机的状态,在这个初始相位关系条件下依照CLKDIV 对数据进行反序列化,若不满足触发器的静态时序要求,在高速传输时会产生极大的误码导致无法传输有效的数据。可以利用FPGA 内部的IODELAY 对数据通路添加延迟并且保持时钟的相位不变的方式来产生相位偏移,从而达到调节数据和时钟相位关系的目的。但是每当系统重新上电或复位时,这种数据和时钟的初始相位状态是随机的,调节相位关系无法通过添加固定时间的延迟来解决,所以在设计时只能采取在传输数据的过程中动态地调整相位关系。FPGA 内部的SERDES 提供的鉴相器可以检测当前数据相对于参考时钟的上升沿相位超前或者滞后,可以根据鉴相器提供的相位关系动态地调节IODELAY 的延迟值,这样系统复位、布线或者温度等因素导致的相位偏移都可以通过这种动态调节的方式调整到最佳的相位关系,从而有效地按照板载时钟将串行数据反序列化。

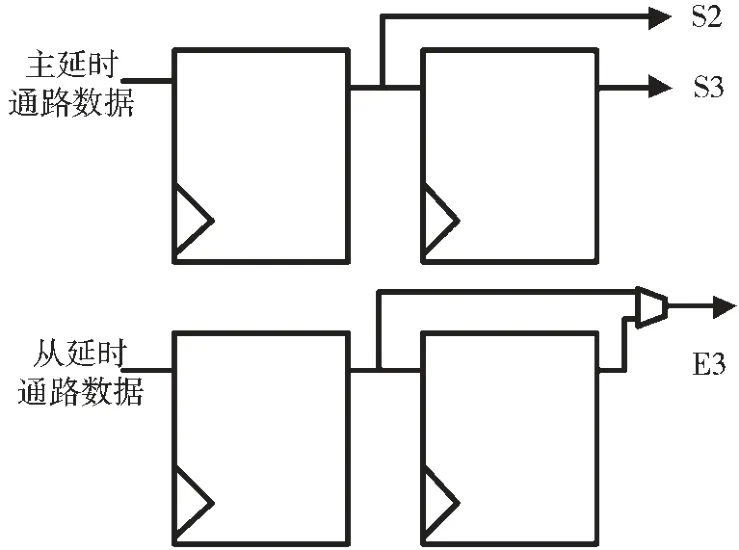

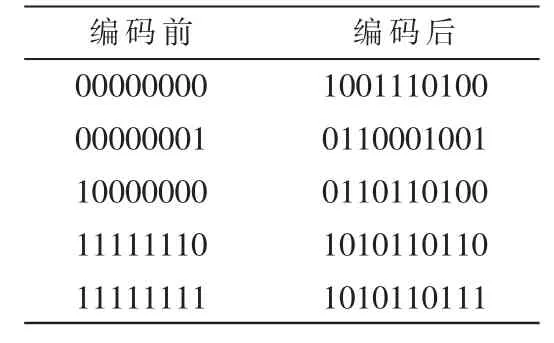

鉴相器的结构和原理如图4 所示,S2 和S3 相差一个时钟周期,通过判断S2 和S3 不相等来判定串行数据是否发生变化。通过比较S3 和E3 来指示相位关系是超前还是之后。即只有在S2≠S3 的条件下,E3 和S3 产生的相位检测结果才是有效的。当串行数据连续发送相同的数值时S2 始终等同于S3,即连续的0 或者连续的1,会使得相位检测模块失效,直到发生电平翻转才可以恢复相位检测。当进行连续相同电平的传输,会导致鉴相器长时间失效,这种相位的校准机制就会暂时停止,此时如果受到温度等影响产生相位的偏移,若不满足时序收敛的条件则会产生误码,这个问题可以通过对数据进行8B/10B 编码解决。8B/10B 编码一般使用在交流耦合中来实现直流均衡,在本设计中数据发送前端对数据进行8B/10B 编码,数据回读系统进行数据回读时,可以通过8B/10B 解码将数据恢复成为有效信号。通过8B/10B编码进行扰码的数据会保证一段时间的直流平衡,即一段时间内的0 和1 数量相等[9]。将数据进行8B/10B 编码传输时,连续的相同电平最高不会超过5 bit,即最少每5 bit 会进行一次相位检测,可以为数据的正确恢复提供足够的电平跳变,这样即使有连续相同电平的8 bit数据也会被编码为含有电平跳变的10 bit 数据。典型数据的8B/10B 编码如表1所示,在传输多个连续相同的电平时,都会被插入多个电平跳变,可以防止鉴相器的长时间失效。

图4 鉴相器电路

表1 典型的8B/10B 编码

1.3 比例扩充设计

利用8B/10B 编码可以解决鉴相器失效的问题,但是这种编码传输的方式又会带来一个新的问题,FPGA 内部的SERDES 最高支持8:1 比例的数据反序列化,而对数据进行8B/10B 编码后,数据位宽从8 位扩展到了10 位,从而无法实现对串行数据的反序列化。

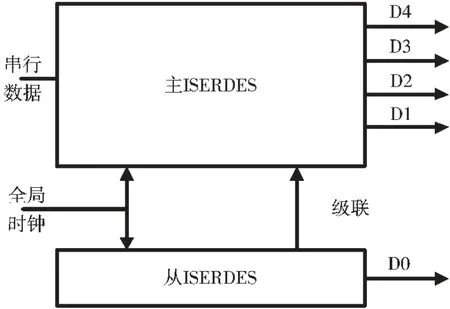

FPGA 内部单个SERDES 支持2:1~4:1 比例范围的数据反序列化,将两个相邻的SERDES 级联可以完成2:1~8:1 比例范围的数据反序列化。当需要对数据进行10:1 比例反序列化时,可以采用一种巧妙的方式,通过对数据进行2×5:1 比例反序列化来实现。

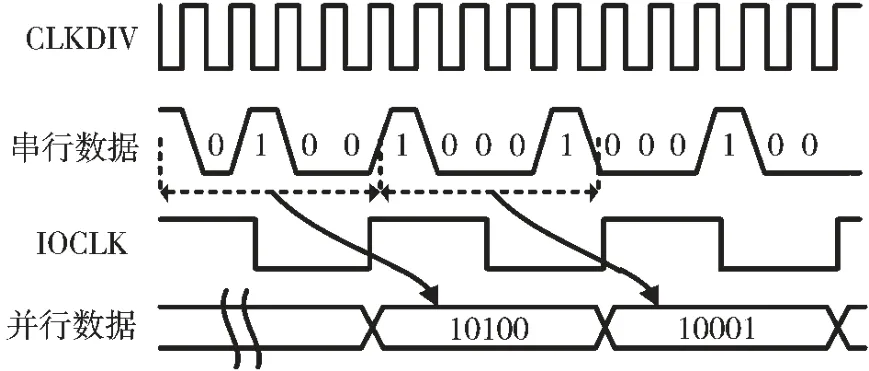

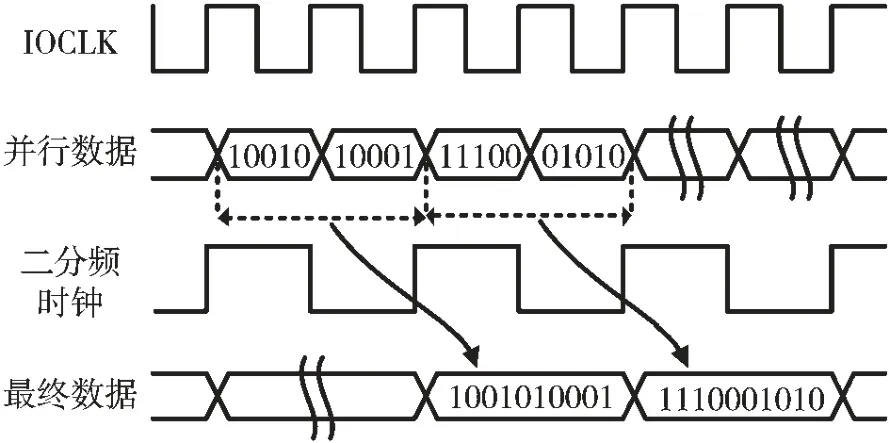

如图5 和图6 所示,当需要对串行数据1010110001进行10:1 的数据反序列化,可以分别对前5 位10101和后5 位进行5:1 比例的反序列化,最后将两次转化的数据进行拼接,即可完成10:1 比例的数据反序列化。利用SERDES 进行5:1 反序列化的电路连接图如图7所示。

图5 数据反序列化

图6 比例转换

图7 反序列化连接图

1.4 帧格式设计

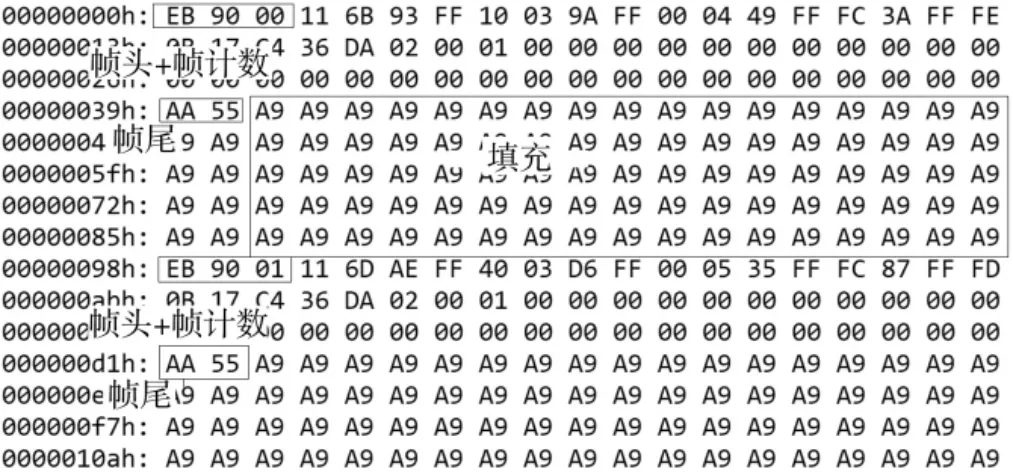

当传输串行数据时,LVDS 总线前端将并行数据序列化进行传输,串并转换单元需要将串行数据转换成并行数据,此时需要对数据进行对齐,即确定哪一位才是这一帧的第一位。通过LVDS 链路双方约定固定帧的方式来确定当前总线是否空闲和数据是否对齐完成。若当LVDS 总线初始化或空闲时,总线上的数据不为约定好的固定帧,则需要使能SERDES 的BITSLIP 信号[10],每使能一次,则相当于串行数据的起始位置向后顺延一位,直到并行数据与约定的固定帧一致时则表示数据对齐。固定帧首先考虑的0x55(0b0101010101)和0xAA(0b10101010),在经过8B/10B 编码后变成 0b1010101010和0b0101010101,虽然完美地实现了直流均衡和电平跳变,但是进行数据对齐时无法确定哪一位才是数据的起始位。本系统采用不断发送0xA9(0b1010100110),数据0xA9 进行8B/10B 编码后会变成0b1010100110,能够满足LVDS 传输时要求的直流均衡以及提供了足够的电平翻转。

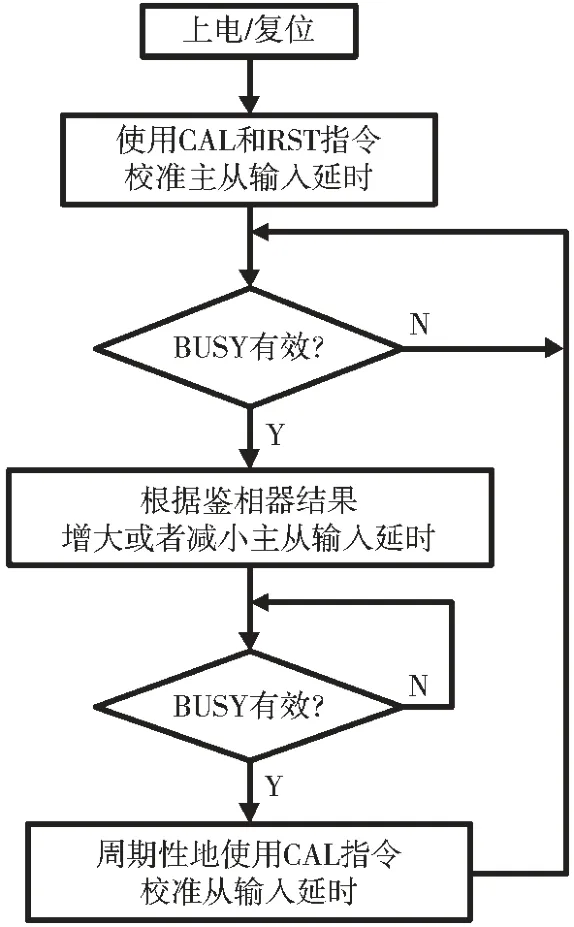

相位校准的基本流程如图8 所示,校准相位需要周期性地使能CAL,每使能一次,会经过28 个周期的校准时间,即每次校准最少需要28 个时钟周期。SPARTAN-6系列FPGA 内部IODELAY2 最多支持255 个TAP 的校准,一般调整相位只需要调整128 个TAP,所以最多只需要3 584 个时钟周期即可完成校准。在校准完成之前,LVDS 总线前端需要持续发送空闲数据。由于INCDEC信号只能指示当前数据和时钟的上升沿相位超前或者滞后,因此当校准成功后,INCDEC 会持续保持电平翻转的状态。所以当相位校准完成前,LVDS 总线需要一直发送空闲数据0x2A6,当完成校准后,才可以发送有效数据。

图8 相位校准的基本流程

1.5 以太网传输

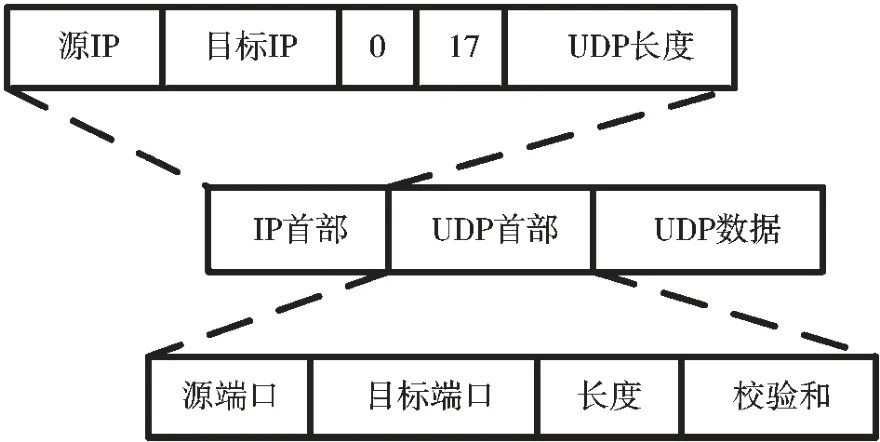

以太网传输采用UDP(用户数据报协议)传输,UDP是传输层的协议,是一种无连接的传输,在基本的IP 数据报服务至上增加了差错检测。相比于TCP 传输,UDP传输不需要在端系统维护连接状态,减少了不必要的开销,增大了传输速度[11-13]。UDP 通信的帧格式如图9所示。

图9 UDP 帧格式

PHY 芯片采用RTL8211EG,可以实现GMII 接口传输。FPGA 与PHY 芯片的连接如图10 所示,使用FPGA充当MAC 侧,控制PHY 芯片进行UDP 协议传输。在实际传输时将控制好的UDP 数据帧依次发送,FPGA 驱动TXC、TXD 和TXEN 向PC 端发送数据,数据格式必须满足UDP 通信数据格式,数据才能被PC 接收到,否则就会被网卡物理层丢弃[14-16]。

图10 FPGA 与PHY 连接图

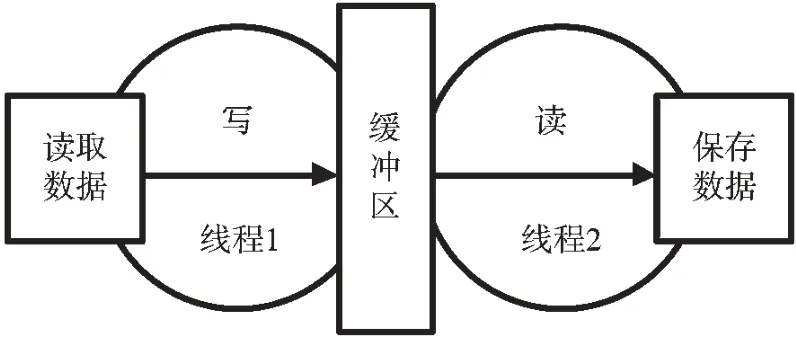

PC 接收端上位机采用Qt 框架C++语言编写,缓冲区设计采用4K 对齐,有效地提高存储速度。为了提高以太网接口的传输速度,上位机采用多个线程并设置了两个大容量缓冲区,缓冲区的设计如图11 所示,其中一个线程读取以太网中的数据并将数据保存在其中一个缓冲区中,当一个缓冲区存满之后,继续将数据保存在另一个缓冲区,另一个线程负责将存满数据的缓冲区写到文件中。两个线程同时工作,读取以太网的数据与写文件同时进行,有效地提高了传输速度。

图11 缓冲区设计

2 硬件测试

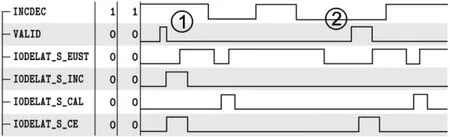

首先,使用Xilinx 公司提供的ICON 和ILA 两个IP 核进行测试,验证整个相位校准的流程。如图12 所示抓取的真实波形,根据图中标记①,当鉴相器VALID 信号拉高时,INCDEC 指示的相位状态有效。获取到当前数据和时钟的相位关系后,开始进行相位校准,使能IODELAY的CE 信号,并根据INCDEC 指示的状态控制IODELAY的INC 信号将信息传递给IODELAY,IODELAY 接收到相位信息则会进入BUSY 状态,当BUSY 拉低时,即可使能IODELAY 的CAL 信号,此时IODELAY 再次进入BUSY状态开始调整延迟,当BUSY 再次拉低时表示延迟调整完成。紧接着进入标记②的状态,延迟调整完成后鉴相器会再次指示调整之后的相位关系。从图中可以看到,在VALID 信号有效时,INCDEC 处于高低电平的跳变状态,此时相位的校准已然完成,实际的相位校准流程与图8 相符。

图12 相位校准的实际过程

接下来对系统进行硬件测试,连接时线缆采用双绞线。测试时LVDS 前端发送真实数据,首先需要发送空闲数据0xA9,当相位校准完成后再发送有效数据,保证LVDS 数据回读设备完成相位校准后再进行数据接收。由于数据回读设备内部的状态机首先进行相位校准,因此最开始的空闲数据不会被传输,如图13 所示,当有效数据传输开始时,LVDS 发送端数据的产生速度小于总线的传输速度,所以在传输的过程中会有等待填充数据产生。

图13 实际工程数据

3 结论

本文分别从硬件总体设计、模拟随路时钟的实现过程、校准数据和时钟相位关系的原理和实现过程以及通过提高SERDES 反串行化比例实现8B/10B 编码解决鉴相器失效的问题4 方面介绍了基于LVDS 的无随路时钟高速数据回读系统的设计与实现。通过对FPGA 内部信号的抓取可以直观地观察到校准模拟时钟和串行数据相位关系的过程,整个校准过程符合IODELAY 调整延迟的固有流程。通过对整个数据回读系统进行整体测试,读取码率为1 Gb/s 的LVDS 总线数据,前端数据为真实的工程数据,结果与程序设计一致。经过验证,通过数据回读设备板载时钟模拟LVDS 随路时钟、提高SERDES 反串行化比例实现8B/10B 编码和利用鉴相器将数据和时钟对齐的方式能有效地将无随路时钟的高速串行数据反序列化,去除掉LVDS 随路时钟,减少LVDS 总线的接口线缆数量,实现了一种接口数量少并且传输速度快的数据传输系统,为离线式数据存储系统的回读提供了一种传输速度快、灵活可靠和可移植性强的方案。