基于HVCMOS 工艺的H 桥驱动电路版图设计

2021-06-30焦继业马彩彩

李 芳,焦继业,马彩彩

(西安邮电大学 电子工程学院,陕西 西安 710121)

0 引言

CMOS 工艺具有低功耗、速度快、抗干扰能力强、高集成度、制程简单、成本低等优点,已成为低压模拟和数模混合集成电路的主流工艺技术[1]。为满足高压驱动应用领域的设计需求,在低压LVCMOS 工艺基础上发展出高压HVCMOS 工艺。其相比高压BCD(Bipolar-CMOSDMOS)工艺,可省去外加生长外延、埋层,且不必考虑不同型器件的兼容与工艺光刻版重复利用[2-4]。HVCMOS工艺的出现为低成本的H 桥驱动设计提供一条可行的技术途径。

在驱动应用设计中,器件导通高阻直接影响转换效率与驱动能力。因此,通常要求器件源漏导通内阻在毫欧级。实际上,器件源漏导通内阻既包括器件自身导通内阻,也有物理版图设计引入的寄生电阻(不同的封装形式也会造成不同的引线电阻)。H 桥的强驱动性能依赖于优良的后端物理版图设计。

物理版图是电路设计与制造的桥梁,影响设计性能与集成度[5]。本文从物理版图角度对H 桥驱动进行了优化设计,旨在满足H 桥驱动的高性价比应用需求。

1 H 桥驱动电路设计

1.1 H 桥基本构成

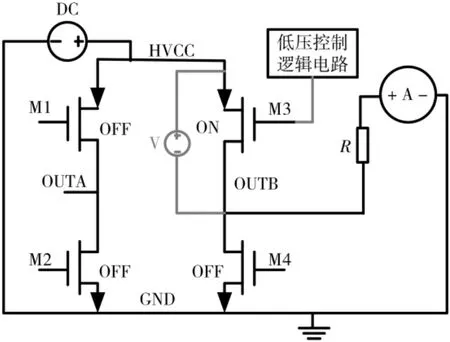

H 桥驱动电路结构形如字母“H”。根据器件源极电位不同可分为低端驱动和高端驱动。低端驱动器件源极接地,通常用NMOS 器件实现。当高端也采用NMOS 器件时,其源极为H 桥输出。为保证器件的导通状态,需采取额外的电荷泵、自举技术提高栅极电压[6]。但在高端采用PMOS 器件时,其源极电位为电源电压,栅极有低电压控制信号即可导通。为实现H 桥驱动设计的低复杂度,本文选择P-N 型H 桥结构[7],如图1 所示。

图1 P-NMOS H 桥结构

1.2 器件尺寸及导通RON

根据持续驱动电流@ 导通内阻(1 A@500 mΩ)设计指标,结合器件特征尺寸L,采用式(1)的典型方法确定器件尺寸[8]。

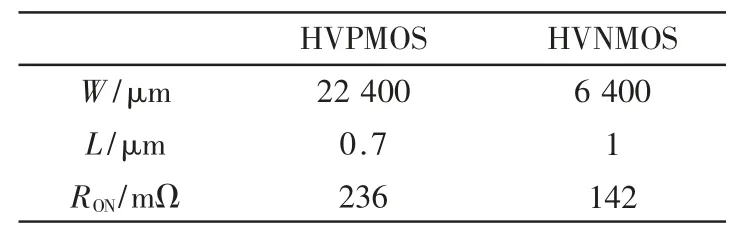

器件导通内阻RON与栅源控制电压VGS成负相关、工作温度T 成正相关。在电路设计阶段需要分析器件导通内阻RON极大情况。在低栅源信号VGS@ 高工作温度T条件(5 V@80℃)下模拟输出电流与导通内阻,最终确定H 桥器件尺寸及相应导通内阻RON如表1 所示。

表1 器件物理尺寸及导通内阻RON

2 H 桥驱动版图设计方案

为实现H 桥安培级驱动能力,桥臂器件形状设计特殊(大的W/L)。物理实现时将大尺寸器件拆分为多个小尺寸并联的插指结构[9],并在单插指器件宽度WF小于100 μm(WF=80 μm)条件下研究不同的源漏极互连线。

H 桥由完全相同的两半桥电路组成(I1/I2,I3/I4),因此可简化为对单侧如I1/I2 组成的半桥进行分析。以下为对不同源漏极互连线结构图示的两点说明:

(1)所选工艺金属层为4 层M1-M4。为减小物理面积,互连线集中于器件阵列有源区。金属M1 仅通过接触孔作为各器件源漏极有源区连接,不作为并联器件阵列间互连线。图示主要展现并联器件阵列互连线M2-M4。

(2)除去金属互连线,金属层间的接触孔也伴有寄生电阻。相邻两层金属层间的并联接触孔能够有效降低寄生电阻[10]。为便于直观分析,不同设计方案仅图示部分插指器件及其上分布的部分层间接触孔。

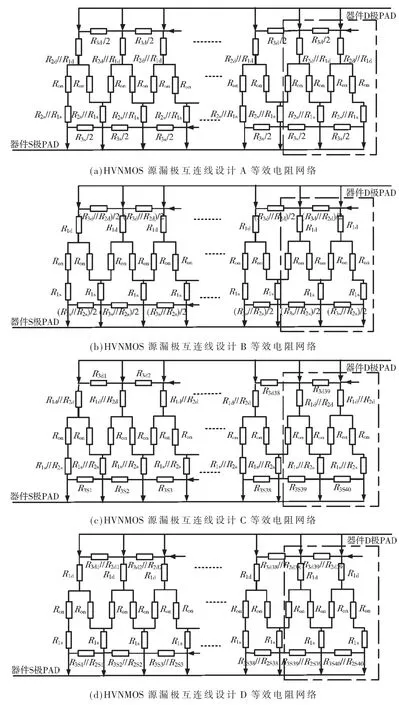

从形状和相对位置对互连线设计结构进行划分,如表2 所示。常规矩形互连结构简单便于修改。考虑到实际电流在流动过程发生变化,设计梯形互连结构有利于消除互连线衬偏。根据器件自有连线M1 与底层互连M2 相对位置的差异分为重叠与垂直结构。图2~图6 为不同互连线设计简化图示。

表2 源漏极互连线的组合设计方案

图2 金属图层M2-M4

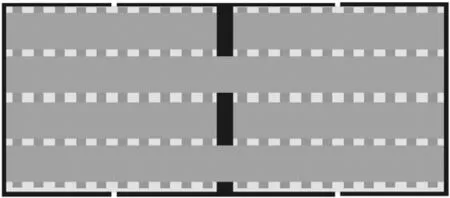

图3 半桥I1/I2 互连线设计方案A

图4 半桥I1/I2 互连线设计方案B

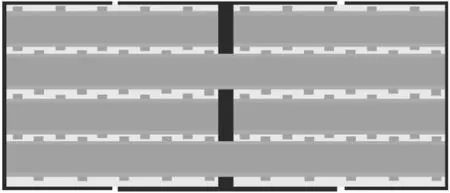

图5 半桥I1/I2 互连线设计方案C

图6 半桥I1/I2 互连线设计方案D

3 H 桥导通内阻验证

3.1 H 桥导通内阻评估

在物理设计中金属互连线均会引入寄生电阻[11]。通过构建简单、快速有效的方法对物理设计做出评估可提高设计效率。

寄生评估过程可采取分层分段步骤:先分离多层互连线以判断层间连接关系;其次确定单层寄生电阻;最后依据层间连接关系将各单层的寄生电阻进行串并联。因此,单层寄生电阻的精确评估很关键。

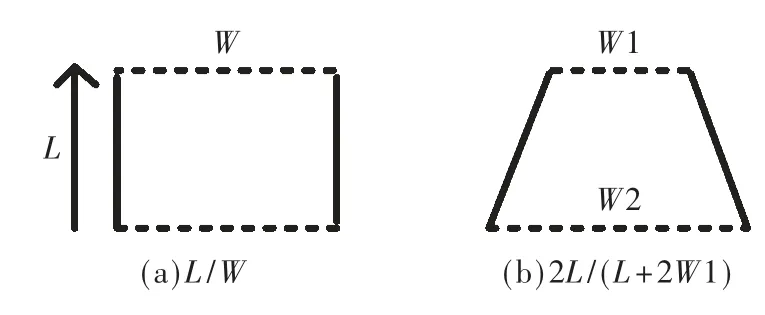

类矩形状的互连线形如设计A、B,其形状规整,有效长宽特征明显。但在实际设计中,综合物理因素限制,互连线会有非规整形状,如设计C、D 互连线为梯形。相关文献对此类非常规互连线有效长宽比进行了研究[12]。确定电流流向后的两种互连线结构有效长宽比如图7 所示。

图7 金属互连线的有效长宽比

在同种设计方案中高低端驱动I1/I2 布线(插指阵列右为I1,左为I2)相同。评估不同设计方案产生的源漏极导通电阻差异可简化为对半桥高端驱动I1 或低端驱动I2进行分析。互连线结构层间接触孔数目都是最大化,对器件实际导通电阻影响甚微,不会造成互连线设计之间的明显差异。为简化模型,在评估计算中忽略。

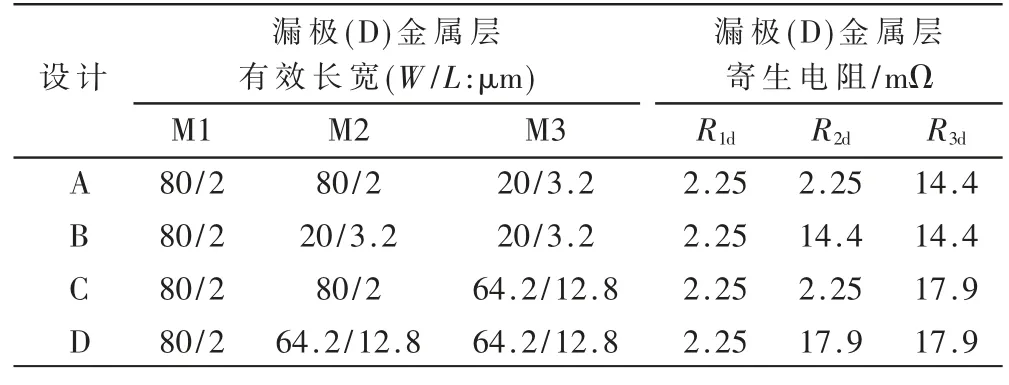

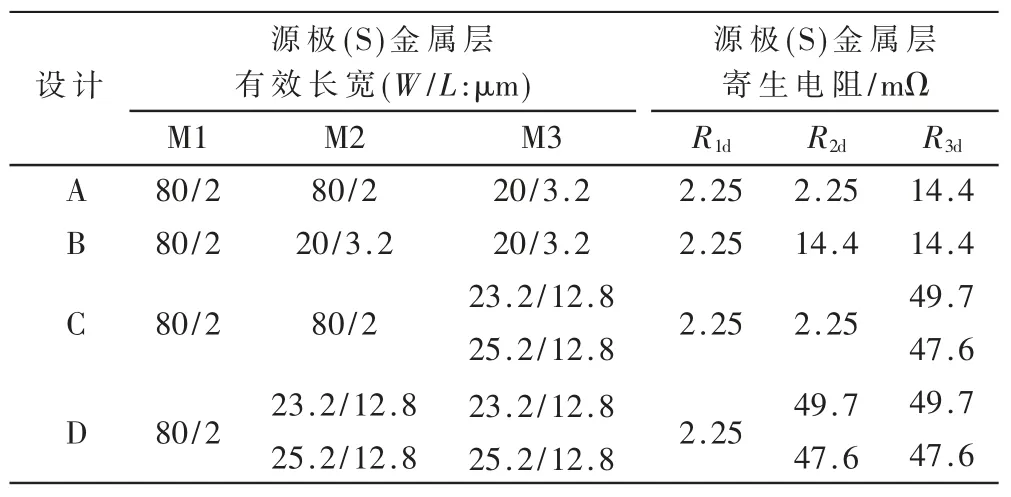

低端驱动I2(HVNMOS)插指阵列源漏导通内阻模型建立的具体内容:由器件导通内阻RON和各单层互连线寄生电阻构建树状电阻网络。图8 为互连线结构等效电阻网络。在不同设计方案中,源漏互连线M4各占器件阵列的一半面积,整体上是大块的金属。源漏极互连线M2-M3 会覆盖于整个器件阵列。为保证阵列器件互连线一致性以方便分析,电阻网络模型不包含互连线M4 寄生电阻。对于矩形互连线设计A、B中,源漏极高层互连线分别为两条并联,在相应的电阻网络中标注此部分横向电阻为Rnd/2、Rns/2,而且各小段寄生电阻为定量。对于梯形状设计C、D,金属互连线的各小段寄生电阻为变量。

基于互连线插指阵列的高度对称性和重复模式对相应的等效电阻网络简化分析。在图8 中,HVNMOS 每一种互连线树状电阻网络均可以等效为四插指结构单位组(虚线框所示)的若干等效电阻并联。结合各金属互连层方块阻值Rsq(0.09 Ω)及互连线有效长宽(L/W),就可确定互连线源漏极寄生电阻Rns和Rnd,结果如表3 和表4 所示。

表3 HVNMOS 四插指漏极互连线结构的RD

表4 HVNMOS 四插指源极互连线结构的RS

图8 HVNMOS 源漏极互连线设计等效电阻网络

前仿真低端HVNMOS(W/L=6 400/1)在VGS@IDS(5 V@1 A)导通内阻RON为142 mΩ,故单插指器件(WF/L=80/1)在5 V@12.5 mA 的导通内阻RON为11.36 Ω。将单插指器件的导通内阻和不同互连线寄生电阻代入等效电阻网络模型,采用串并联、三角形-星形电阻等效转化技术可计算器件实际导通内阻。

3.2 H 桥导通内阻仿真

为验证评估方案的正确性,对四种设计方案进行具体设计,如图9~图12 所示,并保持与电路设计相同仿真条件VGS@IDS(5 V@1 A)进行带寄生参数仿真。表5 为理论评估计算与仿真对四种设计方案导通内阻差异性判断。两种方法结论一致,金属M2 与M1 垂直、顶层金属M3 梯形状的互连结构能够提高互连线沿电流流向的有效长宽比,降低寄生电阻。

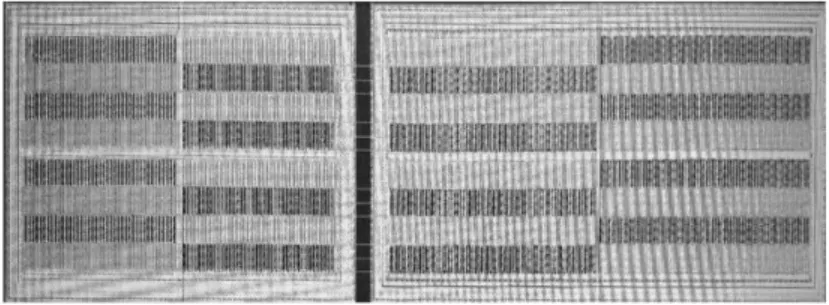

图9 半桥I1/I2 互连线设计方案A

图10 半桥I1/I2 互连线设计方案B

图11 半桥I1/I2 互连线设计方案C

图12 半桥I1/I2 互连线设计方案D

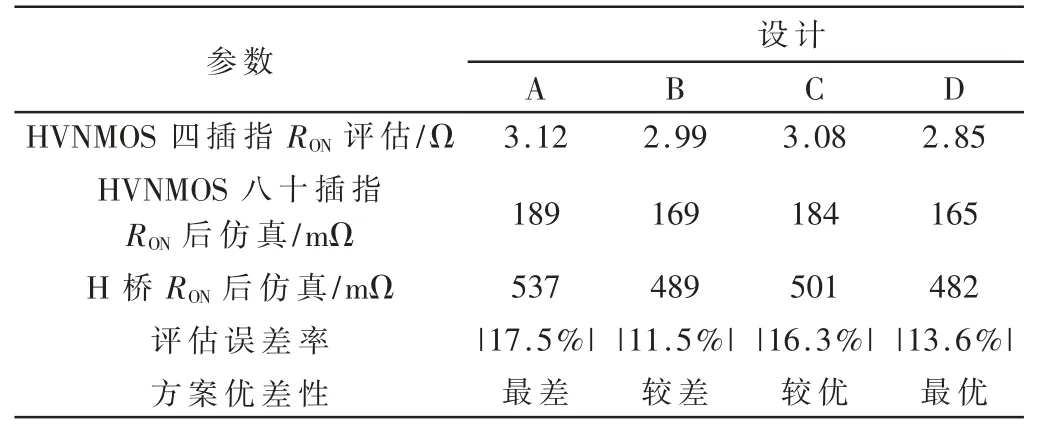

表5 不同互连线设计结构的RON

在表6 中列举了器件并联阵列互连线RON评估方法对比。本文建立的树状电阻评估方法虽与相关文献采取的有限元FEM 法相比误差率存在一定的差距,但可实现在设计前期对不同互连线结构进行差异性分析,不必依赖设计完成的后仿真优化。基于电流流向对不同形状互连线有效长宽比的识别提高了评估方法的合理性,而且对设计方案优差性判断与仿真结论一致,说明了评估方法的可行性。

表6 器件并联阵列互连线RON 评估方法对比

3.3 H 桥导通内阻测试

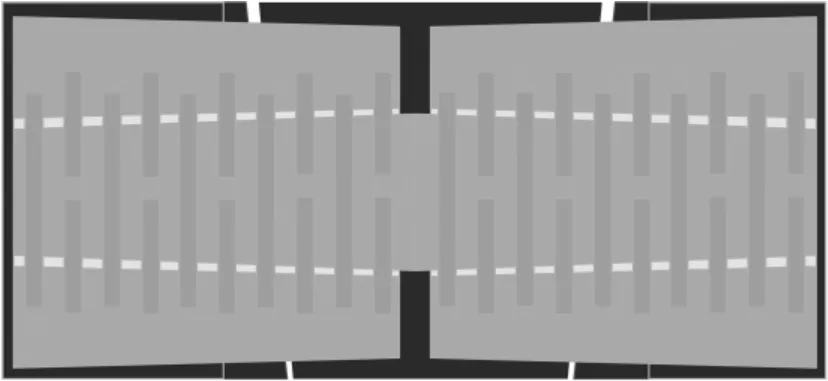

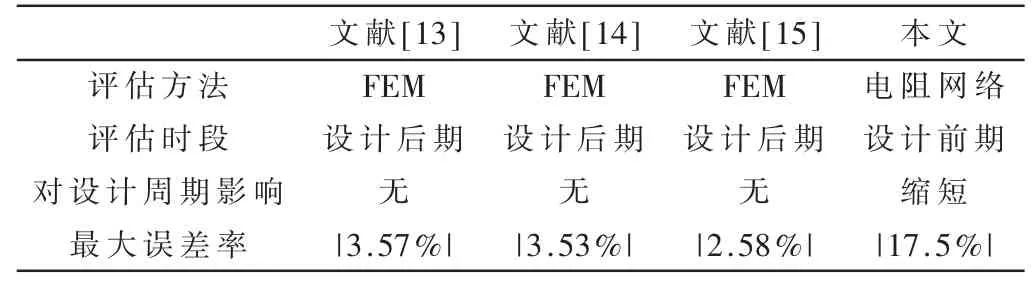

为提高集成度、增强通用性,将H 桥驱动及其栅极控制逻辑电路集成于SoC 系统。根据设计前期对不同互连线设计评估和仿真结果,将较优设计B、D 集成于SoC系统进行COB 封装流片测试验证。图13 为集成有设计B、D 相应的SEM 图。

图13 互连线设计

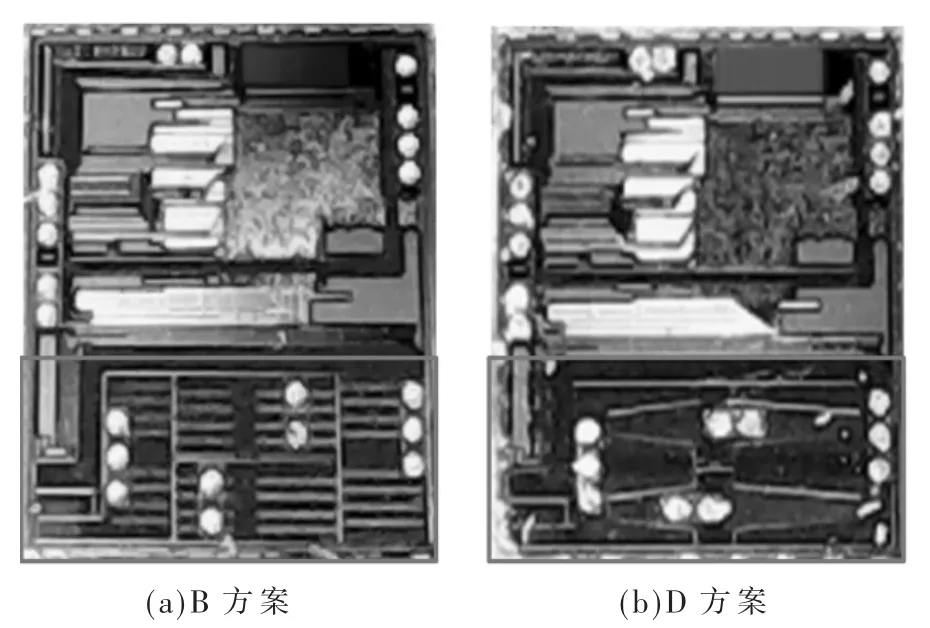

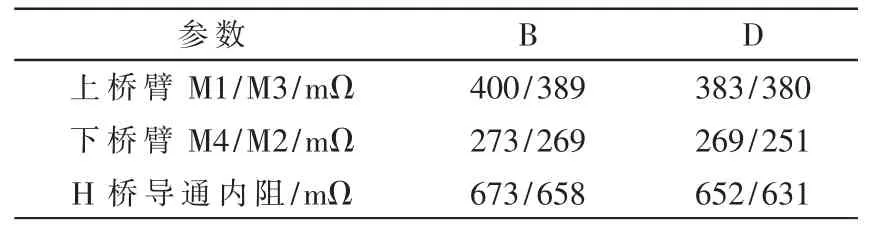

H 桥的导通内阻为毫欧级,对于测试方法中引入寄生电阻误差异常敏感[16]。本文在测试方法选取直接欧姆测量。直接测量导通器件源漏极电压,结合回路中电流即可得到器件导通内阻。为保证测量结果的准确性,对每个器件导通内阻进行多次测量取平均,测试条件保持与仿真条件一致。图14 为上桥臂HVPMOS 的测试方法,对于HVNMOS 方法类似。最终完成实测结果如表7 所示。

图14 HVPMOS 导通内阻测试原理

表7 集成于SoC 芯片的H 桥导通内阻测试结果

测试结果与设计前期的评估、仿真结论一致,互连线设计D 相比设计B 产生更小的寄生电阻,H 桥的驱动性能更强。但在相同的设计中,测试、仿真与预期指标存在差距。差距主要来源于芯片的焊盘接口和测试引脚之间的引线寄生电阻。后续可以选择集成封装进行进一步验证。

4 结论

本文基于制程简单、灵活易兼容的HVCMOS 工艺,实现H 桥驱动优化设计。通过优化器件并联阵列源漏极互连线,降低非理想寄生电阻,提高H 桥驱动性能。同时,建立的互连线评估模型可在设计前对物理版图设计方案进行优差性分析,不必依赖设计后仿真,从而提高设计效率,保证物理版图的高效高质完成。

值得注意的是,物理寄生参量既取决于互连线设计结构,也与工艺金属层方块电阻条件相关。本文在特定工艺下研究了不同互连线设计结构。基于其他工艺条件下互连结构的寄生结论可能存在差异,但本文的研究方法仍具有一定参考价值。