基于AXI 总线的可配置LVDS 控制器设计与验证*

2021-06-30蒙宇霆袁海英

蒙宇霆,袁海英,丁 冬

(北京工业大学 信息学部微电子学院,北京 100124)

0 引言

复杂电子系统设计对数据传输速率的要求日益严格,也带来高功耗、高成本等问题,低压差分信号(LVDS)[1]是一种高性能数据传输技术,它是速度、成本和功耗之间的最佳折中方案。在物理层电路设计方面,LVDS 的低压摆幅(250 mV~450 mV)和快速过渡时间可以使数据传输速率达到100 Mb/s~3 Gb/s,能够满足现代复杂系统设计中对数据传输的需求。此外,这种低压摆幅可以降低功耗消散,具备差分远距离传输[2]的优点。在当今大量数据传输的诸多场景中,如芯片间的信息传输[3-4]、视频图像处理[5-6]、光通信[7]和LCD 面板[8]等,LVDS 已成为最有前景的解决方案之一。在数字逻辑功能设计方面,由于需求、协议和应用场景的差异[9-10],设计人员存在大量重复性的设计、调试工作。为提高系统开发效率,解决平台间的兼容性问题,通常在FPGA 平台上实现LVDS高速接口设计[11-13],文献[11]在FPGA 上实现了LVDS 总线控制器,解决了多节点高速通信的故障隔离问题;文献[12]实现了LVDS 接口的收发单元设计,在收发通路中加入数据与时钟对齐机制,提高了平台兼容性,并在FPGA 上验证了方案。文献[14]通过FPGA 设计了一种基于LVDS 接口的高速并行数据传输系统,并应用于实际专用网络交换模块。在实际芯片工程中,考虑到当LVDS控制器集成到SoC 系统上时存在兼容性问题,软硬件间应有更高的操作灵活度,系统各模块间数据传输应高速稳定。因此,为了提高系统可靠性,降低成本,设计一种高灵活度、高性能的LVDS 控制器具有很高的价值。

本文设计的控制器主要用于由摄像头采集而来的数据与内存的交互,更加关注逻辑功能的实现。基于APB 总线的可配置通路可通过配置寄存器按照自定义协议传输数据,在数据读写方面选择AXI 总线以提高数据传输速率,针对数据传输过程中常见的丢数等错误,在收发通路中加入了检查模块,实现了更加灵活准确的数据传输功能。

1 LVDS 控制器设计方案

1.1 LVDS 控制器总体结构

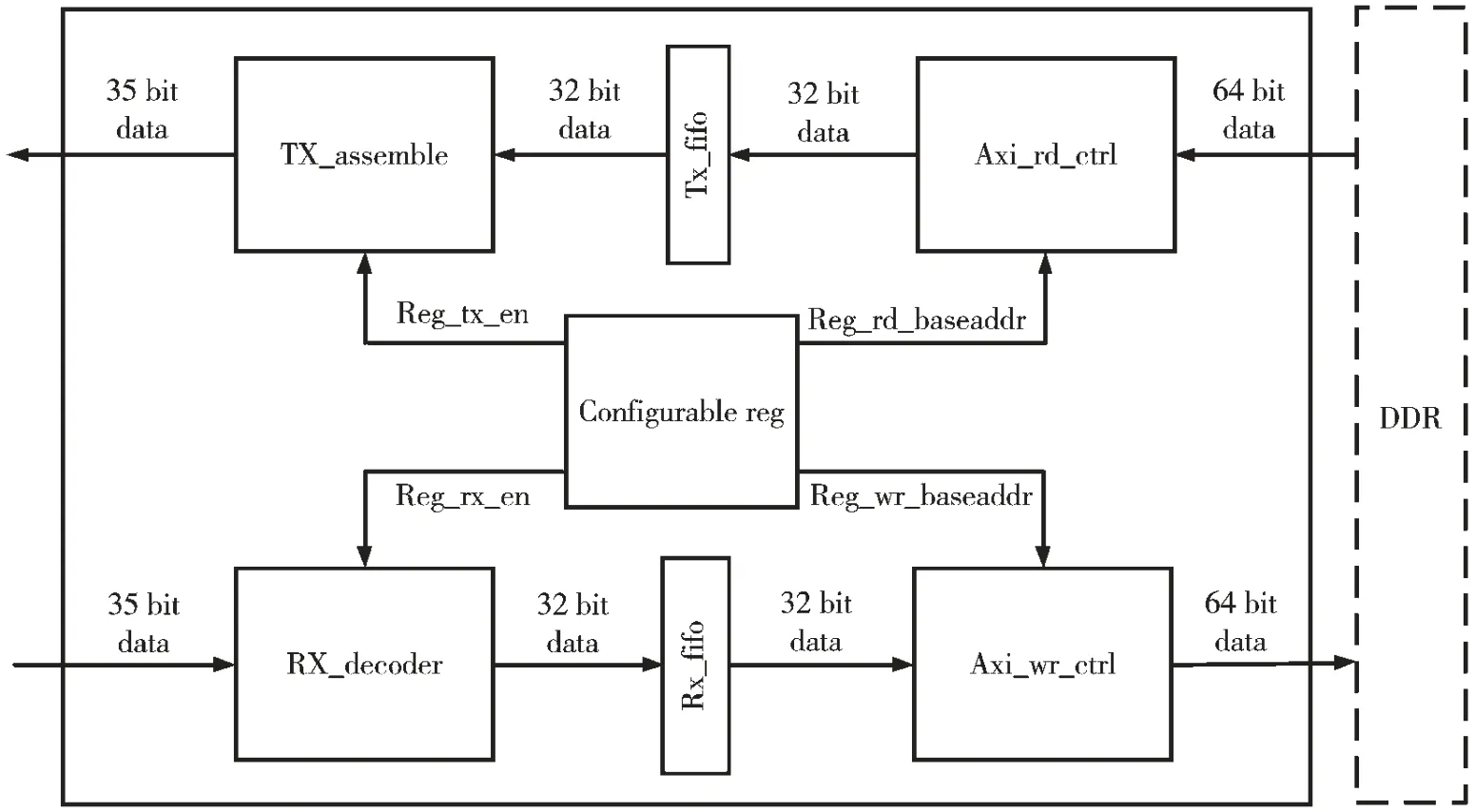

基于AXI 总线的LVDS 控制器总体结构设计如图1所示,该控制器的数据流以及主要控制寄存器信号展示在图中。电路内部主要由Rx_decoder、Tx_assemble、Axi_wr_ctrl、Axi_rd_ctrl、Configurable_reg 等模块组成。为了在SoC 系统中利用软件控制数据传输,加入了基于APB 总线接口的可配置模块Configurable_reg,用于提供与CPU交互的接口,可通过APB 配置通路配置寄存器来控制LVDS 模块收发数据帧。

图1 LVDS 总体结构

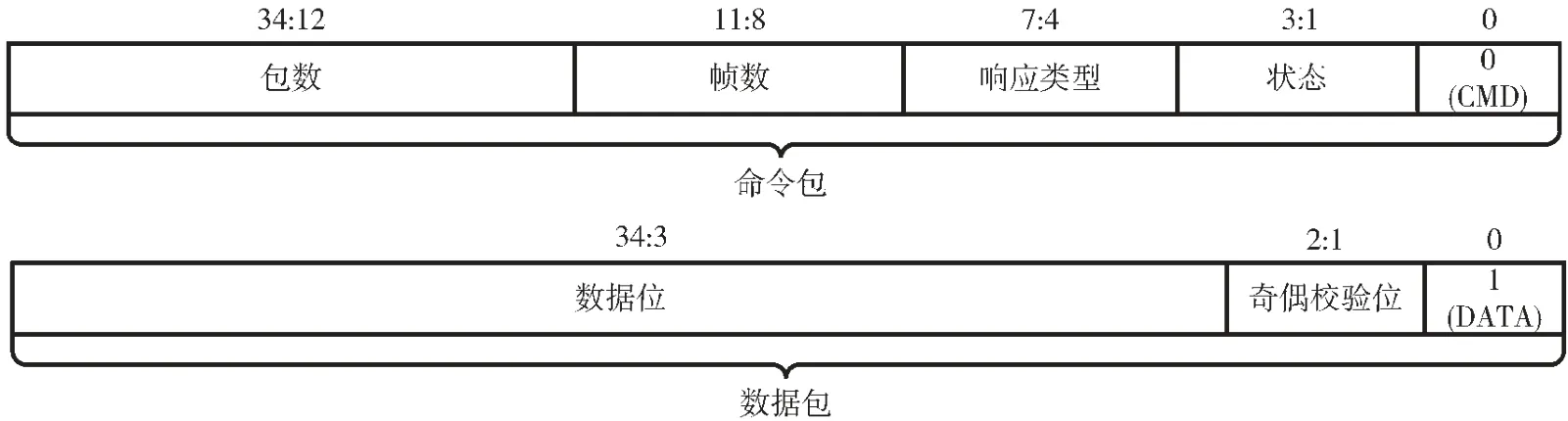

为了灵活地控制数据传输,本文自定义了一种数据接收和发送的协议:数据是帧的形式传输,帧由命令包和数据包构成,如图2 所示。命令包中包含了状态、响应类型、帧数以及包数等字段。在数据接收过程中,Configurable_reg 模块的使能寄存器Reg_rx_en 会控制是否接收数据。若将Reg_rx_en 配置为1,模块Rx_decoder 将收到的第一个35 位命令包进行解析,若Rx_decoder 模块检测到FRAME_START 状态,则开始接收数据。接下来收到数据包,为确保数据正确传输,35 位数据包中带有两位奇偶校验位,最低位是1,表示此时接收的是数据包,最高32 位是数据字段。最后收到带结束状态FRAME_END 的CMD 命令包。相应地,数据发送使能由Configurable_reg 模块的寄存器Reg_tx_en 控制,Tx_assemble 模块则会将数据按照自定义的协议封装、打包、发送出去。

图2 数据传输格式

1.2 数据接收控制逻辑

数据接收流程:LVDS 控制器接收到对端设备的数据帧,由Rx_decoder 模块进行解析后,将数据传输到Axi_wr_ctrl 控制模块。考虑到这两个模块在数据传输过程中时钟域不一致,采用异步FIFO 做跨时钟域处理。Axi_wr_ctrl 模块将接收到的32 位数据转化为64 位数据,并通过Axi 总线将其送到DDR 中。数据发送通路中的主要功能模块介绍如下。

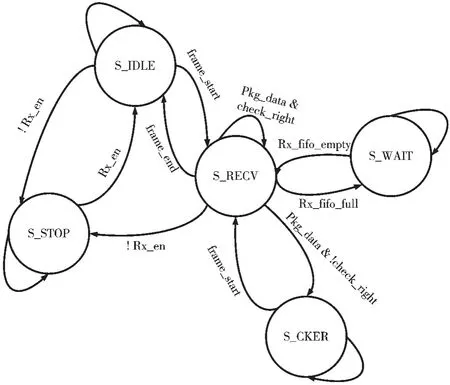

Rx_decoder 模块的作用是解析对端设备传来的数据帧中的命令包,并检查数据包是否出错,它的控制状态机如图3 所示,分别有S_IDLE、S_RECV、S_CKER、S_WAIT和S_STOP 五个状态。S_IDLE 表示此时没有数据帧正在接收,可以接收新的数据帧。当收到CMD 命令包的帧头开始信号。

图3 Rx_decoder 模块状态机

frame_start 时,会从S_IDLE 状态跳到S_RECV 状态,此时开始接收数据。为了避免在接收过程中发生数据丢失或数据传输错误的现象,增加了S_WAIT 和S_CKER 两个状态。当Rx_fifo_full 信号置1 时,表示此时接收FIFO是满状态,状态机从S_RECV 跳转到S_WAIT,等待接收FIFO 为空时再由S_WAIT 跳回S_RECV 继续接收数据。

当奇偶校验检查到数据不一致时,状态机会从S_RECV状态跳转到S_CKER 状态,在S_CKER 状态意味着数据传输发生错误,需要等待重新开始的信号,如果此时收到了frame_start 信号,表示要接收新的数据帧,因此状态机从S_CKER 跳转到S_RECV。每进来一个数据包都会进行奇偶校验检查,检查正确则会继续传入剩余的数据包,直到收到CMD 命令包的帧尾结束信号frame_end,状态机从S_RECV 状态跳转到S_IDLE 状态,表示完成了这一帧数据的接收。CPU 中断是最高优先级,不论在空闲状态S_IDLE 还是S_RECV 数据接收状态,当Rx_en 寄存器为0 时,会直接从S_IDLE 状态或S_RECV 状态跳到S_STOP 状态。

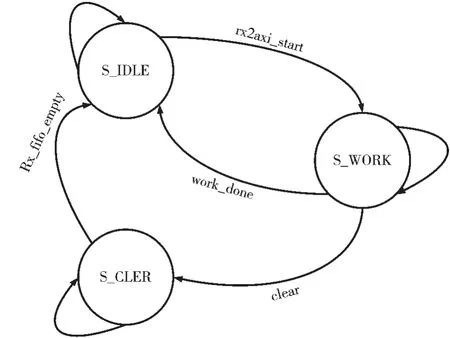

Axi_wr_ctrl 模块用来控制从Rx_decoder 模块接收的数据通过AXI 写通道写到DDR,其控制状态机如图4所示,包括S_IDLE、S_WORK 和S_CLER 三个状态。状态机是否工作取决于rx2axi_start 和work_done 两个信号,这两个信号是Rx_decoder 模块检测到开始标志和结束标志时传到Axi_wr_ctrl 模块的控制信号。当rx2axi_start置1 时,由S_IDLE 状态跳转到S_WORK 状态,S_WORK状态下会将进来的32 位数据整合为64 位数据并送到AXI 写通道,按照AXI 协议控制数据写到DDR 中。如果AXI 写回应通道发生错误响应,clear 信号会置1,状态机由S_WORK 状态跳转到S_CKER 状态,在S_CKER 状态下,会将此时FIFO 里的数据全部清除,清除完毕后跳转到S_IDLE 状态,等待rx2axi_start 置1 时重新开始传输。此外,为了更加灵活地配置AXI 的功能,在Axi_wr_ctrl 模块中加了两个可配置寄存器用于改变AXI 通道中每次突发传输数据的个数和写入DDR 的起始地址。

图4 Axi_wr_ctrl 模块状态机

1.3 数据发送控制逻辑

数据发送流程:Axi_rd_ctrl 模块接收到来自DDR controller 的数据流后,开始进行数据位宽转换,经过异步FIFO 的跨时钟域处理,送到TX_assemble 模块将数据进行打包,再发送到对端设备。数据发送通路中的主要功能模块介绍如下。

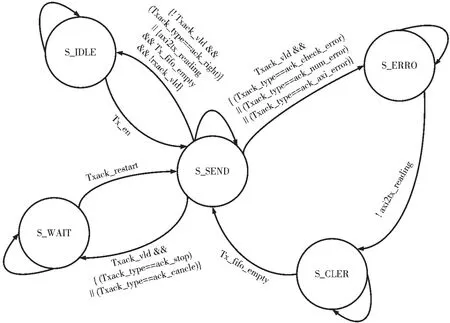

Tx_assemble 模块的功能由状态机控制,如图5 所示,分别有S_IDLE、S_SEND、S_ERRO、S_CLER 和S_WAIT 这5 个状态。S_IDLE 表示此时没有数据帧正在发送,当CPU 要发送数据的时候,会配置Tx_en 寄存器为1,从S_IDLE 状态跳转到S_SEND 状态。同时,Tx_assemble 模块会生成控制信号并通过握手协议发送到Axi_rd_ctrl 模块。S_SEND 状态表示即将发送数据。根据自定义协议,每个35 位的命令包中包含要发送的帧数、包数、响应类型和状态信息,Tx_assemble 模块会用计数器来统计发送的帧数、包数及状态信息,然后将这些信息打包。每个35 位数据包中包含32 位数据、2 位奇偶校验位及1 位说明位(指明是数据还是命令)。最后Tx_assemble 模块将命令包和数据包合并为数据帧由状态机控制发送。

图5 TX_assemble 模块状态机

Axi_rd_ctrl 模块接收来自Tx_assemble 模块的命令并把当前状态信息返回Tx_assemble 模块。若Tx_assemble模块开始发送数据的同时向Axi_rd_ctrl 模块发送读控制信号,那么Axi_rd_ctrl 模块将会通过AXI 读通道从DDR读出数据并写入读FIFO 中。为了灵活配置,Axi_rd_ctrl模块也包含了可配置寄存器来设置axi 起始的读地址和突发式读写的数据数量。

2 LVDS 控制器仿真验证

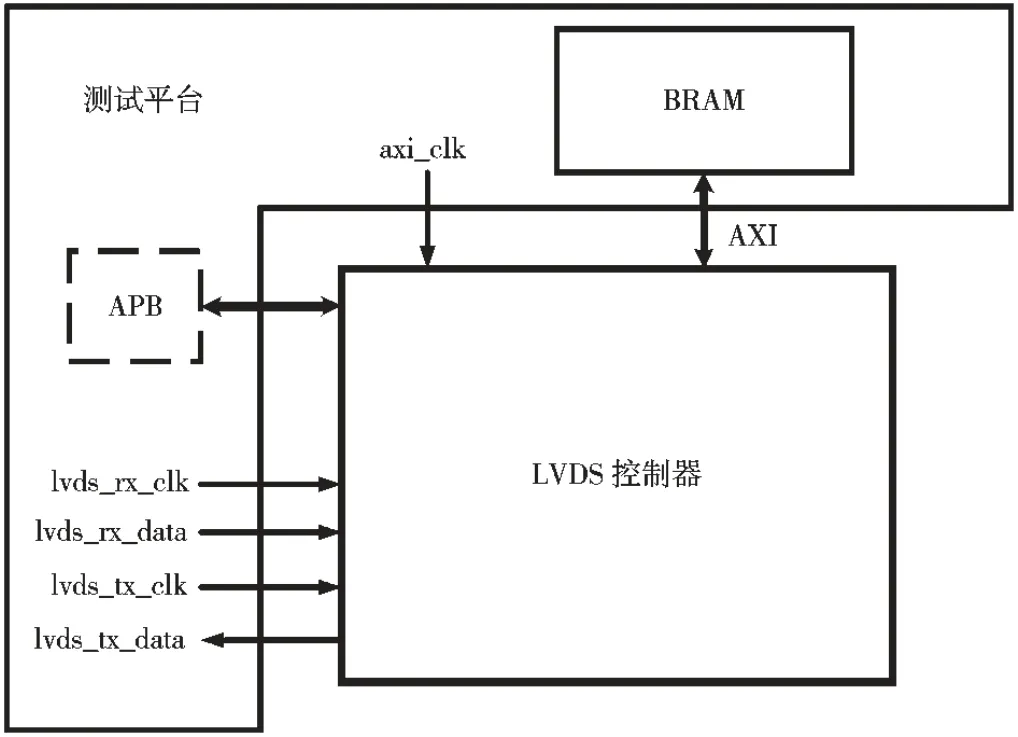

为验证本文提出的LVDS 控制器设计方案,搭建如图6 所示的测试平台,利用Synopsys 公司的仿真软件VCS 和Verdi 进行功能仿真验证。测试平台的主要功能包括:提供与LVDS 控制器进行数据交互的BRAM(模块级验证用BRAM 代替DDR);为验证APB 总线配置寄存器功能,根据APB 总线协议生成可配置环境;根据自定义的LVDS 控制器收发协议,在测试平台内生成完整的数据帧,包括数据包和命令包等;将所有测试平台所需的环境以及待测的LVDS 控制器集成,构建完整的验证环境。

图6 LVDS 控制器的测试平台

为了简化复杂的验证过程,考虑到LVDS 控制器特有的收发通路,提出了一个高效的验证方案:在验证平台上根据自定义协议配置环境,向LVDS 控制器发送完整的数据帧,数据由LVDS 控制器的接收通路收到之后通过AXI 接口写入BRAM,此时再利用验证平台的APB环境通过配置寄存器将存到BRAM 里的数据帧读出,由发送通路发送回验证平台,验证平台将发送出去的数据帧和收到的数据帧进行比对,最后给出验证结果。根据上述验证方案,将验证流程分为以下三部分:

(1)验证LVDS 控制器配置通路

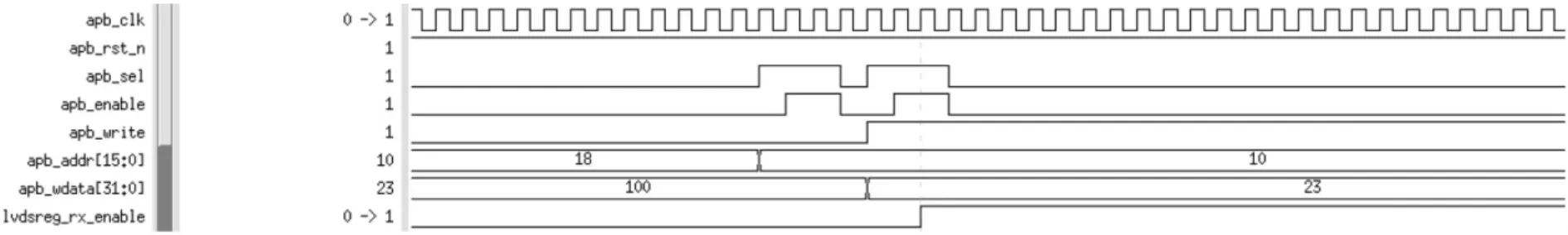

通过APB 总线接口完成初始配置,设置收发数据包数量、AXI 总线突发式读写的数据数量和DDR 的基地址。仿真波形如图7 所示,APB 通道分别对6 个地址进行读写,对应下面6 组寄存器改变为相应的值,表明APB 配置通路功能正确,能按照标准APB 协议对可配置寄存器进行读写操作。

图7 APB 配置通路波形

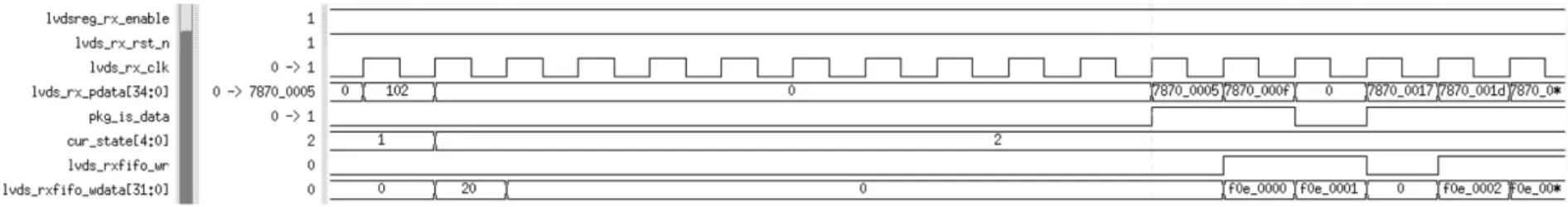

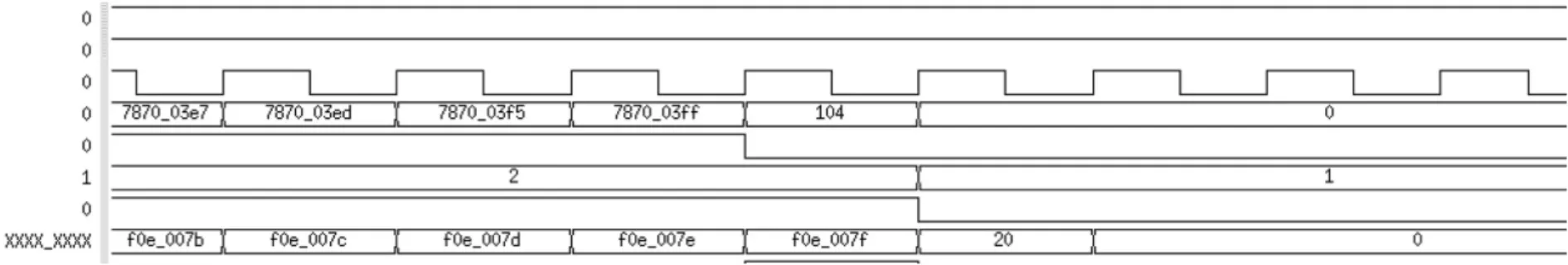

(2)验证LVDS 控制器接收通路

完成APB 配置通路的初始化后,将验证平台生成的数据帧按照自定义协议由lvds_rx_data 输入端口发送到LVDS 控制器,发送数据帧前先通过配置通路配置lvds_rx_enable 寄存器,将接收通路的使能信号打开,其仿真波形如图8 所示。APB总线地址0x10 的第一位写入1 之后,lvds_rx_enable 信号被拉高,这意味着接收通路将要接收数据。随后,lvds_rx_data 输入端口收到数据帧的帧头,即图9 中lvds_rx_pdata信号的0x102,根据之前命令包的定义,0x102 表示发送的帧数为一帧,此包类型为开始状态。接收到开始命令包后,等待10 个周期再开始接收128 个数据包。数据包接收完之后紧接着接收到帧尾命令包,即图10 中lvds_rx_pdata 信号的0x104。接收过程中,接收通路的Rx_decoder 模块会控制异步FIFO 和Axi_wr_ctrl 模块将128 个32 位数据合并为64 个64 位数据写到BRAM 中。图11 显示,接收到的数据通过AXI 写通道全部写入BRAM 里,说明接收通路功能实现正确。

图8 配置lvds_rx_enable 寄存器波形图

图9 帧头波形

图10 帧尾波形

图11 写入BRAM 的数据波形

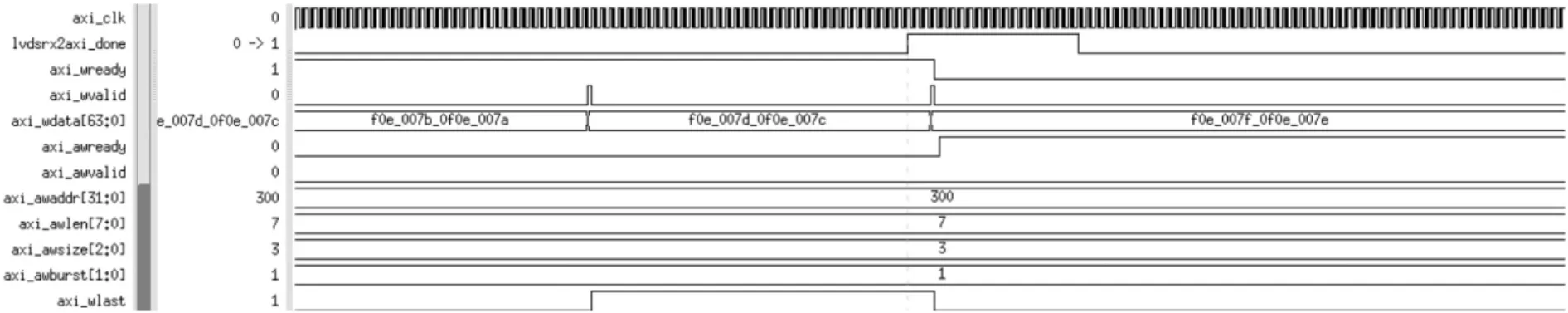

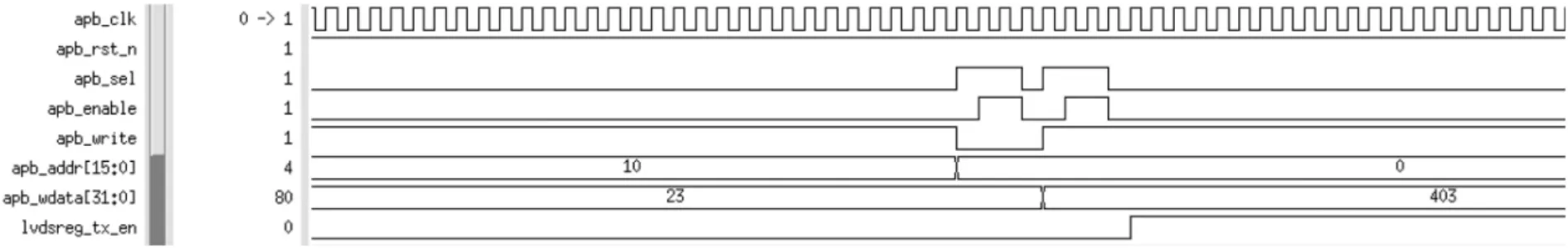

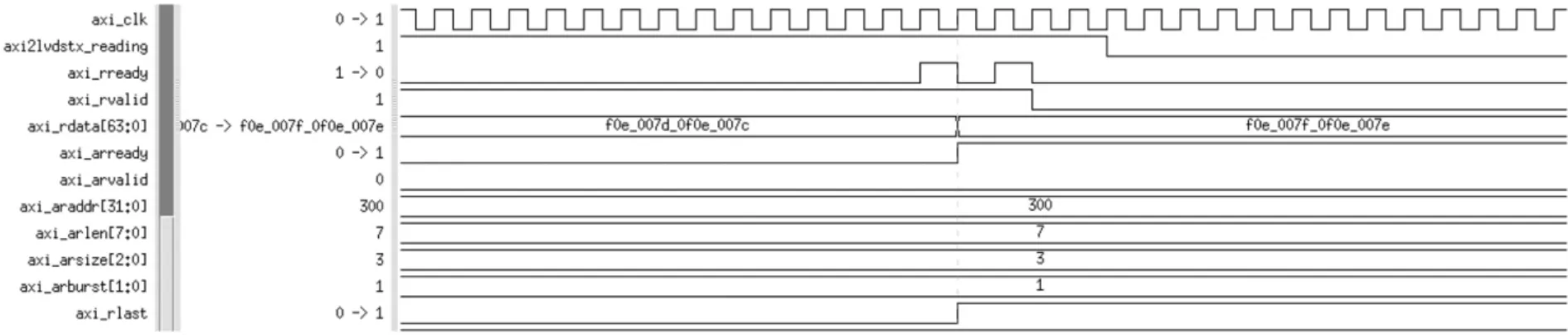

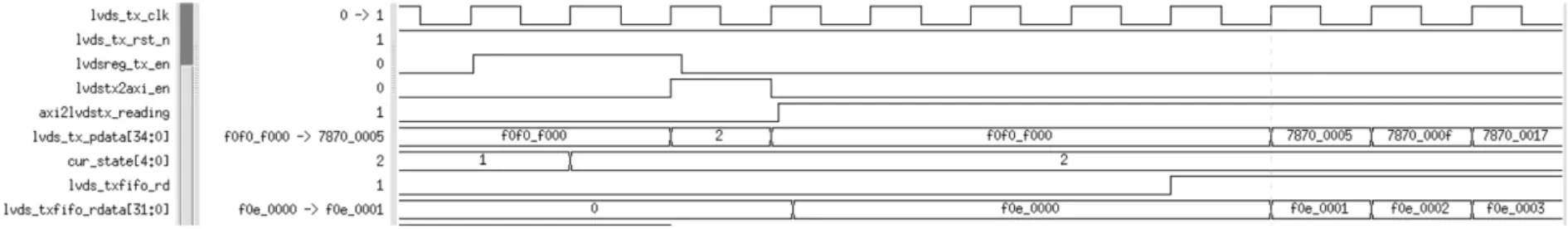

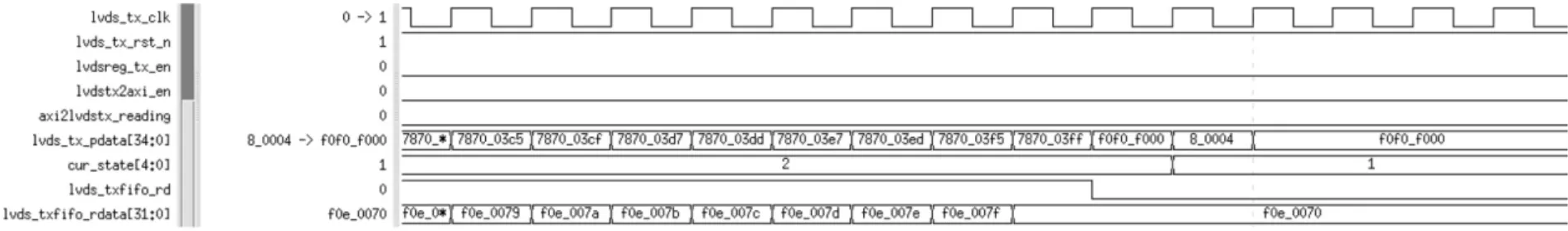

(3)验证LVDS 控制器发送通路

根据所述验证方案,首先通过配置通路配置lvds_tx_en寄存器将发送通路的使能信号打开,仿真波形如图12 所示。APB 总线地址0x00 的第一位写入1 之后,lvds_tx_en信号被拉高,这意味着发送通路将要发送数据。随后,Tx_assemble 模块发送控制信号控制Axi_rd_ctrl 模块和异步FIFO,Axi_rd_ctrl 模块先将64 个64 位数据转化为128 个32 位数据,再经过异步FIFO 发送到Tx_assemble模块中,最后,Tx_assemble 模块将接收到的数据打包发回验证平台。图13 显示,Axi_rd_ctrl 模块通过AXI 读通道将BRAM 中的数据读出。由图14 和图15 可见,Tx_assemble 模块将帧头、数据帧和帧尾发送回验证平台,且验证平台发出的数据与收到的数据一致,故发送通路功能实现正确。

图12 配置lvds_tx_en 寄存器波形图

图13 读出BRAM 的数据波形

图14 帧头波形

图15 帧尾波形

3 结论

本文设计了一种基于AXI 总线的可配置LVDS 控制器,可通过APB 总线配置寄存器按照自定义协议收发数据,具有与内存交互的AXI 高速总线通道,满足高性能数据传输需求。最后,针对该控制器的接收通路和发送通路提出了高效的验证方案。验证结果表明该控制器可以在SoC 系统上使用自定义协议高效无误地进行数据传输。该设计方案已经集成到基于ARM 的SoC 上并完成了系统级验证,验证过程充分体现了软硬件协同工作的灵活性。LVDS 控制器内部工作时钟频率为50 MHz,外部串并转换通道时钟为350 MHz,满足视频数据传输需求;当LVDS 控制器在更高时钟频率下工作时,可通过改善电路设计进一步提升数据传输效率。