基于代码反汇编的电路板测试方法研究

2021-06-27袁荣刘良勇李金猛

袁荣,刘良勇,李金猛

(国营芜湖机械厂,安徽芜湖 240007)

传统软件要正确在某一平台上运行,则应遵循该平台的一个基本约定。此约定在上层或正向的高级语言开发中不体现,但是在底层汇编级正向或逆向开发中必须严格遵循,这一约定被称为ABI(应用二进制接口),ABI 规定了寄存器用途,调用栈结构。嵌入式系统软件除了具备上层应用软件的所有特征,还体现在硬件的紧密关联上,嵌入式软件源码经过编译链接后的源码无法运行在其他硬件平台上,甚至在使用相同处理器的其他平台也无法运行,这是嵌入式软件复杂性的直接体现[1]。

近年来,航空电子产品发展快速,模块化、组件化、数字化程度不断提高,板件中集成了大量可编程器件,在航电维修过程中,部分板件没有资料,在对硬件理解的基础上并不能掌握板件的工作原理和工作流程,提出了一种利用反汇编的方法对嵌入式板件进行工作流程梳理。

1 反汇编方法研究

利用芯片公司的IDA 软件开展电路板的在线软件代码读取和备份,利用反编译工具反编译软件代码[2],得到各个模块对应的汇编文件,对汇编文件进行分析,主要内容为对模块的初始化、数据流向、硬件空间地址分配进行分析[3],形成数据流程图和模块框图。

1.1 形成数据流程

分析反编译出来的汇编文件[4]、芯片与外设间的数据交互过程,结合硬件空间地址,形成boot 的启动流程以及模块间的数据交互流程[5]。某型电路板反编译后分析的数据流程如图1所示。

图1 某型电路板通过反汇编分析的程序流程图

1.2 模块划分

结合硬件空间地址分配和boot 启动流程[6],分析出嵌入式板卡的大致模块划分情况[7],某型待测电路板划分后的情况如图2 所示。

图2 某型电路板模块划分

2 测试硬件设计

测试平台系统为待测板卡提供一个信号检测、信号激励与仿真、电源供电等资源的通用平台,针对被测板卡提供通用的测试板卡,并提供适配的转接板。

机箱中集成了电源、通用测试板卡、仿真器,电源采用长峰的直流电源,提供±12 V,±5 V 的电压,测试板卡提供了GPIO、通用测试口、串口、LVDS、可编程时钟、ADC、DAC、VGA 接口等资源,仿真器提供了Xilinx-FPGA/CPLD、TI-DSP、ADI-ARM 仿真器。方案框图如图3 所示。

图3 系统方案框图

2.1 板卡方案

通用测试板卡为待测板卡提供适配的GPIO、串口、时钟、LVDS、AD/DA 等资源,将常见的串口、USB、LVDS 接口等集中到板卡上,并通过转接板与待测模块进行匹配,板卡设计方案如图4 所示。

图4 板卡设计方案

2.2 测试主板硬件设计

测试主板的硬件设计框图如图5 所示。

图5 测试主板硬件框图

2.2.1 FPGA芯片

主要FPGA 是XC7K325T-2FFG900I。

2.2.2 电源设计

电源芯片使用ADI 公司的LTM4644,将5 V 电压转化成1.0 V、1.8 V 和3.3 V。LTM4644 是一个四路DC/DC 降压型且单路输出4 A 的μModule 稳压器[8],内含开关控制器、功率FET、电感器和支持组件。在4~14 V 或2.375~14 V 的输入电压范围内支持0.6~5.5 V 的输出电压范围[9]。

2.2.3 网络模块设计

网 络 芯 片 采 用W5300 芯 片[10],W5300 是 一 款0.18 μm CMOS 技术的芯片,自带10/100 以太网控制器,并集成TCP/IP 协议。W5300 专为易于实现的Internet 嵌入式应用程序而设计,具有高稳定性、高性能和低成本等特性[11]。

2.2.4 串 口

串口采用MAX3232EUE芯片和MAX490ESA芯片。

2.2.5 A/D和D/A电路设计

模数转换芯片采用AD9430BSVZ,数模转换芯片采用AD9753AST,时钟为60 MHz。

3 测试软件设计

3.1 上位机软件设计

3.1.1 测试功能

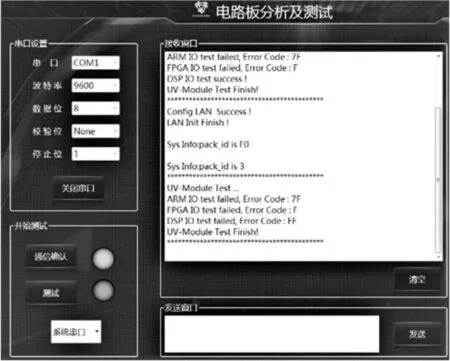

上位机软件会提供相应的操作按钮,只需点击一下,就可对板卡的相应部分进行检测,如果检测没问题,上位机软件在对应测试按钮的地方指示灯会按要求指示,同样如果有问题,指示灯会指示,对应的上位机软件界面也会打印信息,供使用者查看[12-13]。测试过程示意图如图6 所示。

图6 测试过程示意图

3.1.2 测试原理

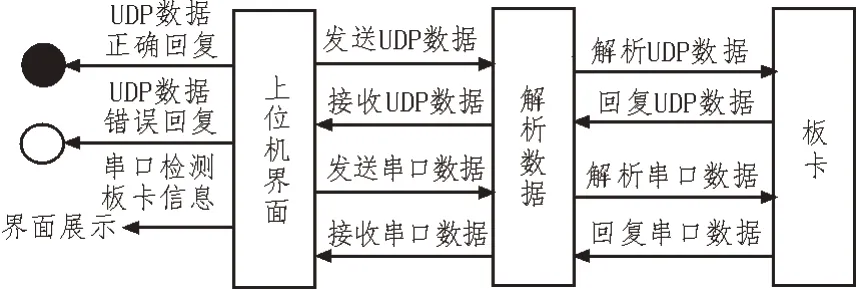

通过UDP 网络以及RS232 串口通信来实现上位机软件与板卡之间的信息交互,根据约定好的协议报文来读取板卡里的信息,上位机软件的发送端对网络通信的确定以及所要测试的板卡信息进行分类发送,可集中针对测试的部分进行测试,上位机软件测试原理如图7 所示,测试流程如图8 所示。

图7 上位机软件测试原理图

图8 测试流程图

3.1.3 通信原理

上位机软件与板卡之间通过UDP 网络进行信息的交互,主要定义了包括IP、端口在内的协议报文,报文里根据发送识别号的不同,分别对应板卡各个部分的信息,板卡在接收到对应的信息之后对上位机进行回复操作,上位机根据该回复指令与之前的协议报文进行对照,若出现不同,则亮红灯,若相同,则表示板卡正常,亮绿灯[14]。

在板卡出现故障时,上位机软件与板卡之间进行RS232 串口通信,根据板卡之间约定好的串口号、波特率、数据位、校验位、停止位等信息,完成与板卡之间的串口通信。当打开串口时,板卡会回复连接正常等信息,在进行板卡测试时,串口发送端发送某一特定的数字(与板卡之间约定好的数字)就可完成对板卡特定部分状态的检测,板卡会根据发送指令,检测完成后给上位机串口回复该状态信息,并显示在上位机软件界面,操作者根据上位机读取到的信息进行相应的操作。

3.1.4 测试结果

根据上位机测试的结果,操作者能够很好地检测被测板卡的状态信息,并快速处理板卡之间存在的问题。FPGA 调用正确板卡的信息与被测板卡信息进行比对,最后通过上位机软件直观地将测试结果显示在界面上。操作者可根据测试结果记录板卡出现的问题及板卡出现错误的现象,测试结果如图9所示。

图9 测试结果

3.2 下位机测试软件设计

3.2.1 通信确认设计

FPGA 芯片起到接收上位机命令的作用,上位机和FPGA 之间交互数据采用的是UPD 协议,报文格式是自定义格式[15]。首先是建立连接,上位机发送询问码给测试主板,测试主板回复特定字符给上位机,上位机正确收到,表示连接建立。通讯确认点击之后,上位机下发通讯确认字符,测试主板收到后向系统串口打印字符码。对于不同的板卡界面,当点击切换串口命令的选项会让测试主板将串口连接切换到对应的板卡接口上。如果板卡连接不对,则会出现乱码[16-18]。

3.2.2 串口切换设计

测试主板通过网络收到上位机切换串口的命令。测试主板根据数据包的串口号,在FPGA里将连接到上位机的串口线切换到网络包指定的串口线。

4 结束语

文中选择某型飞机上的3 块典型板件,通过直接在线读取替换或软件移植等方式,对电路板上的处理器、存储器、配置芯片和可编程逻辑器件等的内部核心代码进行备份,并针对部分汇编程序开展分析,理解模块在工作状态的原理,再通过正向开发的方式实现了该类型板件的测试与故障定位,对复杂机载电路板的测试具有一定的参考价值。