基于FPGA的数字跑表设计

2021-06-26胡一丁隋丽颖刘肖楠指导老师何英昊

胡一丁,隋丽颖,刘肖楠,指导老师:何英昊

(大连理工大学城市学院,辽宁大连,116000)

0 引言

在科技高度发展的今天,随着大规模集成电路和计算机的发展,现代电子设计的方法与技术也在不断发生变化。目前,比较有效的电子设计方法是将板卡设计、可编程逻辑设计和软件开发融合在一起。而且,计算机的应用与发展已经在人们的日常生活中逐渐崭露头角。大多数电子产品多是由计算机电路组成,本次设计的课题就是基于计算机电路的时钟脉冲信号、状态控制等原理设计出的数字跑表。跑表是体育比赛中常用的计时仪器,所以对时间的精确度很高。

1 系统设计

1.1 总体设计

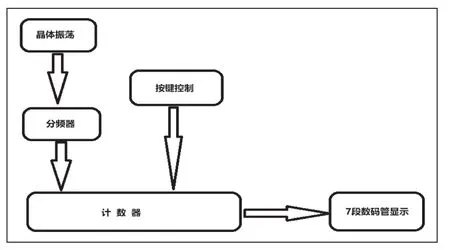

基于前面的分析,课题数字跑表设计由FPGA器件完成按键控制、数字的显示等核心数字电路的功能。设计数字跑表,令它通过两个按键来控制计时的开始和结束,一个是清0控制按键,用于设置跑表为初始零状态;另一个是开始/停止控制按键,在清0控制按键无效的时候,按一下开始/停止键则计时器开始计时,再按一下则暂停计时,再按一下则继续计时。数字跑表总体设计框图如图1所示。

图1 数字跑表的流程框图

1.2 各部分模块设计

根据此设计流程,我们可以将数字跑表的设计分为三个主要部分:

(1)分频

首先根据FPGA器件的基础时钟,进行时钟的设计,将器件自带的时钟频率进行分频,分频成为课题数字跑表所需的时钟信号,课题要求输入时钟频率为100Hz,100Hz=0.01s,使其满足数字跑表计时精度为10ms的要求,我们已知的FPGA器件上自带的时钟信号为50MHz。

(2)控制

根据要求数字跑表要具有控制功能,通过两个按键控制,一个为清零控制按键,控制异步清零,和启动功能,用于设置跑表为初始零状态,另一个按键为开始/停止按键,控制数字跑表的启动和停止,按一下开始/停止键则计时器开始计时,再按一下则暂停计时,再按一下则继续计时。

(3)显示

最后一步,对所得的数据进行处理,并将其显示。由显示的时分秒用7段数码管显示出来。将三个部分整合起来放在一张Block Diagram上进行编译,然后对管脚进行锁定。

图2 数字跑表的整体电路图

2 详细设计

数字跑表设计的程序流程图如图3所示。

图3 数字跑表设计的程序流程图

2.1 分频器模块

输入信号:CLK(时钟信号),CLR(清零按键),PAUSE(开始/暂停按键)

输出信号:MSH,MSL,SH,SL,MH,ML(7段数码管)

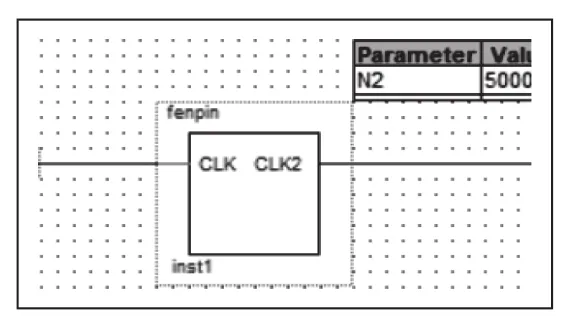

分频部分器件图如图4所示。

图4 分频模块

逻辑功能:对于器件自带的50MHz的信号进行分频成为100Hz的输入时钟信号。

2.2 显示模块

通过6个7段数码管分别显示时、分、秒,器件图如图5所示。

图5 显示模块

根据课题要求数字跑表的输出要能够直接驱动共阴极的7店数码管显示。

2.3 控制模块

要设置两个按键,一个为清零控制按键,控制异步清零,和启动功能,用于设置跑表为初始零状态,另一个按键为开始/停止按键,控制数字跑表的启动和停止,按一下开始/停止键则计时器开始计时,再按一下则暂停计时,再按一下则继续计时。器件图如图6所示。

图6 控制模块

3 系统仿真

完成了系统的分模块的功能调试后,可以进入系统仿真调试阶段。根据系统设计原理,当启动按键和开始计时按键同时打开时,就能够开始计时,得到相应的显示效果。将器件引脚锁定,CLR与PAUSE两个引脚锁定按键:

图7 器件引脚锁定图

当清零按键和开始/暂停按键同时置零时程序开始计时,如图8所示。

图8 启动计时仿真

当清零按键置一时,异步清零,跑表设置为初始状态,如下图9所示。

图9 重置初始状态仿真

当清零按键置零,开始/暂停案件置一时,程序暂停计时,如下图10所示。

图10 开始/暂停按键仿真

实验结果表明,该数字跑表设计的非常成功,由于实验电脑显示问题,所以仿真的输入频率未达到100Hz,但是证明程序没有问题,改变程序中的分频模块即可得到100Hz的输入时钟信号,达到课题所要求的10ms的精确程度。

4 验证

由其逻辑电路模块仿真也可看出,由控制模块控制其他两个模块,分别完成其任务,图11、图12、图13分别给出了在DE2板子上模拟实现的结果,与现实生活中所用的数字跑表功能基本一致,也与仿真结果基本一致。

图11 运行开始计时

图12 暂停计时

图13 重置计时

(1)运行(SM1 向下)

(2)暂停(SM1 向上)

(3)清零(SM0向上为清零,向下为重新开始)

5 结语

在开始程序设计的时候,由于对Quartus II软件使用不够熟悉,以及对VerilogHDL语言掌握不够,出现了很多语法错误,经过一遍遍的尝试与修改。终于将程序编译通过了,在这个过程中,也对软件的使用有了一点点的进步。仿真的时候由于实验室的电脑不能实现将50MHz分成100Hz的时钟,所以将其改成了50Hz的时钟分频为1Hz的时钟,仿真后,出现了结果。下载的时候,DE2板没有现象,经过反复检查程序、原理图和引脚,都没有发现错误,后来发现是因为将另一台电脑的数据线插到了DE2板上,经过修改终于出现了现象。通过本次实验,不仅熟悉了Quartus II软件,还掌握了VerilogHDL语言的设计思想,同时还了解了DE2板以及数码管的使用及原理,增强了自身的硬件语言水平,总而言之,本次课程收获良多。