基于CPCI总线的波控单元自动测试台

2021-06-08李艳华肖文光

李艳华,肖文光

(1. 安徽工商职业学院 应用工程学院,安徽 合肥 231131;2. 中国电子科技集团公司第三十八研究所,安徽 合肥 230088)

在大型相控阵雷达中,波控单元承担着控制计算机与T/R组件之间的控制码传输、控制指令传输、工况信息传输的任务.波控单元需要完成数据信息的硬件接口转换、通信协议转换等工作[1].由于T/R组件数量众多,有的阵面甚至达到上万个,使得波控单元的数量以及单个波控单元控制T/R组件的数量都在显著增加.因此,波控单元不但功能复杂,而且数量大、接口多,这给波控单元的测试带来很大挑战.

波控单元的测试要求是快速高效、故障定位准确、全面测试不遗漏.基于常规仪器仪表的测试方法只能对功耗、工作电压等参数进行测试,无法对控制码传输功能进行测试,所以设计一种专用测试台是非常必要的.凭借着结构紧凑、可靠性高、可扩展性强、支持热插拔等优势,CPCI总线[2-3]和VPX总线[4-5]已成为嵌入式集成测试领域最常用的总线.VPX总线是一种新兴的高速串行总线,虽然传输带宽和可扩展性能都远远超过CPCI总线,但是在满足同等设计条件下,CPCI总线在成本、成熟度、产品可获得性等方面更具优势.因此,本文以某相控阵雷达波控单元为测试对象,选择基于CPCI总线标准构建硬件平台,提出了一种基于CPCI总线的波控单元自动测试设计方案.

1 CPCI总线特点

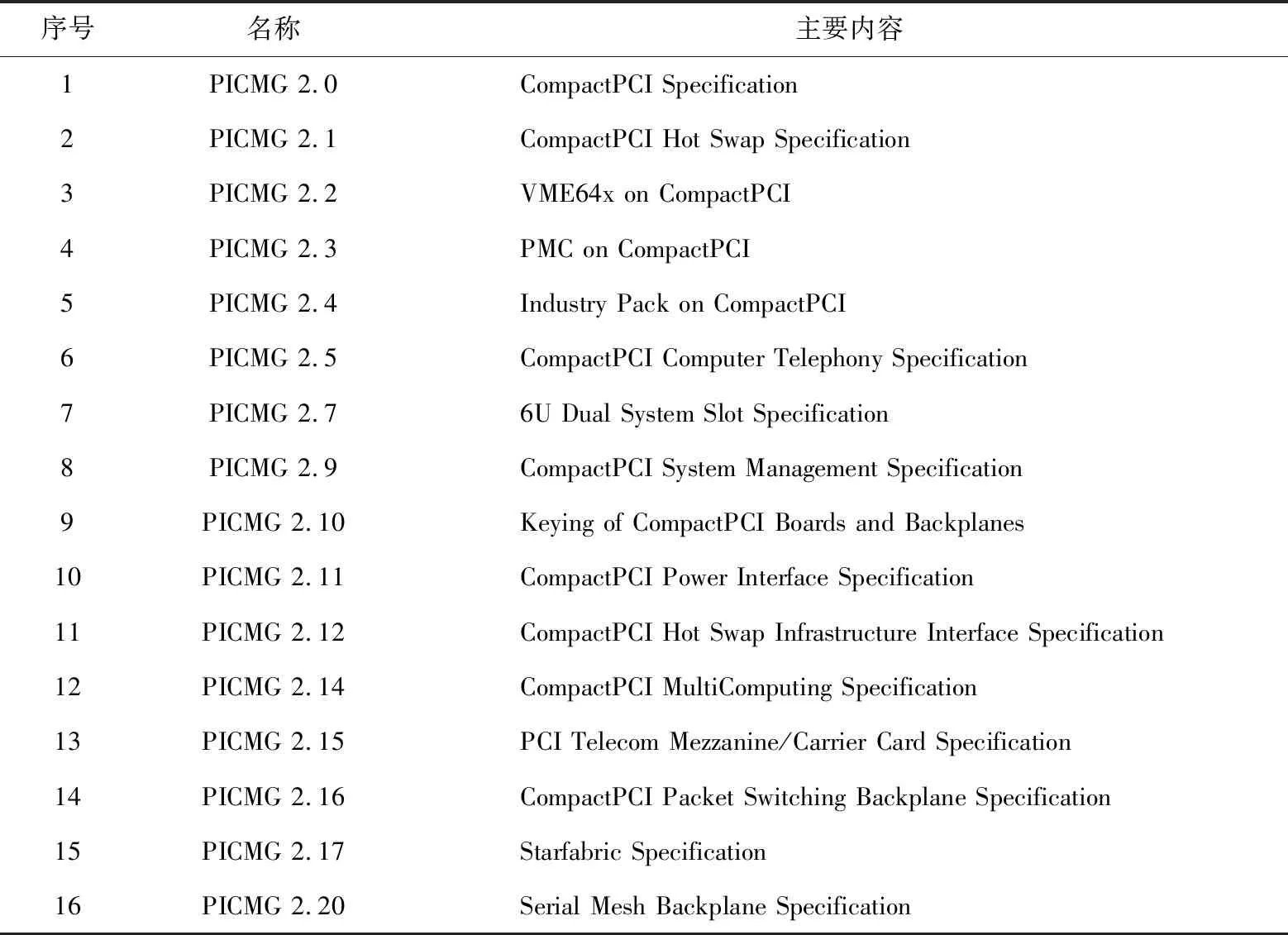

CPCI总线是由PICMG(PCI Industrial computer manufacturer’s Group)制定的一种开放工业计算机标准,其具体内容在PICMG系列技术规范中作了详细定义,这些技术规范见表1所列.

表1 PICMG系列技术规范

在这些规范中,PICMG 2.0是CPCI总线的核心标准,其对6U板卡与背板连接的五个连接器(J1~J5)的引脚进行了定义.其中,J1定义了32位的PCI总线信号,支持33 MHz或 66 MHz 两种频率;J2是J1功能的拓展,它将J1原来32位总线扩展到64位总线;J3~J5由用户自己定义.与 6U 板卡比较, 3U 板卡从硬件到功能都更加精简,只设计了J1和J2两个连接器[6].

CPCI总线在工业领域获得广泛的应用和普遍的认可,具有如下几个方面的优点.

(1)兼容标准PCI总线,二者具有相同的布局总线协议.

(2)高传输速度,一个32位33 MHz的CPCI总线的传输速度可达到132 MB/s,64位66 MHz时最高528 MB/s.

(3)具备欧卡规范,CPCI总线采用欧卡封装标准,抗震和通风性能明显增强,更换和维修效率也因其支持前面板插拔得到极大改善.

(4)良好的扩展性,CPCI总线理论上可扩展256个总线设备,每个总线段最高支持8个插槽,是PCI总线的2倍.

(5)抗震性强,传统的PCI板卡只能固定于一点,震动时板卡和插槽的连接处容易接触不良.而CPCI 板卡的顶部与周围都有导轨固定支持,可以保证接触良好.

(6)支持带电热插拔,由于CPCI板卡的插针长短不一,其中地和电源插针的长度最长,保证了板卡安全的带电插入与拔出.最短的插针是片选IDSEL、BDSEL,通过检测这两个信号,系统就可以判断板卡处于插入过程还是拔出过程[7-8].

2 测试台架构设计

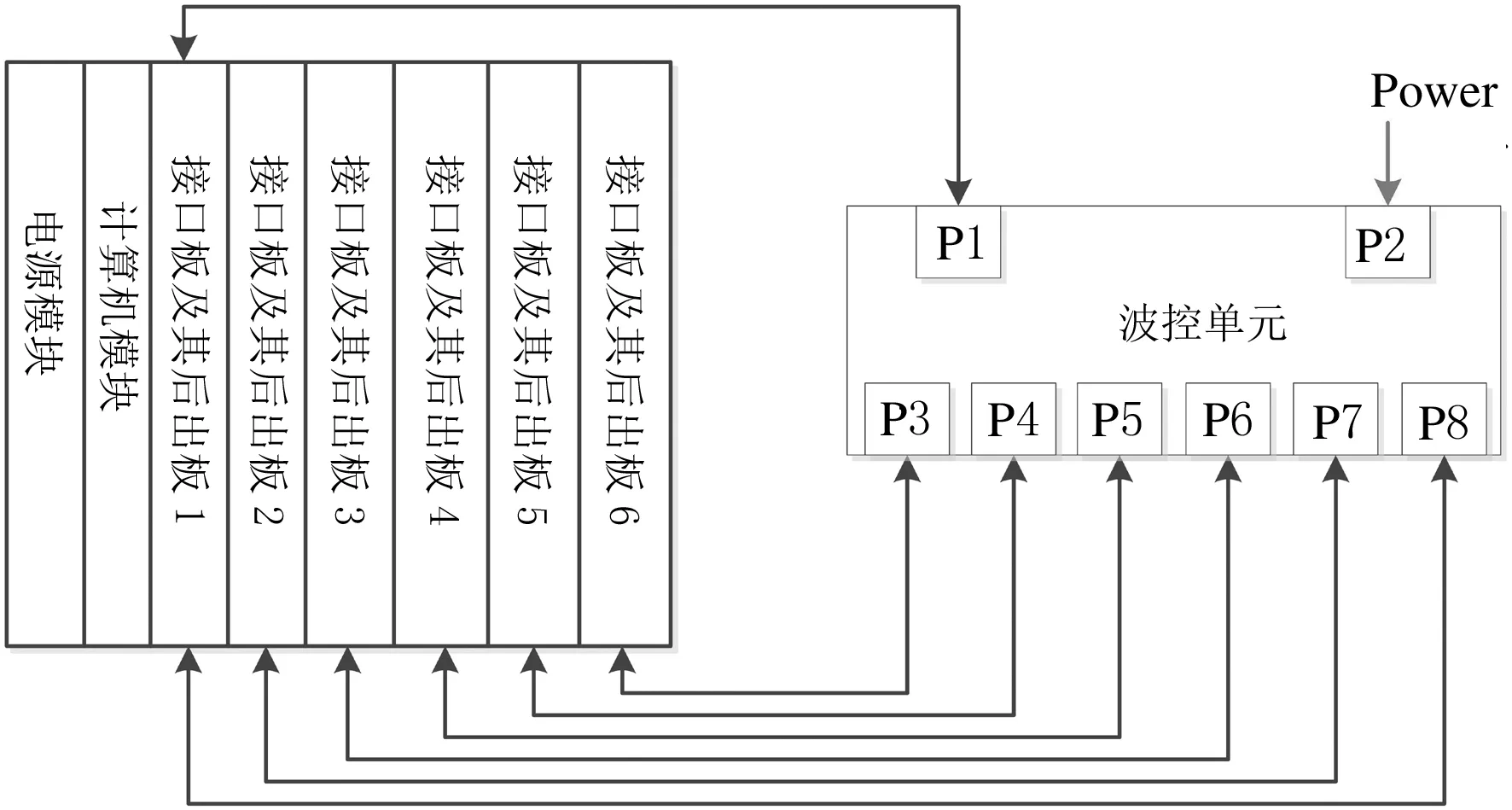

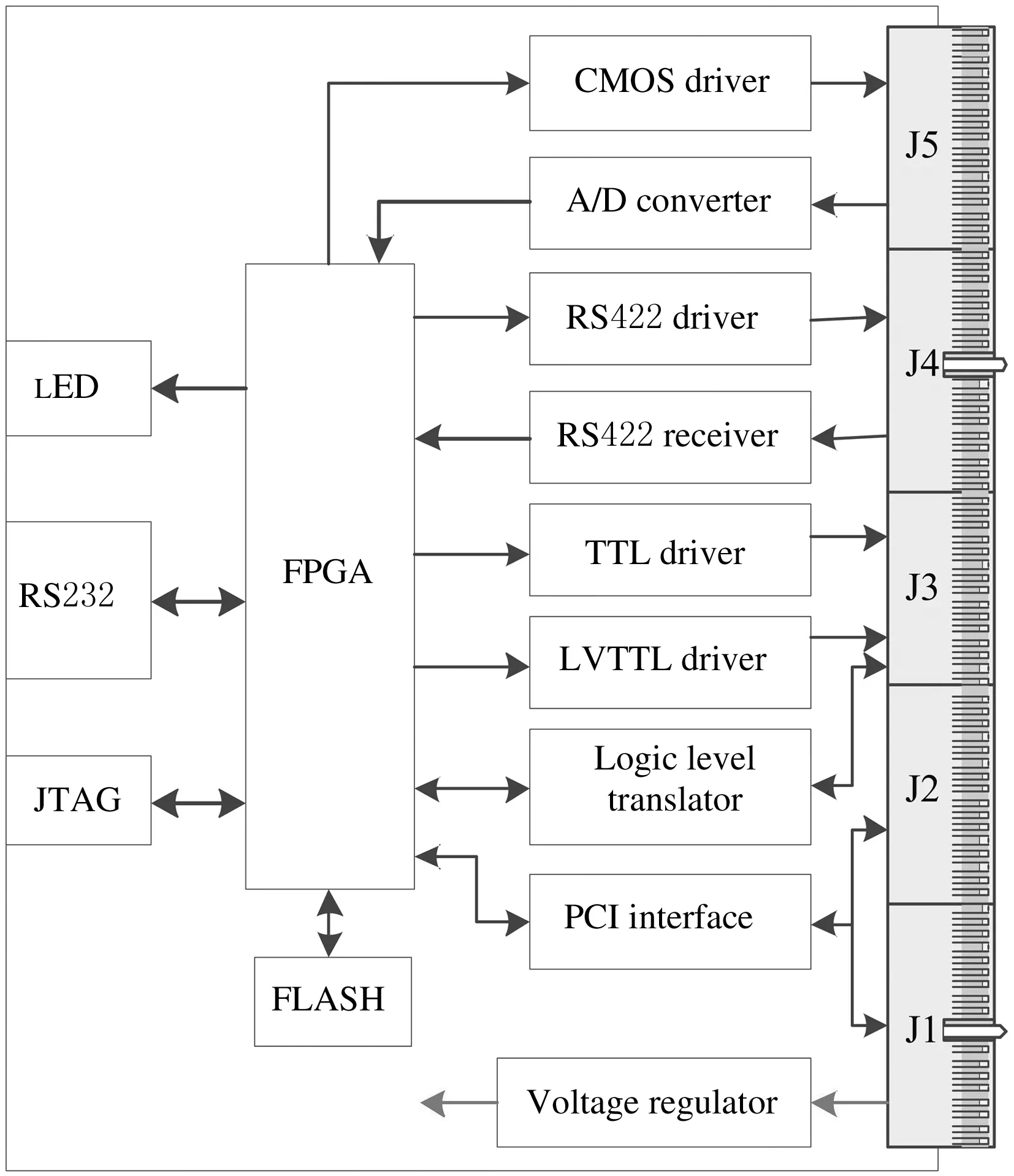

基于CPCI总线的波控单元自动测试台如图1所示.波控单元为待测设备,其P1口与波控计算机连接,用于接收控制码、时序和上报状态信息;P2口与二次电源连接,给波控单元供电并监测电源工作状态;P3~P8口分别与5个T/R组件连接,用于发送控制码、时序和上报组件状态信息.

图1 测试台组成示意图

在本设计中,波控单元自动测试台主要由符合CPCI 6U模块标准的1个电源模块、1个计算机模块、6个接口板(包括后出板)和1个CPCI背板组成.电源模块通过背板给其余模块供电,电源种类包括+5 V、+3.3 V、+12 V和-12 V.计算机模块负责专用测试软件的运行,完成参数设置、控制码的生成和比对、产生错误模拟指令和BIT测试指令、测试结果的显示和保存等任务.计算机模块通过CPCI总线与各接口板通信,最大传输速率为528 MB/s.

接口板负责数据的转发,并通过后出板与波控单元连接.接口板模拟T/R组件通过RS422串口与波控单元通信.6个接口板的硬件和软件设计完全相同.

3 组成单元的详细设计

3.1 电源模块

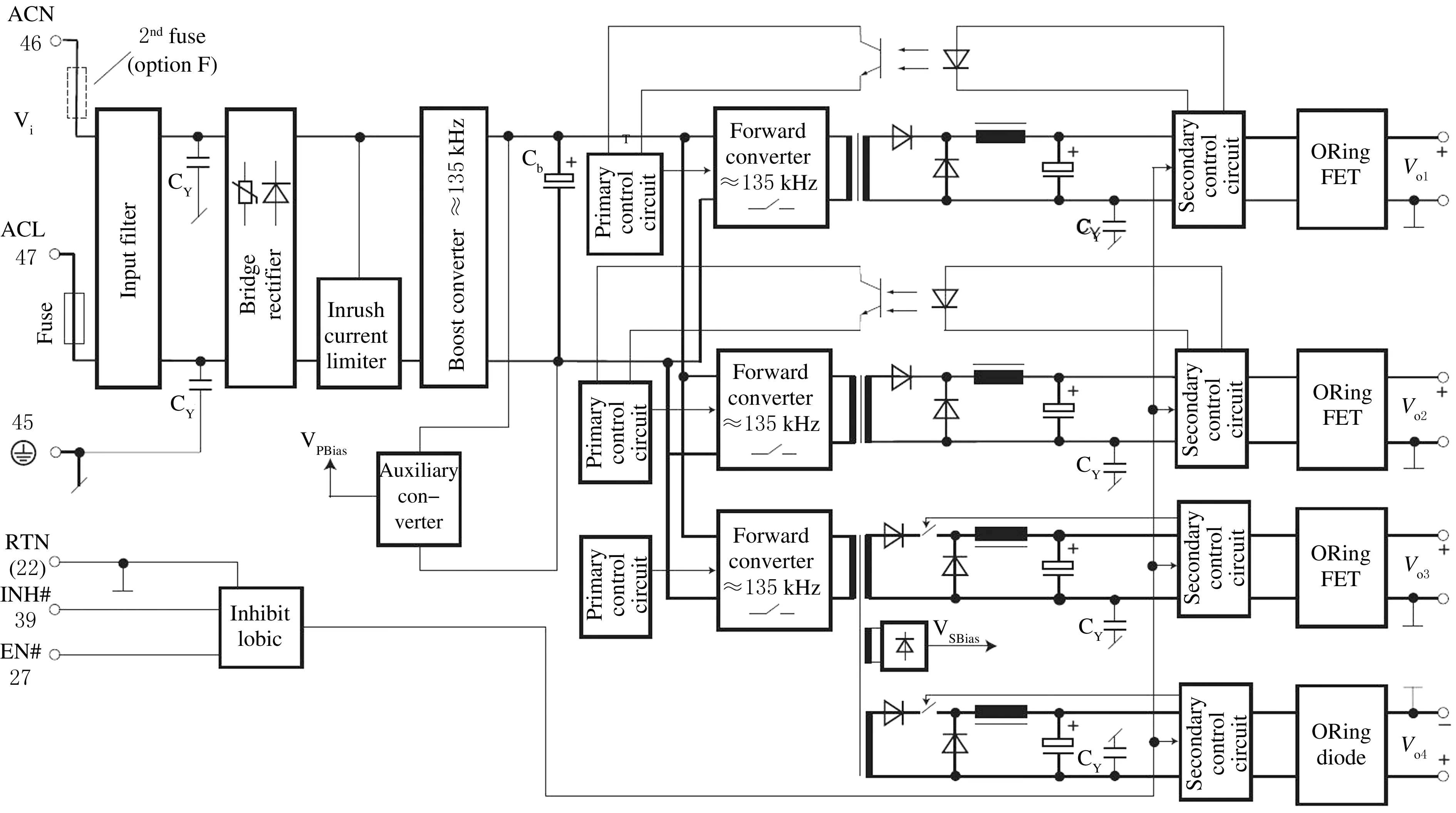

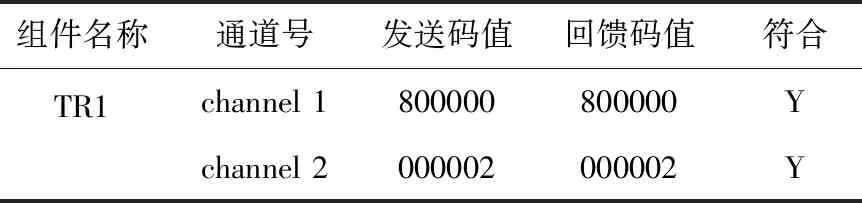

电源模块是通过背板给计算机模块及其他接口板供电的.根据CPCI规范对电源的要求,电源模块的标准输出电压包括+5 V、+3.3 V、+12 V和-12 V 4种.常用的输入电压有220 V交流和48 V直流两种,输出功率范围为300 W至700 W,标准厚度为8 HP,4 HP厚度为非标产品.本设计选用的电源模块原理如图2所示.

图2 电源模块原理图

该电源模块额定输入电压范围为100~240 V AC,额定输入频率范围为50~60 Hz,额定输出功率为500 W.其中,Vo1额定输出电压为+5 V,额定电流为40 A;Vo2额定输出电压为+3.3 V,额定电流为50 A;Vo3额定输出电压为+12 V,额定电流为8 A;Vo4额定输出电压为-12 V,额定电流为3 A.电源模块的输入内置保险丝进行过流保护,输入滤波器、压变电阻和浪涌电流限制器一起提供有效的抗瞬变电压保护,可将浪涌电流的危害降到最低.电源输出受INH#引脚的控制,该引脚支持TTL和CMOS逻辑电平.当INH#为低电平,所有的输出被禁止,该引脚通常连接到机箱电源开关[9].

此外,该电源模块的设计还采取了输入反极性保护、输入欠压关机、过载保护、热保护等措施,确保安全可靠.

3.2 计算机模块

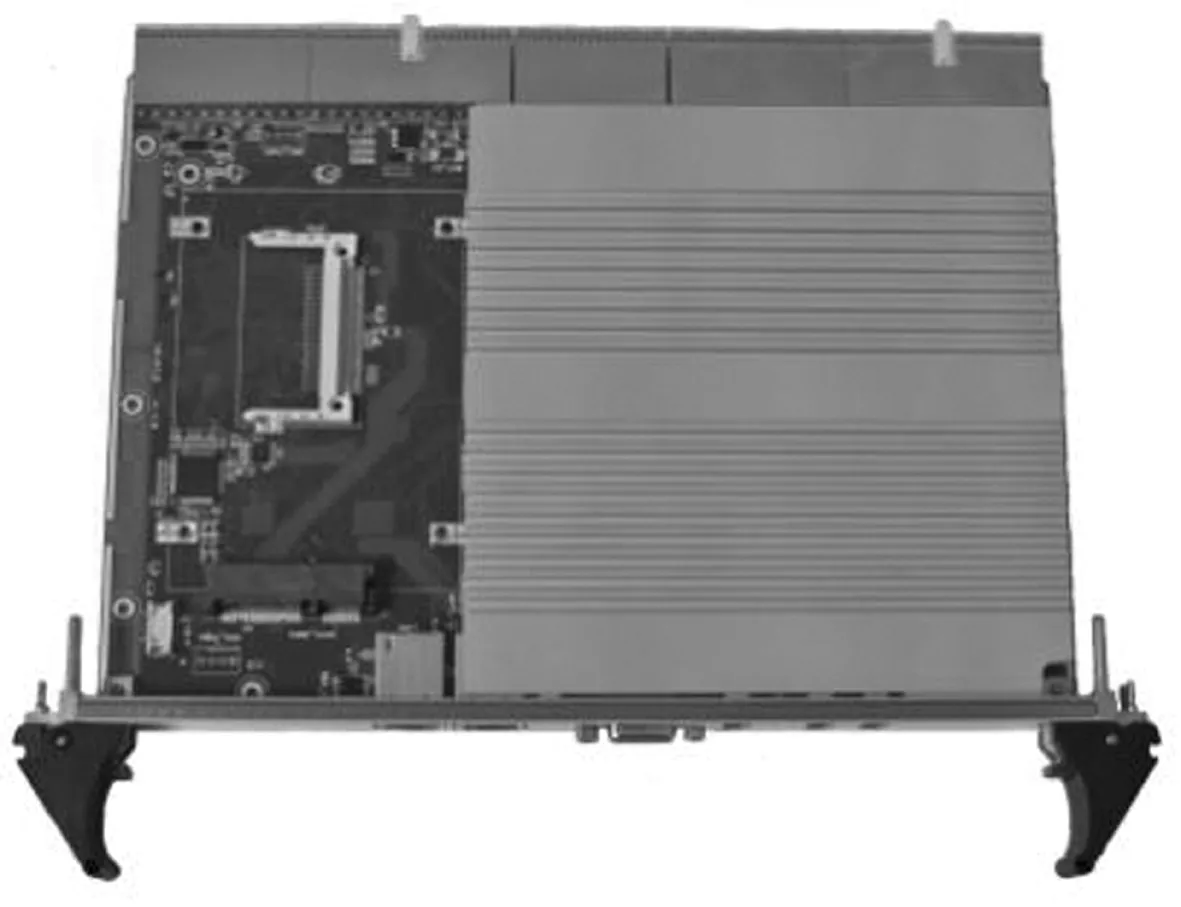

计算机模块是专用测试软件运行的硬件平台,主要由中央处理器、存储器、显示控制器、音频控制器、以太网控制器和通用串口组成.其中,中央处理器是计算机模块的核心.目前,市场上用的较多的处理器是飞思卡尔的PowerPC处理器[10]和Intel的X86处理器.从早期的P5/P6架构到现在的Core架构,凭借卓越的性能和持续的创新,Intel始终保持业界领先地位[11].计算机模块采用的是新一代6U双槽CPCI单板计算机,搭载2.5 GHz双核Intel处理器i7-3555LE、intel QM77芯片组及最高8 GB容量的双通道64 bit DDR3L存储器,支持板载安装CF卡与SATA硬盘,模块实物如图3所示.计算机模块前面板提供2个GbE接口、3个USB2.0接口和1个VGA显示接口.J1连接器和J2连接器通过PCIE-PCI桥和CPU连接,PCIE-PCI桥将32 bit/64 bit、33 MHz/66 MHz PCI并行总线转换成4X PCIE串行总线,减小了信号线的数量和布线难度.计算机模块采用Intel 82574实现4个GbE接口的通信,2个GbE接口位于前面板,另外2个GbE接口与J3连接器相连以支持PICMG2.16背板协议.通过J3连接器引出的接口还有6个USB2.0接口、1个VGA接口、4个SATA接口、1个PS/2接口和2个RS-232串口.通过J4连接器引出的接口包括1个4X PCIE接口、1个音频接口、1个DVI接口和3个TTL串口.通过J5连接器引出的接口包括1个4X PCIE接口、1个LVDS接口、1个SATA接口、5个GPIO接口和4个1X PCIE接口.软件支持Windows XP、Windows7和Linux操作系统.计算机模块整板采用SMT设计,结构紧凑,可靠性高,抗振性好,能胜任各种现场复杂处理工作.

图3 计算机模块

3.3 接口板

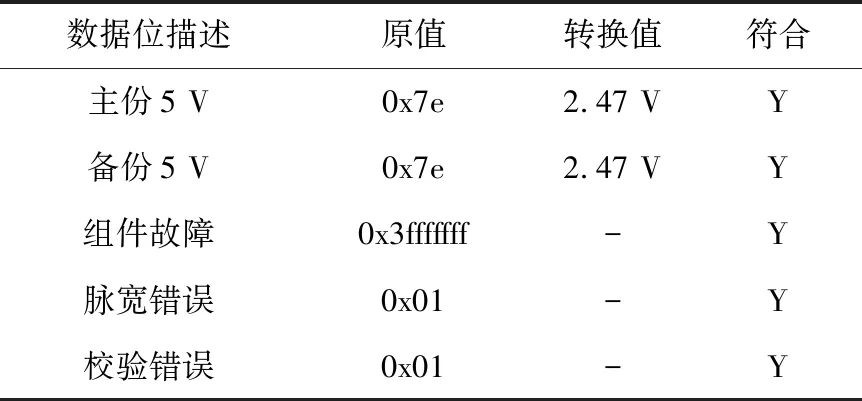

接口板与波控单元之间的测试信号包括RS422差分信号和模拟量两种.除了RS422驱动电路和AD转换电路之外,接口板还配置了多种接口驱动电路,以满足通用性和扩展性要求,接口板的设计原理如图4所示.接口板采用6U结构CPCI总线接口,主要由FPGA控制器、FLASH存储器、通信接口电路、接口驱动电路、A/D转换电路、PCI接口电路、电压调整电路及LED指示

图4 接口板原理图

电路组成.FPGA控制器为1片XC5VFX100T芯片,配置FLASH容量为256 MB.通信接口电路包括20路RS422发送接口电路、20路RS422接收接口电路和1路RS232串口电路.接口驱动电路包括8路TTL驱动电路、8路LVTTL驱动电路、16路电平转换电路和8路CMOS驱动输出电路.A/D转换电路可同时检测16路模拟量,采样位宽为12 bit,模拟量值为0~5 V.PCI接口电路选用PIC9030芯片实现复杂CPCI协议的实现,简化了设计.电源调整电路负责将+5 V输入电压转换为+3.3 V、+2.5 V、+1.2 V和+1.0 V为接口板上其它电路供电,LED指示电路提供红、绿两色状态指示.

4 测试流程

测试台通过闭环收发完成波控单元的控制码、时序和BIT功能测试,并通过数据比对自动定位故障点.具体测试过程包括正向测试和逆向测试两种.

4.1 正向测试

正向测试的主要目的是完成控制码和时序传输正确性的判断,具体测试过程如下.

(1)打开专用测试软件,加载控制码配置文件,并对测试模式、时钟频率、重复频率、数据格式、发射脉冲宽度、接收脉冲宽度等参数进行设置.启动测试后,计算机模块将控制码和时序通过CPCI总线发送给接口板1.

(2)接口板1接收控制码并产生TRT和TRR信号,通过RS422串口转发给波控单元,传输速率为2.5 Mbps.

(3)波控单元对接收到的控制值进行校验,对TRT和TRR的逻辑相关性、宽度等指标进行验证.若没有错误则按照T/R组件数据格式重新分包,并通过P3~P8口分别发送给接口板1~接口板6,传输速率仍为2.5 Mbps.若打码值有错误则记录错误标志,时序错误则强制转换为正确的时序.

(4)接口板模拟T/R组件接收控制码和控制时序,FPGA对控制时序进行逻辑和宽度比对,比对结果和控制码均通过CPCI总线发给计算机模块.

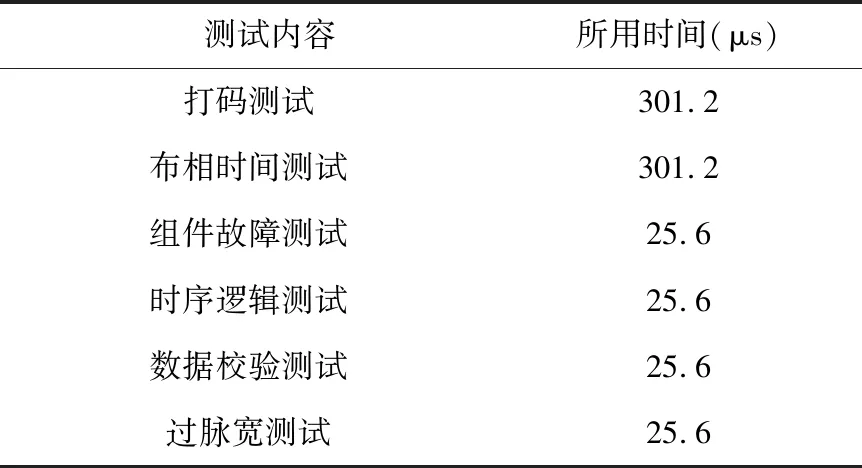

(5)计算机模块将接收到的控制码与所发送控制码进行比对,比对结果在测试软件上显示并存档,表2为双通道T/R组件1的控制码比较结果,共有30个T/R组件.

表2 控制码比较结果

4.2 逆向测试

逆向测试目的是检测波控单元的BIT功能.BIT功能是指波控单元上报T/R组件故障和自身状态信息的能力.自身状态信息包括数据校验错误、时序逻辑错误、脉冲过宽错误和A/D检测信息等[12-13].根据软件设置,BIT测试既支持单项测试,也支持自动遍历测试.T/R组件故障模拟测试的具体过程如下.

(1)计算机模块向各接口板发送T/R组件故障模拟指令0x03,然后等待接口板回馈数据.

(2)接口板解析故障模拟指令,模拟全部T/R组件或部分T/R组件故障,即以RS422信号形式向波控单元发送5个STATE信号,高电平表示故障.

(3)波控单元接收30个STATE信号,并记录错误标记,等待读取.

(4)接口板1向波控单元发送读数据时序,读操作以读使能信号RDEN下降沿开始,读数据期间保持低电平,上升沿结束读操作.波控单元根据读操作时序发送回馈数据帧.

(5)接口板1接收数据帧并进行校验,校验无误则通过CPCI总线发送给计算机模块,并在测试软件上显示和存档.表3为BIT测试中主5 V、备5 V、组件故障、过脉宽错误、数据校验错误的显示结果.

表3 BIT测试结果

5 性能分析

波控单元的测试内容包括控制码测试、布相时间测试、组件故障测试、时序逻辑测试、过脉宽测试、A/D检测测试和数据校验测试等项目.T/R组件的控制码长度为48 bit,则30个T/R组件的控制码长度为1 440 bit.RS422的传输速率为5 Mbps,CPCI总线的传输速率按照100 Mbps计算,接口板、波控单元和计算机模块处理数据的时间小于1 μs,这里忽略不计.控制码通过CPCI总线的传输时间约为3.6 μs,控制码通过RS422串口的传输时间约为297.6 μs,所以控制码测试的总时间约为301.2 μs.波控单元BIT测试的数据帧长度为128 bit,BIT数据帧通过CPCI总线的传输时间小于1 μs,BIT数据帧通过RS422串口的传输时间约为25.6 μs,所以BIT测试的总时间约为26 μs.波控单元各功能项测试时间见表4所列.

表4 测试时间列表

自动测试模式下,波控单元的测试时间为控制码测试时间与BIT测试时间的和,约为326.8 us.因此,基于CPCI架构的波控单元测试台可在1 ms内自动完成波控单元的正向和逆向功能测试、故障判断和显示,功能测试覆盖率达到100%,符合波控单元测试的设计要求

6 结语

基于CPCI总线的波控单元自动测试台已在实际项目中得到应用,并在多个产品中得到借鉴使用.与基于常规仪器仪表的测试方法相比,该测试台在测试效率、测试覆盖率、通用性、可扩展性等方面都具有明显优势,不但满足了波控单元电路输入输出信号的自动控制和测试要求,而且开发的接口板可以满足TTL、LVTTL、RS422、RS232、CMOS、A/D等多种接口信号的测试需求.该测试台可根据测试电路需求对后出板接口形式进行调整,非常适合雷达系统中不同单机或分系统的试验测试,便于设计师快速构建适合自己项目的测试系统.