一种高精度PTP时钟同步方法及应用

2021-05-31黄化吉吴其伟袁金保杨雪松

黄化吉,吴其伟,江 锐,袁金保,杨雪松

(伟乐视讯科技股份有限公司,广东 惠州 516025)

0 引 言

目前,在工业以太网应用中,网络时钟同步是一个核心技术。高精度时间同步协议(Precision Time Protocol,PTP)是标准化的精确时间协议,可以达到甚至超过亚微秒级的同步精度,特别适合分布式系统和以太网传输,是目前应用广泛的一种网络时钟同步协议[1]。

SMPTE ST 2110标准是SDI over IP技术最新的标准,是数字音视频领域IP专业流媒体标准,非常适合超高清制播系统下4K超高清电视节目的传输。ST 2110标准采用PTP作为时钟同步技术,对流媒体网络中各个设备进行全网时钟同步[2-3]。

在PTP的基础上,本文提出了一种时钟同步方法,能够较好地实现从时钟对主时钟的快速同步,且能合理平衡同步精度和稳定度。目前,该方法已经应用于伟乐视讯科技股份有限公司SDI over IP技术的相关产品中,并取得了良好性能。

1 PTP时钟同步原理

IEEE 1588协议定义了一个能够在测试和控制系统中实现高精度时钟同步的协议——精准时钟同步协议(PTP)。该协议应用于以太网,适用于任何满足多点通信的分布式控制系统,对采用多播技术终端的时钟可实现亚微秒级同步。

PTP通过报文传送建立时钟同步关系。在一个PTP通信子网中,可以把设备时钟分为主时钟和从时钟。全网中时钟精度最高的设备的时钟可作为主时钟,其余设备时钟为从时钟。PTP采用这种主从模式和时间戳机制进行报文交互,对时间戳进行编码并传送,在从时钟设备对时间戳进行计算并校准时间。

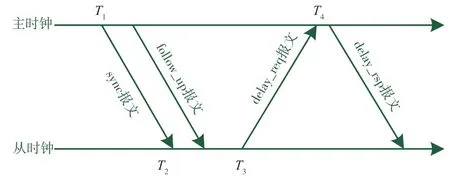

PTP时钟同步的原理是主时钟和从时钟之间通过报文传输并记录报文的收发时间,从相互传递的4个时间戳中计算得到主从时钟之间的往返时延和主从时钟之间的时间偏差,从而对从时钟的时间进行偏差校正。PTP主从时钟同步过程如图1所示。

图1 PTP主从时钟同步过程

具体同步过程可以分为4个报文过程[4]。

(1)主时钟在T1时刻向从时钟发送一个sync报文,以开启一次时钟同步,而从时钟则在T2时刻接收到该报文。

(2)主时钟在发送sync报文后会再次发送一个follow_up跟随报文,该报文包含发送sync报文的时间戳T1。

(3)从时钟接收到跟随报文后,在T3时刻给主时钟发送一个delay_req延时请求报文,而主时钟在T4时刻接收到该报文。

(4)主时钟在接收到delay_req延时报文后,会对从时钟响应一个delay_rsp延时响应报文,且延时响应报文中会携带T4时刻的信息。

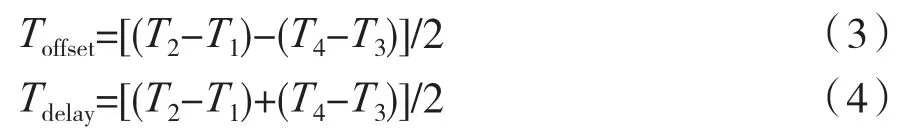

从以上T1、T2、T3和T4这4个时间戳可以计算出主从时钟的往返时延Tdelay和时延偏差Toffset。假设Tdelay1和Tdelay2分别是主时钟到从时钟和从时钟到主时钟的时延,则有:

假设主从通信的传输路径对称,式(1)和式(2)中的时延Tdelay1和Tdelay2相同,即Tdelay1=Tdelay2=Tdelay,则有:

如果主从通信中的传输路径非对称,可以假设Tdelay1=Tdelay+TΔ,Tdelay2=Tdelay-TΔ,式(4)不改变,Tdelay即重定义为往返的平均时延,则式(3)变为:

式(5)表示通过时间戳计算得到的T´offset,包含了一个固定的时延偏差TΔ。在更多的应用场景中,主从时钟的同步关心的是主从时钟的频差,TΔ的存在仅增加了同步时延,并不影响从T´offset中恢复频差信息的收敛性和稳定性。因此,在本文所提出的同步方法中以Toffset来分析主从时钟的同步及优化。

2 PTP时钟同步方法

从时钟得到与主时钟之间的Toffset后,可以根据Toffset来校正从时钟的时刻点。校正操作的核心内容是从时钟相对于主时钟频率偏差的校正,使得从时钟的频率能够较好地跟踪主时钟的频率,从而达到同步。

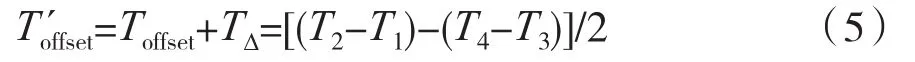

2.1 PTP时钟同步模型建模

本文研究PTP时钟同步的建模模型如图2所示。该模型中,主从时钟之间会周期性间隔250 ms(间隔可以根据实际情况修改)发起一次时钟同步操作。每次同步操作都会得到一个Toffset值,从而形成一个Toffset时间序列。由于网络存在不稳定性和测量误差等,以上得到的Toffset并不能很好地反映主从时钟之间的频率偏差,可以看作是真实值叠加噪声干扰的结果。本文所提的PTP时钟同步方法的目标是通过一定的滤波算法,尽量消除Toffset时间序列中的噪声影响,得到更精确的AF_Toffset数据,进一步通过合理的反馈控制算法使从时钟能够较好地还原主从时钟时间的频差信息Toffset,并用Toffset对从时钟进行频偏校正,使其自适应跟踪主时钟的频率。

2.2 数据滤波

Toffset序列反映了主从时钟的频差及设备处理和网络的时延抖动噪声。主从时钟的频差随着时间的延长会缓慢积累,与非特殊场景下的时延抖动噪声不同。数据滤波的目的是要降低噪声影响,从而使频差结果更趋于平稳。从Toffset序列的特征分析,可以考虑使用递推平均滤波法或一阶滞后滤波法对Toffset进行滤波去噪。

图2 PTP时钟同步模型

2.2.1 递推平均滤波法

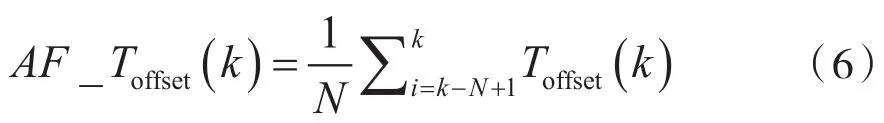

递推平均滤波法也叫滑动平均滤波法,是把连续N个样本点看成一个队列,采用先进先出原则,每次采样的新样本进入队尾,同时丢弃队首的一个样本点,之后对队列中的N个数据进行算数平均运算获得滤波结果,用公式可表示为:

只要选取合适的N值,递推平均滤波法即可对周期性干扰和白噪声干扰产生较强的抑制作用。由于滤波长度为N,对于偶然出现的脉冲性干扰会持续影响N个点的滤波输出,因此对脉冲性干扰的抑制作用较差。另外,由于需要N个滤波样点,因此所需的存储空间较大。

2.2.2 一阶滞后滤波法

一阶滞后滤波法是取本次样本值与上次滤波结果进行加权平均,权值可以通过经验进行调整。若令α为加权系数,则滤波算式可以表示为:

只要选取合适的加权系数,一阶滞后滤波对周期性干扰和白噪声干扰也有较强的抑制作用,不足之处在于存在一定的相位滞后性,且不能消除滤波频率高于采样频率1/2的干扰信号。由于一阶滞后滤波的反馈环节会对后续的滤波存在持续影响,因此一阶滞后滤波对脉冲性干扰的抑制作用也较差。它的突出优点是当前滤波结果仅与当前样本点及上一次的滤波结果相关,因此算法简单且无需过多的存储空间,实现复杂度低。

2.3 反馈控制

如图2所示的PTP时钟同步模型的最主要功能在于,根据滤波后的AF_Toffset数据设计一个既合理又简单的反馈控制跟踪算法,使从时钟能够较好地跟踪主时钟频率。从实际应用场景出发,从时钟的反馈控制跟踪算法需要兼顾收敛速度、跟踪准确性及跟踪稳定性3个特性。算法收敛速度表征在频差跟踪过程中,如果出现突发的偏离均值较大的噪声样点,算法输出结果能够快速收敛到正常值水平;算法的准确性表现在能够准确得到从时钟与主时钟之间的频差信息且结果误差小;算法的稳定性表现在每次同步计算得到频差结果波动小,能满足控制压控晶振或时钟频率校准模块稳定工作。

比例积分微分(Proportion Integration Differentiation,PID)控制算法是工业控制中应用最广泛的一种自动控制算法,具有原理简单、易于实现、适用性广、控制参数相互独立以及参数选定简单等优点。对于过程控制的“一阶滞后+纯滞后”及“二阶滞后+纯滞后”对象,PID控制算法是最优控制算法。本文在综合前述算法跟踪特性需求的基础上,采用PID控制算法对频差进行跟踪。

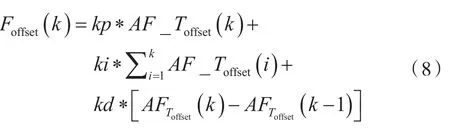

设频差为Foffset,则有:

式中,kp、ki及kd分别为PID控制算法中比例、积分及微分环节的系数。kp代表的比例项能迅速反映误差,从而减小误差,但是不能消除稳态误差,且过大的kp参数会导致系统不稳定;ki代表的积分项能消除静态误差,缺点是控制作业缓慢,且过强的积分作用会使系统的超调量加大,甚至出现振荡;kd代表的微分项能预测误差变化的趋势,减小超调量,并克服振荡,提高系统的稳定性,加快系统的动态响应速度,减小调整时间,从而改善系统的动态性能。

当算法刚开始启动或者受到外部干扰出现突发大噪声样点时,希望算法能快速收敛,因此需要设置较大的kp参数和ki参数;当算法收敛到一定程度后,希望算法能有较好的稳定性和较小的频差波动,因此需要设置较小的kp参数和ki参数[5]。因此,改进的PID算法在启动及中途判断当前AF_Toffset对历史均值的偏离程度,如果偏离超过一个预设的判定阈值,则使用一套较大的kp参数和ki参数;当偏离程度回归,小于预设的判定阈值后,则使用另一套较小的kp参数和ki参数[6]。

3 仿真及验证

算法的验证分为两部分:一是使用Matlab建模PTP同步模型并进行仿真验证,找到合适的参数;二是将该算法应用于符合ST 2110标准的SDI over IP的相关产品,实际测试主从时钟的同步效果。

3.1 Matlab建模仿真

使用Matlab建模如图2所示的PTP时钟同步模型,以主时钟为基准时钟,设定从时钟与主时钟的频率偏差ΔF为2×10-5。主从时钟每隔250 ms发起一次时钟同步操作,同步操作结束后,从时钟计算产生一个Toffset。先由Toffset滤波得到AF_Toffset,再由AF_Toffset经式(8)计算得到Foffset。仿真过程中,在主从时钟往返时延Tdelay上人为叠加一个幅度介于[-E,E]之间伪随机数ETdelay的干扰,用于验证往返时延抖动大小对计算结果的影响情况。为了能相对较为直观地分析算法性能,取Foffset与主从时钟的频差ΔF的差值ΔFoffset曲线进行数据分析:

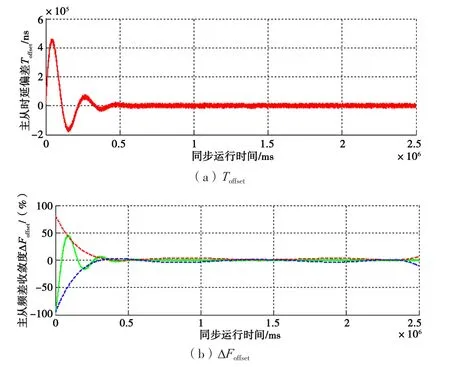

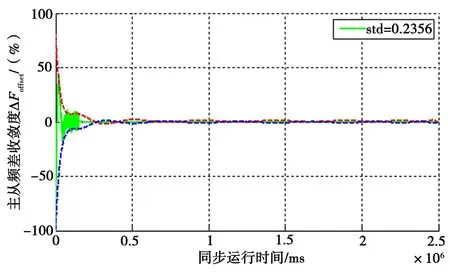

图3 Matlab仿真Toffset和ΔFoffset结果

根据算法建模仿真得到Toffset和ΔFoffset的结果,如图3所示,其中图3(b)还根据振荡收敛情况绘制了曲线的包络线。在图3的示例中,噪声的最大值E取20 μs,未使用任何数据滤波算法。PID参数采用经验进行整定,有kp=12 800/250、ki=125/250、kd=32/250。

(1)取ΔFoffset曲线的包络线收敛速度来研判算法的整体收敛速度,包络线收敛的越快,表明算法的收敛速度越快;

(2)取ΔFoffset稳定后样点的均值来研判算法收敛结果的准确度,均值越接近0,表明算法准确性越高;

(3)取ΔFoffset稳定后样点的均方差来研判算法收敛的稳定性,均方差值越小,表明算法的稳定性越高。

其中,(2)和(3)能直接反映PTP时钟同步精度的参量,而(1)体现的收敛速度对算法的实际应用具有非常重要的意义。如果不能够快速收敛,将会在很大程度上降低算法的实际应用价值。

3.1.1 PID参数整定

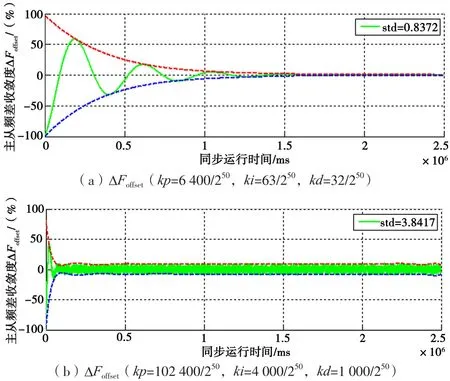

ΔFoffset曲线的包络线收敛速度主要取决于PID参数的整定。根据以上分析,收敛速度和收敛后结果的幅度波动大小难以同时满足。

不同的PID参数下,ΔFoffset曲线收敛的速度比较如图4所示。图4(a)曲线收敛速度慢,需要约5 000个样点后才能收敛到较平稳的结果,且收敛稳定后最终结果波动小,序列的均方差为0.837 2。图4(b)曲线收敛速度快,约500个样点后收敛到平稳结果,且收敛后结果波动较大,序列的均方差为3.841 7。

改进的自适应PID控制算法取两组PID参数,其中第一组参数在刚开始启动时用于曲线快速收敛,当收敛到一定程度后即自适应地转换到第二套参数用于曲线的平稳收敛。

自适应PID控制算法的曲线收敛仿真结果如图5所示。可以看出,改进后的自适应PID控制算法可以在曲线的收敛速度和收敛平稳度方面取得较好的效果。

3.1.2 主从时钟往返时延抖动的影响

主从时钟的往返时延抖动是影响时钟同步精度的重要因素。为了研究两者的关系,在图2的PTP同步模型中旁路数据滤波模块的功能,而反馈控制环节使用前述的自适应PID控制。

图4 不同PID参数下ΔFoffset曲线收敛的结果比较

图5 自适应PID控制算法结果

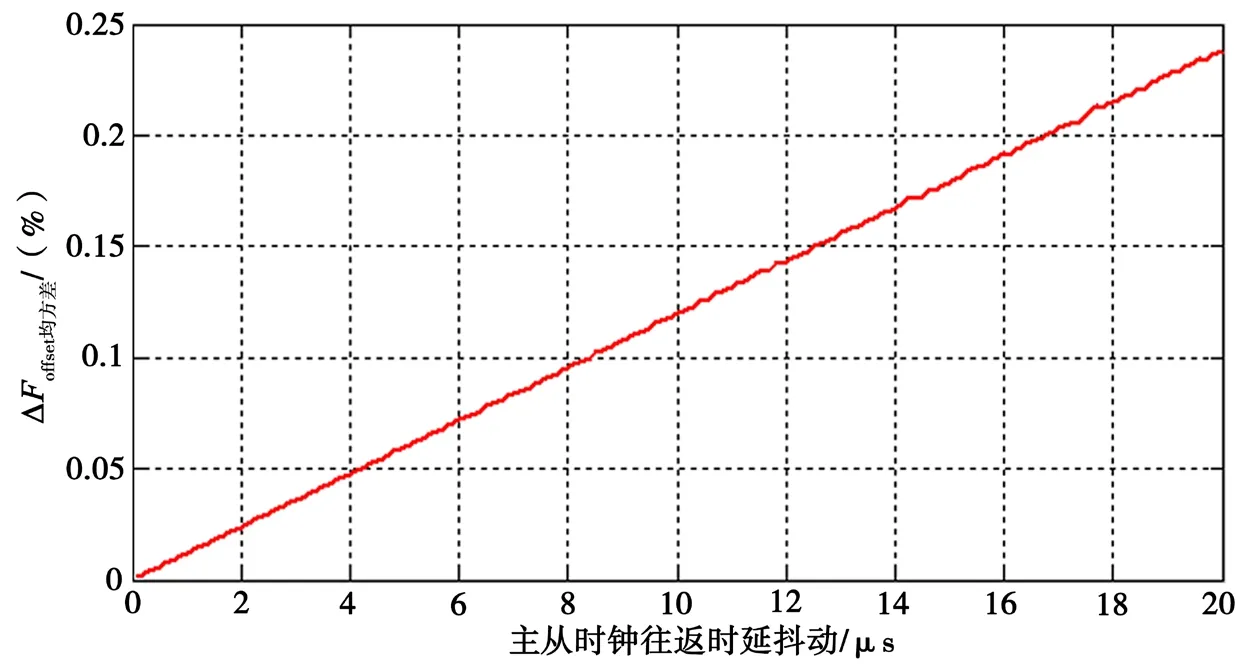

主从时钟往返时延抖动与频差稳定度关系的仿真结果如图6所示。对往返时延叠加一个幅度介于[-E,E]的伪随机数ETdelay的干扰,E从0逐步递增至20 μs,观察其与ΔFoffset均方差之间的关系。结果表明,往返时延的抖动程度与ΔFoffset的离散程度正相关。因此,控制往返时延抖动对提高时钟同步的精度具有积极意义。

3.1.3 滤波算法优化

为了研究数据滤波对PTP时钟同步的影响,将主从时钟的时延抖动控制在如图6所示的[-20,20]μs进行仿真,比对使用递推平均滤波法和一阶滞后滤波法进行滤波的结果。同样地,反馈控制环节使用前述的自适应PID控制。

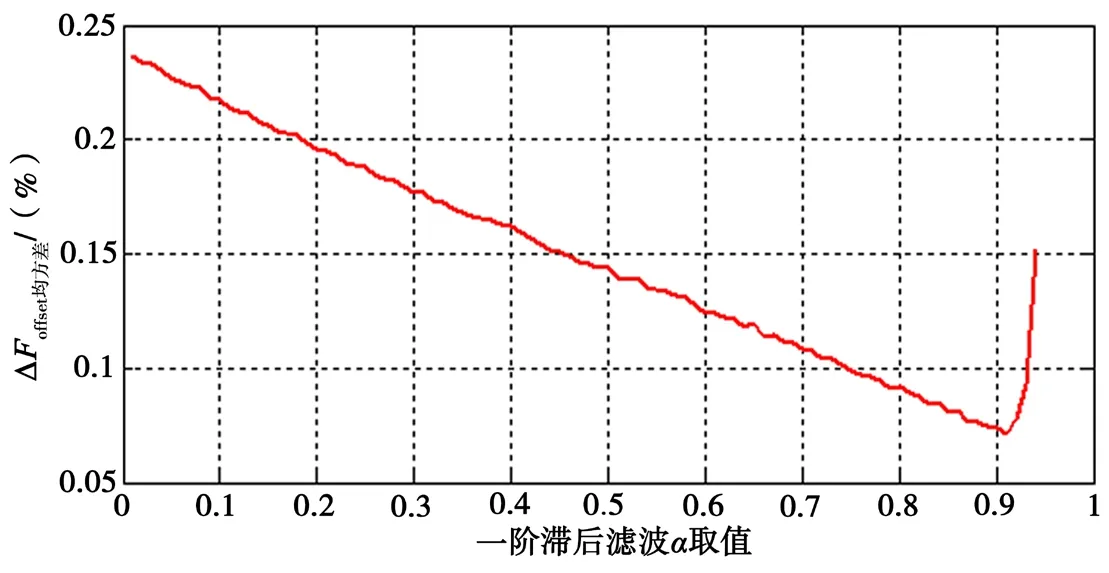

一阶滞后滤波参数α的取值与频差稳定度的关系,如图7所示。可以看出,当α=0.9时,频差稳定度性能最优,最优ΔFoffset均方差值约为0.071,较未使用滤波前的0.236有较大幅度的优化。

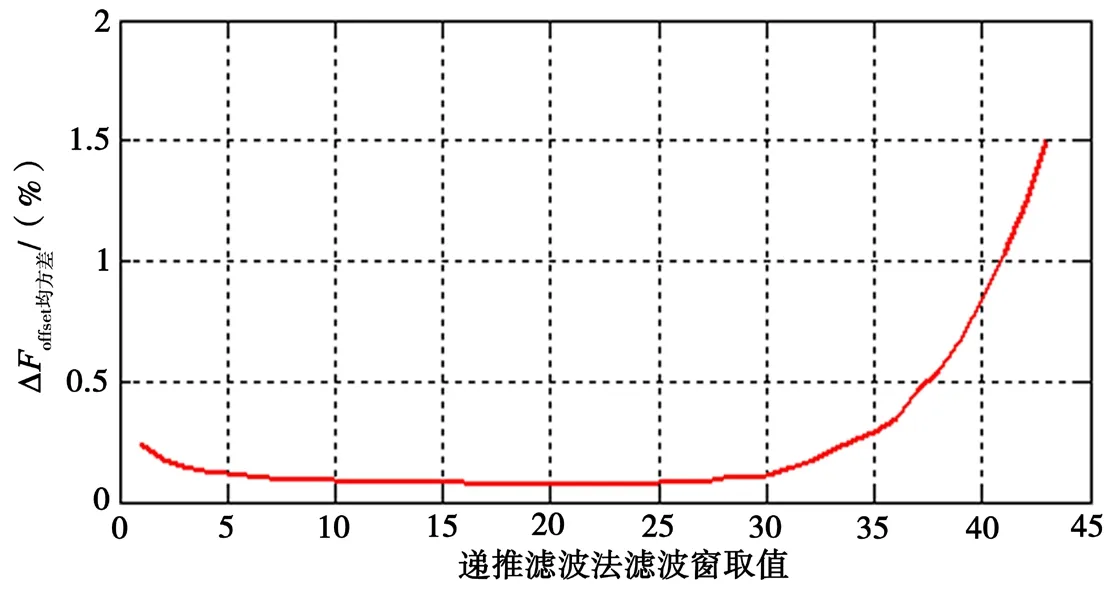

递推平均滤波法滤波窗取值与频差稳定度的关系如图8所示。过大的滤波窗N会导致Foffset曲线出现振荡,从而引起ΔFoffset均方差曲线递增。可以看出,当滤波窗N取值在[20,25]时,频差稳定性能最优,最优ΔFoffset均方差值约为0.07,较未使用滤波前的0.236有较大幅度的优化。

图6 主从时钟往返时延抖动与频差稳定度关系

一阶滞后滤波法与递推平均滤波法所能获得的最优频差稳定性能大致相当。在其他条件相同的情况下,不论使用一阶滞后滤波法还是递推平均滤波法,都比不使用任何滤波方法获得更好的频差稳定性。

3.2 同步方法和算法的FPGA实现及测量

依照仿真分析的结果,将自适应PID控制算法及α=0.9的一阶滞后滤波算法应用于伟乐视讯科技股份有限公司的SMPTE ST 2110标准的SDI over IP产品。该产品使用xilinx ZYNQ7000系列的FPGA实现主要功能。

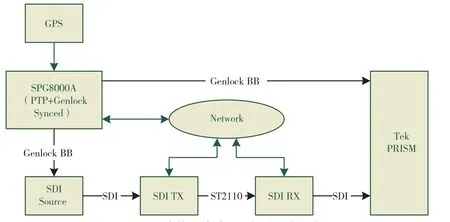

对PTP时钟同步系统进行测量的实际测试场景,如图9所示。SPG8000A是泰克公司主控同步及主控时钟参考信号发生器,可以发出Genlock同步锁定信号及网络PTP协议报文;SDI Source是SDI信源产生设备,接收SPG8000A发送的Genlock信号并产生SDI信号;SDI TX和SDI RX是伟乐视讯科技股份有限公司符合SMPTE ST 2110标准的SDI over IP产品,均通过内部以太网与SPG8000A同步;监测同步的设备是泰克公司的PRISM混合SDI/IP媒体分析平台设备,可以分析SPG8000A输出的Genlock信号与所接收的SDI信号之间的视频帧行场同步关系。视频帧的行场同步关系,可反映时钟同步的精度。

图7 一阶滞后滤波取值与频差稳定度关系

图8 递推平均滤波法滤波窗取值与频差稳定度关系

图9 PTP时钟同步实际测试场景示意图

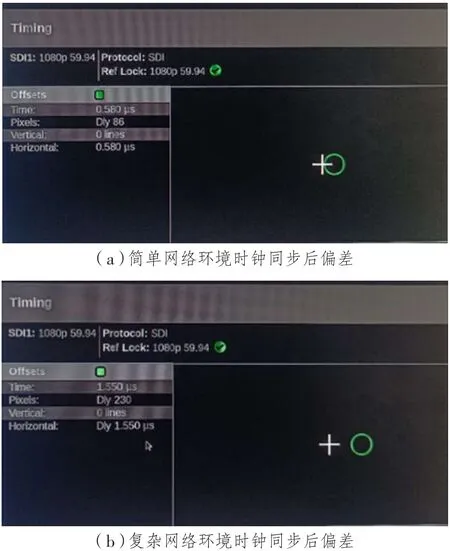

经过PTP同步后,在泰克PRISM设备上测试得到时钟偏差,结果如图10所示。图10中,十字交叉位置点表示Genlock信号的行场起始位置点(固定不动),圆形位置点表示同步后SDI信号的行场起始位置点(依据同步的情况会小幅左右摆动),圆形位置与十字形位置的偏差表示时延,圆形位置的浮动情况则表示同步后的稳定性情况。图10(a)为简单网络环境,仅存在一个交换设备,实际测量结果时延偏差在550 ns(约81个像素点)左右小幅摆动,长时间观测摆动幅度在[-100,100]ns;图10(b)为复杂网络环境,存在多级交换设备,且交换设备上同时存在其他主机,实际测量结果时延偏差在1.5 μs(约223个像素点)左右摆动,长时间观测其摆动幅度在[-230,230]ns,满足产品的指标要求。

图10 PTP时钟同步实际测试环境测试结果

4 结 语

本文分析PTP时钟同步协议的同步原理和过程,提出了一种时钟同步方法,对PTP协议同步后从时钟得到的时间偏移Toffset进行数据滤波,较好地消除了网络干扰的影响。同时,采用改进的PID控制算法对从时钟的时钟频率进行频偏校正,使用Matlab建模仿真分析了算法的性能指标,并将该方法实际应用到产品设计,同时比对测试了不同网络环境下网络的时延抖动对时钟同步精度产生的影响。随着基于SMPTE ST 2110标准的设备的普及,PTP同步方法将用于伟乐视讯科技股份有限公司相关视频处理设备的时钟同步设计,以获得进一步完善和发展。