基于AD5504 的多路信号源的设计与实现

2021-05-21张雪钰王洪凯焦新泉刘东海孙

张雪钰王洪凯焦新泉*刘东海孙 周

(1.中北大学仪器科学与动态测试教育部重点实验室,山西太原 030051;2.北京航天长征飞行器研究所,北京 100076;3.北京机电工程总体设计部,北京 100039)

在遥测系统中,采编器主要实现对遥测系统中分布的大量温度、压力、冲击、噪声等传感器产生的模拟量参数的采集与分析[1]。在采编器自测系统中,模拟量信号源可模拟传感器输出信号并提供标准信号。结合设计要求,需实现32 路0~28 V 波形、频率、相位、占空比可调的电压输出,除方波外频率在1 Hz~10 Hz,方波在1 kHz~10 kHz,电压调节精度为0.1%。传统信源卡采用专用DDS 芯片[2],参数固定,且通道数少,无法满足多种信号输出;采用DA 芯片与模拟开关阵列相结合的方式可实现多路可调节信号发生源,但该类信号源电路设计较为复杂,且存在一定的通道干扰,为简化设计并达到设计要求,采用AD5504 4 通道模数转换器进行DA 转换,结合VHDL 语言与上位机实现程控多路模拟电压的输出,经测试,满足设计要求且可靠性高。

1 总体设计方案

模拟量信号源板卡采用模块化设计,包括FPGA控制模块、电源模块、接口模块和信号源模块,其整体框图如图1 所示。电源转换模块负责背板电源的转换;接口模块采用33 M 的PCI 总线实现上位机与板卡的通信;信号源模块通过数模隔离芯片、DA 转换模块和方波控制模块来实现多通道0~28 V 可调模拟电压输出,各通道可通过上位机对每个通道的波形、相位、频率、幅度进行配置,多路信号源的切换由FPGA 内部寄存器进行控制。

图1 系统整体框图

2 DA 转换电路设计

2.1 隔离电路设计

为使数字信号与模拟信号完全隔离[3],避免信号串扰,采用4 通道数字隔离器ADUM1400 作为隔离芯片,其内部采用高速CMOS 与变压器技术相结合,功耗低,集成度高,它提供4 个独立的隔离通道,互不干扰。FPGA 输出的信号均隔离后再输出,数字端采用3.3 V 和DGND,模拟端采用A5V 和AGND。隔离电路如图2 所示。

图2 ADUM1400 隔离电路

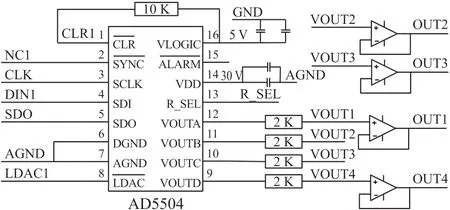

2.2 数模转换电路设计

为满足电压输出范围,同时考虑到减少外围偏置放大电路的设计,选择ADI 公司的12 位分辨率的4通道数模转换器AD5504 作为DA 芯片,分辨率可达30/(212-1)=0.007 3 V,满足设计要求。DA 转换电路如图3 所示。芯片的数字供电电压为5 V,模拟部分参考电压VDD 比需求电压大至少0.5 V,本设计采用30 V 供电,通过控制芯片的R_SEL 引脚,可以选择输出电压为0~30 V 或0~60 V,宽输出电压使得芯片外围无需再增加电压放大电路。输入为SPI 串行接口,FPGA 通过SYNC、SCLK、SDI 与AD5504 通信,输出包含4 个通道,为了降低输出阻抗,提高带负载能力,需对输出电压进行跟随缓冲。

图3 DA 转换电路

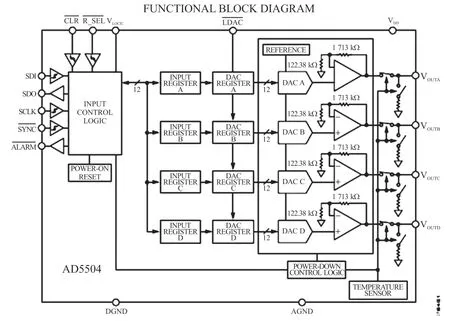

由图3 可知,AD5504 不需要外部模拟开关阵列的配合,4 通道的选择输出或同时输出,通过控制芯片内部寄存器的值来实现,因此简化了电路,同时也大大降低了通道之间的串扰[4]。其内部结构图如图4 所示。在单个芯片封装中包含4 个DAC,4 个输出放大器和一个精密基准电压源,内部为双缓冲结构,该结构使数据可以串行加载,并在下一次更新前,输出不受影响,同时可以以并行方式驱动所有开关,最大程度的减少各开关之间的时间偏移,减少毛刺并改善失真性能。其LDAC 引脚可配置4 通道同步输出,双缓冲的结构使数据依次载入一级缓冲后,同时更新所有通道的输出缓冲器,达到同时输出的目的。设计时多片芯片共用时钟、数据和CLR 信号,而SYNC 和LDAC 信号单独连接FPGA 的不同引脚[5]。输出电压由输入DAC 的二进制码决定:

式中:D是载入DAC 寄存器的二进制编码的十进制等效值。AD5504(12 位)即为0~4 095。

图4 AD5504 内部结构图

2.3 波形输出电路控制

由于输出波形中包含方波,若直接经采样保持电路输出,方波边沿时间即为采样时间,为十几微秒,不能保证方波边沿的完整性[6],因此采用模拟单刀双掷开关ADG333A 切换来实现方波的输出。通道切换电路如图5 所示。

图5 波形输出电路

ADG333A 的模拟电压输入可达32 V,通道导通典型时间为90 ns,而关断时间为80 ns,可以满足方波高低电平的快速切换[7]。其中IN 管脚为AB 通道选择管脚,通过控制IN 管脚的电平,可切换AB通道输出方波的上下限值至D 接口输出,从而实现方波的输出。若输出波形为其他波形时,IN 管脚置1,波形从ADG33A 的A 通道输出。波形输出后还需经过一阶低通滤波器来抑制杂波,保证波形的平滑输出,为减小输出阻抗提高信号源的驱动能力,模拟开关输出后增加运放跟随电路。ADA4625_1 工作电压可达36 V,轨到轨输出,压摆率为48 V/μs,满足方波快速变换要求。

3 DA 转换逻辑设计

3.1 DA 转换时序设计

DA 转换器AD5504 使用3 线串行接口与FPGA 通信,串行数据通过SDI 引脚输入16 位控制字至移位寄存器。表1 为AD5504 输入寄存器控制字格式,其输入移位寄存器为16 位位宽,包含一个读写控制位,3 位地址位和12 位DAC 数据位,第15 位为读写控制位,R/W 为1 则为读模式,为0 为写模式。DB14-DB12 为地址位,用于输入寄存器的选择,若A2A1A0为111,则为控制寄存器。控制寄存器用于设置DAC输出通道的状态,一个写控制器操作必须接另一个写操作,第2 个写操作可以是写入DAC 输入寄存器或空的写操作。通过FPGA 控制输入寄存器的地址和数据写入来实现AD5504 的通道切换及DA 转换。

表1 输入寄存器控制字格式

AD5504 的写操作时序图如图6 所示。SCLK为串行时钟信号,最高支持16.667 MHz,在该时钟的上升沿将数据通过SDI 引脚依次写入AD5504 内部的16 位移位寄存器中[8]。SYNC 为帧同步信号,空闲时该信号为低电平,在每次数据写入操作之前,需要将该信号拉高20 ns,在该信号的下降沿启动写操作。SDI 为数字信号输入端。系统上电以后,上位机下发启动信号源指令,设定值被写入FPGA 内部的寄存器中,然后模拟量信号源模块调用内部寄存器中的数据[9],当LDAC 有效时将得到的通道地址和对应的数据缓存到相应的寄存器中,当LDAC无效时输出信号。

图6 写操作时序图

输入寄存器3 位地址位对应的功能如表2 所示。

表2 地址位定义

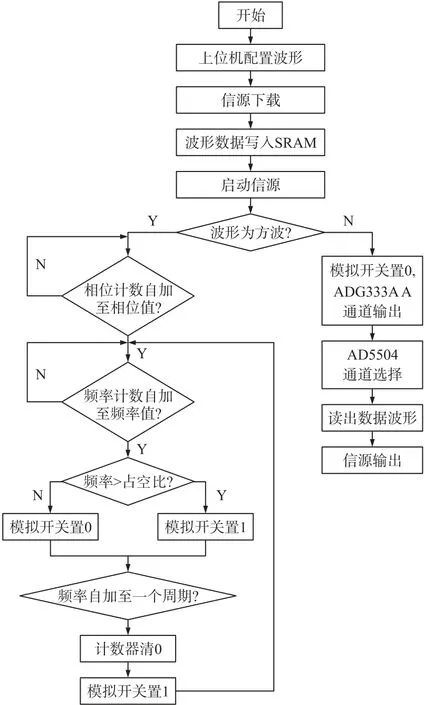

3.2 DA 转换控制逻辑设计

DA 转换控制逻辑主要为FPGA 接收上位机指令并识别,将上位机下传的波形参数及采样值经FPGA 缓存下载至SRAM[10],并在收到启动信源指令时对波形数据进行读取、DA 转换、通道切换等操作。上位机通过用户配置的波形、频率、相位等参数,采用波形函数对配置波形进行采样量化[11],通过PCI 的DMA 模式突发下传至FPGA 并存入SRAM 中。其中各通道的波形信息存在SRAM 的前256 KB 中,波形参数存储在后96 个存储单元内,每个通道含3 种参数控制字:相位、频率、占空比。因此32 通道的波形参数共96 B,相位范围为0~360,频率范围根据波形决定,占空比范围为0~100,波形存储格式如图7 所示。

图7 波形存储格式

图8 波形输出控制流程

波形控制流程图如图8 所示。参数字节的最高2 位为波形类型选择,11 为方波。由于方波的特殊性,进行逻辑设计时分为波形为方波与其他波形[6],FPGA 在上位机下发启动指令后,FPGA 以1 000 个时钟为周期进行一路数据的读取和输出。FPGA 先从SRAM 初始地址依次读出各路波形控制字并进行判别,若判断波形标识符为“11”,将偶数通道的输入端信号设置为幅值电压,奇数通道为下限值,通过相位、频率计数器与方波控制字比较的结果使ADG333A 的IN 引脚电平周期性变换[12],从而实现两通道切换,实现方波频率、相位、占空比的控制。若为其他波形,此时ADG333A 通道选择端IN0,IN1,IN2,IN3 分别赋值低电平‘0’,使得对应V0,V2,V4,V6 通道输出波形。奇数通道均为0X0000。将SRAM内的数据按照设定好的延时值被顺序读出,将读出的波形数据转入数模转换模块进行数模转换。

4 实验结果

上位机波形设置界面和指令发送界面如图9 所示。每个通道可配置的参数包括波形、频率、相位、占空比和幅值。可选用已经配置好的波形文件,也可以重新设置并生成新的通道。

图9 上位机界面

在上位机设置通道分别输出频率、相位不同的正弦波、锯齿波,占空比不同的方波,并用示波器进行波形显示,如图10 所示,波形平滑无过冲现象,达到输出要求。

图10 输出波形图

将信源每路波形的设置参数通过上位机进行配置,通过参数设置可对信号源的幅值进行设置并生成通道。对其转换误差进行测试并采用上位机辅助修正的方式,提高信号源精度,根据输入数字信号值,计算出理论输出电压,采用万用表测量DA 输出端电压,记录如表3 所示。

表3 AD5504 测试结果

标定基本依据为最小二乘法[13]。令理论输出电压为Y,DA 转换实际输出值为X,则Y=AX+B。使用Origin 进行绘图求解线性系数A、B,图11 为使用Origin 计算标定系数的过程。

图11 Origin 求解线性系数

5 总结

基于FPGA 和PCI 总线的多通道信源卡,采用AD5504 结合上位机配置实现了32 路0~28 V程控电压的输出,简化了调理、运放跟随、放大的过程。实验结果表明,该信源卡输出的电压稳定性好,失真小,已成功应用于某等效器系统中,具有较高的使用价值。