一种高压开关综合数据采集与监测系统设计

2021-05-07侯建华刘雪芬

侯建华,刘雪芬,张 凯

(西安西电开关电气有限公司技术中心,西安 710077)

0 引言

电力系统中高压开关设备运行的稳定和可靠对整个电力系统至关重要,对高压开关设备进行在线监测很有必要。目前在线监测装置对监测功能分类过细,造成监测IED(智能电子设备)种类多,工程实施成本高,在线监测产生的经济效益远低于预期。因此将各种监测IED如机械特性监测IED、SF6监测IED、局放监测IED、避雷器监测IED等多种监测功能整合成一台综合监测IED,对高压开关运行的各项参数进行在线监测,将有利于降低成本、工程实施难度和维护工作量[1]。

高压开关综合数据采集与监测装置应能连续或周期性监测、记录被监测设备状态的参数,及时有效地跟踪设备的状态变化,有利于预防事故的发生;根据监测数据能够有效判断被监测设备状况,以便调整设备试验周期,减少不必要的停电试验,或对潜伏性故障进行预警;装置宜具备多种输出接口,具有与其它监控系统间按统一通信规约相连的接口,具备报警输出;具有良好的人机界面,操作简单,便于运用。根据在线监测装置的技术要求,高压开关综合数据采集与监测系统应能监测高压开关的机械特性、SF6气体、母线温度、避雷器、局放等参数,并具备录波功能[2]。

基于以上工程实际出发和在线监测系统的技术要求,装置在硬件设计时采用了FGPA+STM32双处理器的架构。FPGA(field programmable gate array,现场可编程门阵列)属于专用集成电路中的一种半定制电路,内部有丰富的可编程逻辑单元、大量的硬件乘法器模块、充足的I/O引脚资源,使用Verilog HDL/VHDL(硬件描述语言)实现设计。采用FPGA进行的嵌入式系统硬件设计,可重编程、可定制、速度快、能缩短开发周期,满足实时处理的要求[3]。基于ARM Cortex-M4内核的STM32F407是一种高性能的32位微控制器,它是针对低成本、低功耗、高性能的、面向终端应用的微控制器,内核架构先进,性能优越,主频可达168 MHz,执行效率高,具有较高的运算能力及数据处理能力,拥有丰富的外设接口和扩展功能[4]。采用FPGA和STM32双处理器架构的平台设计,可以充分发挥两者各自优势,通过STM32的FSMC(flexible static memory controller,灵活的静态存储控制器)接口和FPGA的双端口RAM(random access memory,随机访问存储器)能快速实现两者之间的数据交互,整个系统具有成本低、速度快、可靠性高的优点,能满足高速数据采集、存储、控制等多功能应用。

1 系统整体设计

STM32微控制器采用的芯片是ST(意法半导体)的STM32F407ZE,FPGA是Xilinx(赛灵思)的XC6SLX9-2TQG144I。FPGA芯片基于成熟的45纳米低功耗铜工艺技术,在成本、功率和性能上实现了最佳平衡,内部提供了丰富的逻辑单元、触发器等内置系统级块用于逻辑设计,并提供了一种新的、更高效的双寄存器6输入查找表(LUT)逻辑供选择[5]。STM32F407ZE为144引脚封装,主频高达168 MHz,具有512 KB Flash和192 KB SRAM,通信接口多达15个,多达17个定时器,还具有符合IEEE 1588 v2标准要求的以太网MAC10/100控制器和能够连接CMOS照相机传感器的8~14位并行照相机接口,是一种高集成度、高性能的微控制器。

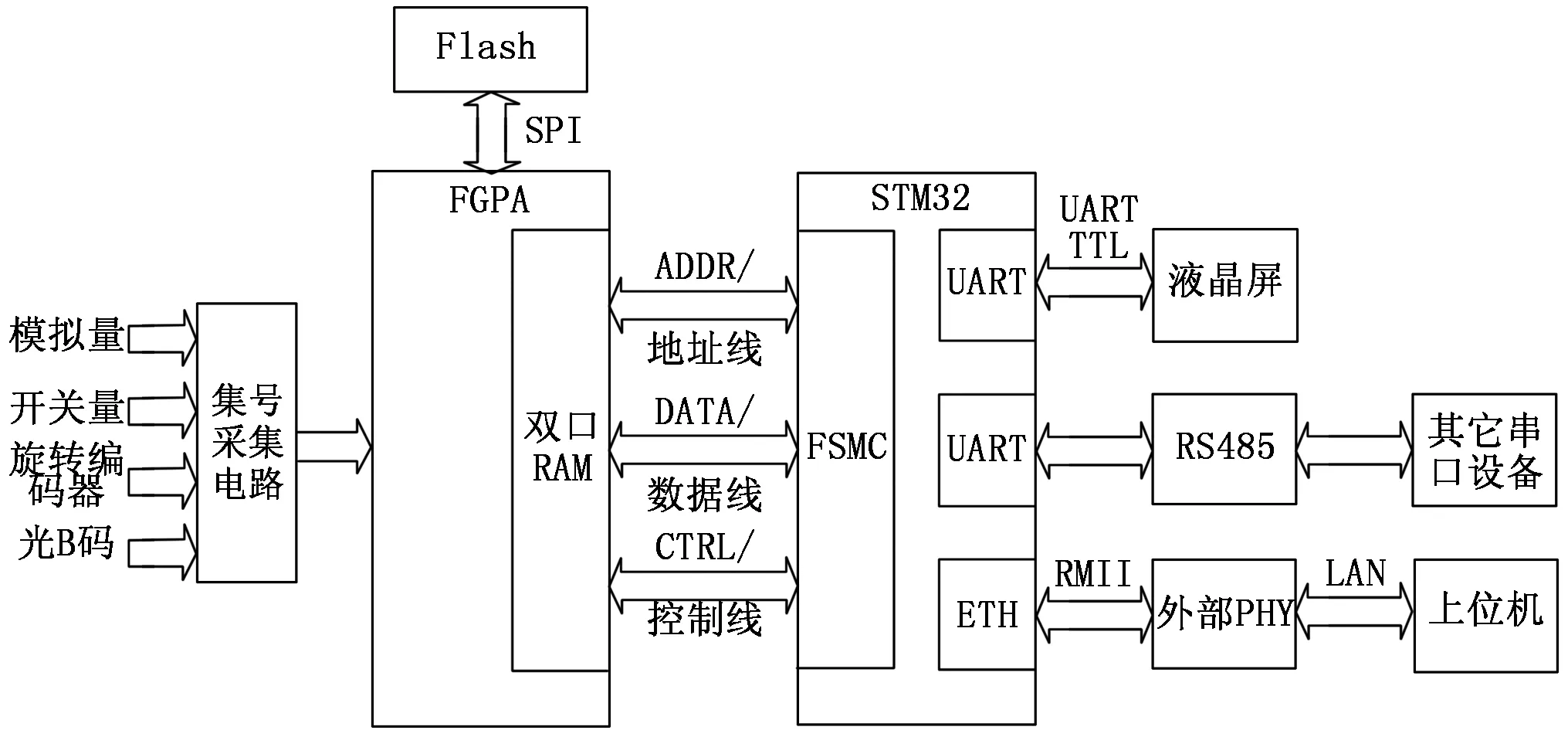

系统总体设计见图1,现场各种信号先经过信号采集电路统一处理后进入FPGA,由FPGA进行高速采集存储。在FPGA内部利用Xilinx提供的IP核构建双口RAM,A口用于FPGA读写数据,B口由STM32F407通过FSMC总线读写数据[6]。FPGA将采集的实时数据和录波数据经过处理后存储到双口RAM中,并从双口RAM中读取STM32下发的数据,实现与STM32数据交互。STM32F407用于控制、显示和管理数据,通过串口与液晶屏按私有协议方式进行通信,向液晶屏上传数据,同时接收液晶屏下发的控制指令解析执行,同时通过以太网口上传数据给上位机。系统充分发挥了FPGA高速采集、并行处理和STM32强大的处理能力和丰富的外设,可实现高速数据采集和多种应用。

图1 系统总体设计框图

系统根据功能划分共设计了3块电路板,信号采集电路板、主控板和电源板。信号采集电路板主要包括采集现场各模拟量信号,并对信号进行调理,开关量信号输入和输出电路,编码器TTL电平信号采集电路,光B码输入电路等。主控板为FPGA+STM32双处理器核心板以及外围电路,电源板为系统电源设计回路,为系统及外部传感器提供电源。

2 硬件设计

2.1 FPGA+STM32硬件设计

信号采集电路板与装置后面板端子相连,各种模拟量、开关量、旋转编码器TTL信号、光B码信号和光以太网信号先统一进入信号采集电路板进行处理,再通过排线与主控板FPGA进行相连。光纤接口可以采集基于IEC61850-9-2的互感器信号[7],B码对时功能主要是满足电力系统变电站对装置的设计要求,以达到时间同步[8]。

信号采集电路板模拟量采集单元由信号调理部分和信号采集部分组成,信号调理部分主要实现对输入的各种信号进行变换和调理,保证信号能够准确的被ADC(analog to digital converter,模数转换器)采集[9],如图2所示。信号采集部分主要实现信号模数转换,由ADC、电压参考及接口电路组成,本系统采用ADI(亚德诺半导体)公司的AD7606芯片。AD7606是一款8通道同步采集输入、真双极性模拟输入的ADC,其输入范围±5 V或±10 V可选,内部集成输入保护和抗混叠滤波器,自带片电压基准,分辨率为16 bits,每通道采样率能够达到200 ksps(kilo samples per second,千次每秒),数据输出通道灵活,既可以选择并行输出也可以支持串行输出。

图2 模拟量信号调理部分原理框图

开关量采集单元主要实现开关状态和各辅助触点信号的采集。为了保证设备的可靠性,防止现场环境对装置运行的影响,需要对输入信号进行隔离。开关量采集单元的电路如图3所示,将待测开关串联接入开关量测量电路中光耦的隔离前端,当开关闭合时,前向通道导通,进而隔离后端通道导通,输出状态改变。通过判断隔离后端输出状态,就可以确定开关量输入的状态。

图3 开关量采集电路

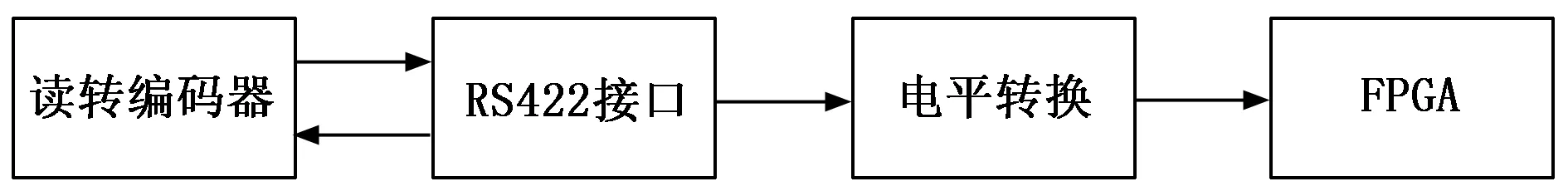

旋转编码器输出为TTL双路正交信号,电平标准兼容5V的RS422接口。由于用FPGA对旋转编码器输出信号进行解析,而FPGA的输入电压最高只能够支持3.3 V,所以还需要加一级电平转换电路。旋转编码器接口电路原理如图4所示。旋转编码器输出的TTL正交信号通过RS422接口芯片,转换成标准5 V的时序信号,再通过电平转换电路,将5 V信号转换为3.3 V的逻辑信号,最后进入FPGA解析。

图4 旋转编码器接口

光B码主要用于系统对时,光B码的接口主要是将光信号变换为电信号,再通过FPGA进行解析。其接口电路如图5所示。

图5 光B码接口

FPGA是一种掉电易失型器件,所以逻辑代码必须放在非易失性存储器内,也就是FPGA的配置芯片内,FPGA上电后从配置芯片加载程序到FPGA内部运行。系统采用主SPI(serial peripheral interface,串行外围设备接口)模式实现FPGA与FLASH配置芯片通信,该通信方式既支持原厂配置芯片,也支持第三方通用SPI FLASH,大大地降低了选型的局限性,可以选择多种配置芯片,而且通用SPI FLASH配置芯片存储空间可以足够大,不需要进行多片串联,可以降低PCB的布局难度,同时支持多线SPI模式,可以加快烧写及加载速度,其接口电路如图6所示。

图6 主SPI配置模式

STM32F407具有丰富的通信接口,包括6个速度高达11.25 Mb/s的UART(universal asynchronous receiver and transmitter,通用异步收发器)、3个速度高达45 Mb/s的SPI、3个I2C(Inter-Integrated Circuit)、2个CAN(controller area network)和1个SDIO(secure digital input and output,安全数字输入/输出接口),可连接很多的外部设备,ST公司为用户应用开发提供了简单易用的固件库,使得基于STM32微控制器开发变得快速容易[10]。

STM32通过FSMC接口从FPGA读取采集的数据,并通过UART与工业液晶屏通信,实现实时数据的定时上传显示,并能上传开关动作的机械特性曲线等非实时数据,完成开关运行状态各项参数的监测,同时接收液晶屏下发的指令,可以对开关进行相应的本地操作和参数设置,STM32与串口液晶屏通信接口电路如图7所示,另外系统还设计了几路RS485接口,作为与其它串口设备通信的预留接口,如图8所示。

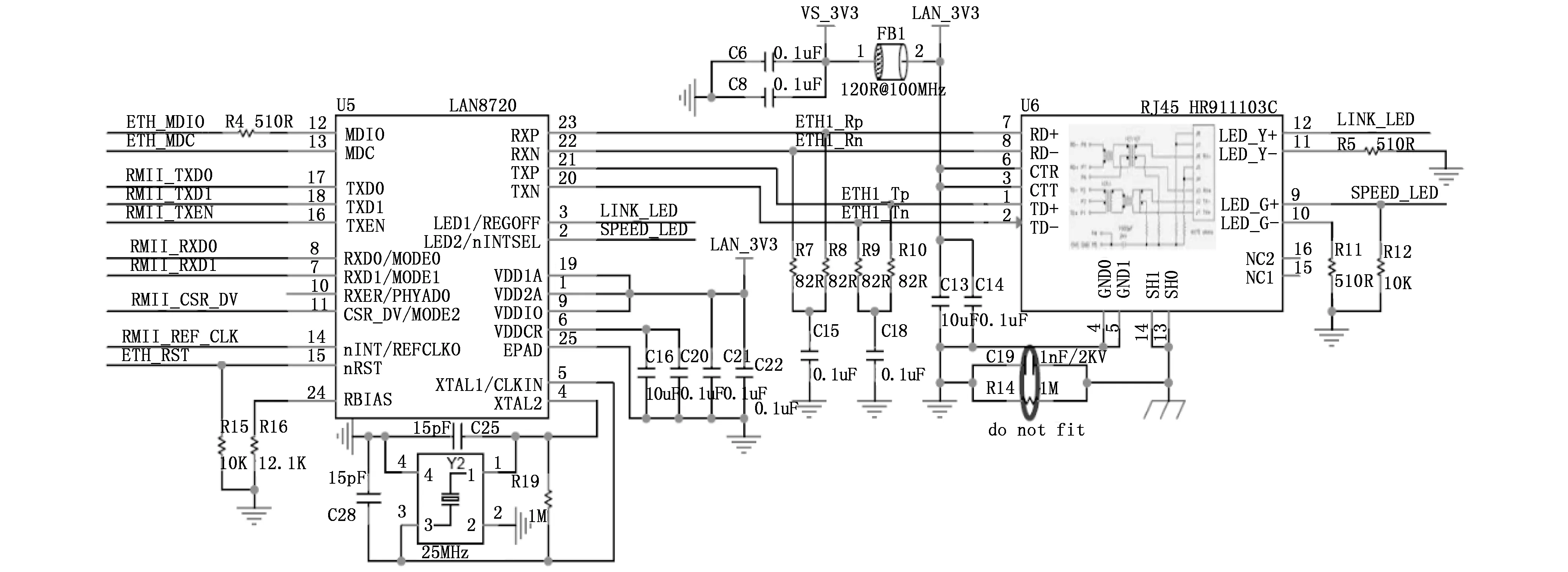

STM32F407可作为TCP服务器与上位机通过以太网接口进行通信,芯片内部自带网络MAC控制器,只需要外加一个PHY(物理层)芯片,即可实现网络通信功能。系统选择LAN8720芯片作为STM32F407的PHY芯片,该芯片采用RMII(简化介质独立接口)接口与STM32F407通信,占用IO较少,且支持自动识别交叉/直连网线功能,自带一个网络变压器的RJ45头(HR911103C),一起组成10M/100M自适应网卡,其原理如图9所示。

图8 RS485接口电路

图9 以太网接口电路

2.2 FPGA与STM32接口设计

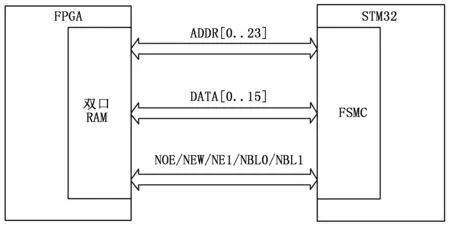

STM32F407芯片使用FSMC外设来读写外部存储器中的数据,FSMC可以用于驱动包括SRAM、NORFLASH 以及NAND FLSAH类型的存储器。在FPGA中利用Xilinx提供的IP核构建双口RAM,可实现异构系统之间快速交换数据[5]。而STM32F407就可以通过FSMC接口访问此RAM,就像访问外部SRAM一样进行数据的读写,从而实现STM32和FPGA的并行数据通信[3],其接口如图10所示。

图10 FPGA与STM32接口图

配置好FSMC外设后,STM32通过FSMC访问FPGA中数据时,通过控制引脚FSMC_NE1可以将FPGA内部RAM映射到STM32的地址0x6C000000-0x6CFFFFFF上,访问的数据宽度为16位,就像操作STM32外部存储器一样简单,直接通过地址就可以访问,FSMC控制器会根据时序自动产生地址信号、数据信号和控制信号。

地址线中的A23-A20这4根地址线用于FPGA与STM32之间的I/O控制,STM32收到相应开关的合分闸命令经过编码通过这4个I/O信号输出到FPGA,这样可以将动作命令快速准确地下发给FPGA。而地址线A19和A18作为FPGA和STM32之间的非实时数据的异步读写处理信号,来互相通知对方完成对开关动作波形数据的读写。其中A19作为STM32的输入信号,当FPGA将动作波形数据保存到双口RAM中时,会在此信号上产生一个脉冲,此信号上升沿会在STM32触发外部中断,从而通知STM32数据准备好可以进行读取,当STM32读取并保存后,会将A18电平进行翻转从而通知FPGA数据读取完成,进而可以继续进行后续数据的异步读写。

3 系统软件设计

3.1 FPGA逻辑设计

FPGA负责数据采集、数据临时存储与数据传输,以及光B码解码功能,还可用于互感器信号的采集和开关分合控制。FPGA端的逻辑功能如图11所示。其中写数据模块负责采集32路模拟量通道串行发送过来的数据以及32路开入量信号,并将其依次放入内部RAM中;通信模块负责将内部RAM中的数据提取出来,存入开辟的双端口RAM中。每次开机时,STM32端首先下发定值数据到双口RAM中,通信模块将该数据从双口RAM中提取出来,送到CRC校验模块中进行校验,如果校验无误,则将定值存入指定的定值寄存器中。启动数据采集,同时发送写使能信号给通信模块,令其开始向双口RAM中写数据。如果FPGA判断到了开关动作,则开始将RAM内缓存的数据存入外部DDR3中,直到FPGA判断到动作结束,停止存储,此时DDR3中的数据包含有完整的开关动作采样数据。然后数据经过处理后存入FIFO,由通信模块写入双端口RAM中[11],并通过I/O告知STM32进行读取。

图11 FPGA逻辑设计图

3.2 STM32程序设计

ST公司为了方便用户开发程序,提供了一套丰富的STM32F4固件库,实现了对芯片寄存器操作的封装,开发时根据具体功能需要调用相应的库函数,可以方便地实现对芯片资源的操作。

图12为STM32F407的主程序流程图,同时设计有两个中断源用于中断主程序完成特定任务。系统上电后程序首先进行中断优先级分组设置、配置系统时钟和时钟节拍、配置实时时钟、配置FSMC接口、初始化串口以太网口、配置外部中断等一系列初始化动作。初始化完成后先向FPGA发送定值配置参数,然后分别开辟一段数据缓存用于保存从FPGA双口RAM中读取的实时数据和一段指令队列缓存用于保存从串口液晶屏接收到的下发指令。之后开始主循环,首先判断是否有TCP客户端进行连接,然后读取FPGA中采集的实时数据,刷新数据缓存。接着判断指令队列中是否有完整的屏下发指令,如有则提取最前面一条指令进行解析,调用相应子程序完成规定任务。紧接着判断定时器节拍时间是否达到,如果达到则按固定时间节拍通过串口和以太网口向液晶屏及上位机上传实时数据。最后判断是否有通过中断方式读取的开关动作波形数据,有则会将波形数据发送到液晶屏和客户端。主程序循环进行以上任务,以响应液晶屏的操作及向屏和客户端上传数据。

图12 STM32主程序流程图

根据系统特点设计了两个中断以完成相应的功能,如图13所示。串口中断用于从屏接收指令数据,并保存在开辟的指令队列中。开关每次动作时FPGA将高速采样并保存开关动作时的机械特性采样数据,然后利用I/O信号触发STM32外部中断,相应的中断服务函数从双口RAM中指定区域读取采样数据,并通过内部标志位通知主程序处理[12]。设计的中断服务程序应尽量高效简洁,减少CPU中断时间,保证主程序能及时响应屏下发的操作指令及读取FPGA采样数据和后续程序的执行,保证数据及时更新和上传。

图13 STM32中断服务子程序

4 仿真与测试

STM32与FPGA之间的接口是程序的关键,需要对STM32读写双口RAM进行测试,以保证数据的正常交互。在程序中添加部分测试代码和数据,利用FPGA的仿真分析工具可以分析STM32通过FSMC读写RAM的时序图,见图14和图15。

图14 STM32读FPGA RAM时序

图15 STM32写FPGA RAM时序

STM32访问外部存储器地址时,FSMC会根据配置的控制信号线产生时序访问外部存储器,读操作时,地址线发出要访问的地址,地址建立周期结束后读使能信号线发出读使能信号,接着存储器通过数据信号线把目标数据传输给FSMC,FSMC把它交给STM32内核。写操作类似,地址线发出要访问的地址,数据建立周期期间写使能信号线发出写信号,接着FSMC把数据通过数据线传输到FPGA存储器中[4]。读写时序图满足FSMC访问外部存储器的时序要求,数据均能正常写入和读取。

5 实验结果与分析

实验现场高压开关为斥力机构,有两个断口分别是K1和K2,合分闸线圈回路连接直流电容,通过电容放电驱动相应线圈来控制开关进行合分闸。系统启动后,FPGA采集到如断口状态、储能状态、分合闸电容电压、开关行程位置、SF6气体压力等数据并写入双口RAM,STM32通过FSMC可以实时读取采集的数据,再通过串口发送到液晶屏进行显示刷新。当开关动作时,FPGA会快速采集和记录从发出动作命令开始10 ms的采样数据,记录开关动作的特性曲线,然后通知STM32进行读取,最终在界面上进行开关动作特性曲线的显示,如图16所示。由于系统可以同时监测和控制多个开关,所以对开关进行分合闸操作时,利用FSMC接口的3根地址线进行编码,由STM32通过这3个I/O向FPGA发送分合闸命令,从而实现对多个开关的可靠控制。

实验结果表明系统运行时,液晶屏上的各种状态数据都能正常显示刷新,数据交互正常。在屏上进行操作时系统能及时响应并完成相应任务,控制开关合分闸时,动作命令能快速输出,相应的机械特性波形曲线数据能及时上传,系统运行稳定可靠,满足了各项功能要求。

图16 系统液晶屏界面

6 结束语

本文采用FPGA+STM32的双处理器架构,设计了一种高压开关综合数据采集与监测系统,利用FPGA的灵活配置及高速并行性,实现模拟、数字信号的采集,利用STM32强大的数据处理能力和丰富的接口资源,实现采集数据的管理和传输。FPGA和STM32之间采用双口RAM和FSMC接口通信实现数据的交互。测试结果表明,系统采样速度高、数据传输快、运行稳定,能应用在高压开关在线监测中及其它高速数据采集和监测系统中。