基于RISC-V的计算机系统综合实验设计

2021-04-22孙卫真刘雪松朱威浦

孙卫真,刘雪松,朱威浦,向 勇

(1.首都师范大学 信息工程学院,北京 100048;2.中国科学院 计算技术研究所,北京 101407;3.清华大学 计算机科学与技术系,北京 100084)

0 引 言

目前,高校进行计算机系统教学实验主要有以下几种教学方式:其一是使用纯硬件搭建实验平台,虽该方式可深入接触计算机硬件模块,但实验操作机械死板、硬件平台开发成本较高;其二是采用软件系统仿真的方式,该方法成本较低、易于上手,但受教育者不能在实验过程中较好体会到计算机与硬件的紧密结合[1]。

为了优化上述问题,实现设计目标,本文从硬件支持、处理器构建、系统编程语言选择三方面考虑,构建计算机系统实验平台。首先,FPGA开发板能为学生提供软硬件协作的基本实验环境,并能结合特定的实验设计达到帮助学生建立计算机系统思维的目标[2-5],因此将其作为本研究的硬件模块平台。其次,RISC-V因具有完全开源、架构简单、易于移植、模块化设计等优势被研究人员用来构建新的片上处理器[6,7]。最后,Rust语言作为新兴系统编程语言致力于解决高并发和高安全性系统问题[8],目前已有许多开源社区的开发人员基于Rust语言对操作系统的开发进行了尝试。清华大学教学操作系统rCore[9]的实现就具有很好的代表性。

为紧跟技术发展并及时更新实验内容,本研究以基于RISC-V CPU的组成原理实验、基于Rust语言的教学操作系统实验作为本文的实现案例,帮助学生深入理解计算机系统组成、完善知识结构,在资源与成本受限的情况下,设计满足高校需求的软硬件结合的计算机系统综合实验平台。

1 基于RISC-V的计算机系统综合实验

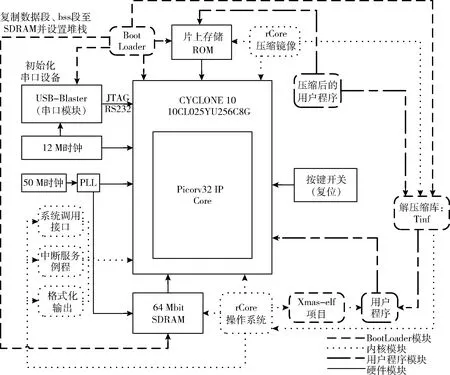

基于RISC-V的计算机系统综合实验主要包含两部分内容,其一是在FPGA开发板上搭建硬件系统实验平台以完成计算机组成原理实验,其二是在自己搭建的硬件平台上移植基于Rust语言的rCore教学操作系统并完成操作系统的各个功能模块实验。综合实验各模块组成关系如图1所示。

图1 综合实验模块

如图1所示在计算机系统实验平台中实线框表示硬件模块、虚线框表示引导模块、点线表示内核模块、长短相间虚线表示用户程序模块,各个模块按图示方式组合构成教学实验平台。

硬件模块的参考实现首先在Quartus中实现基于RISC-V的picorv32 CPU[10]封装,其次添加相关外设并完成总线互连,在完成硬件平台搭建后,将其烧录至低成本的FPGA开发板STEP-CYC10中。学生可根据计算机组成原理实验的参考实现替换CPU或其它外设模块。为检测硬件平台搭建的正确性,实验将通过RISC-V标准指令集测试对硬件平台进行测试,最终完成组成原理实验的参考实现。

软件模块的参考实现首先设计与硬件系统模块相匹配的引导程序,其次移植基于Rust语言的rCore教学操作系统。为保证能够在STEP-CYC10有限的存储资源下完成更丰富的软件功能,实验设计通过对rCore内核与用户程序进行压缩处理得到内核压缩镜像后作为数据初始化硬件平台ROM存储模块。引导程序、解压缩模块、加载模块将作为实验支持提供给学生,学生需在操作系统参考实现框架下完成最小化内核、系统调用、中断服务程序与设备驱动等实验。

通过上述硬件实验与软件实验两个层面的结合,本文完成了计算机系统教学实验平台的搭建与实验案例的展现,达到了在低成本前提下设计基于RISC-V CPU与Rust操作系统教学实验内容的目的。

2 FPGA硬件平台和组成原理实验

计算机组成原理是计算机学科的专业核心课程,该课程的教学目的是使学生理解计算机各个部件的工作原理、建立计算机的整体概念。计算机组成原理主要学习包括控制器、运算器、存储器、输入输出设备等模块的设计方法、各子系统之间的相互关系以及相互连接构成整机系统的方法。

目前,各高校普遍缺乏与计算机组成原理实验课程相配套的实验教学平台,或者存在教学平台可用性不强、成本过高等问题。针对以上问题,在满足组成原理实验基本需求的前提下,实验通过提供简易的FPGA开发板作为硬件平台,让学生使用Verilog设计CPU,实现运算器和控制器等主要部件。通过统一的外部总线接口,CPU能够与预设的各个外部设备控制器连接形成片上系统,然后烧录至FPGA中形成计算机硬件系统。

2.1 组成原理实验环境

硬件实验在STEP-CYC10开发板上搭建基于RISC-V CPU 的SoC系统,可以使用片上ROM、SDRAM、LED,数码管等外部设备。实验将硬件系统中连同CPU在内的各个部分模块化。学生在遵循统一的总线接口协议设计CPU和外设控制模块后,可以将各模块进行互连以完成SoC系统的搭建。模块化的实验平台为学生进行计算机组成原理实验提供了多种选择,学生可根据实验需求替换、增加实验模块。

2.1.1 STEP-CYC10开发板

目前,市面上通用的FPGA开发板种类十分丰富,出于对成本的考虑,本研究采用国产小脚丫STEP-CYC10开发板作为硬件平台。小脚丫STEP-CYC10开发板的FPGA芯片有16 000基本逻辑单元,板卡上集成了USB Blaster编程器、SDRAM、FLASH等多种外设,基本可以满足课程实验的需求。

2.1.2 Quartus软件

STEP-CYC10开发板上集成的FPGA为Altera系列芯片,因此实验可直接使用其相应配套的Quartus作为系统搭建环境和烧录工具。此外,Quartus中的Platform Designer还为遵循Avolon总线协议、AXI总线协议的IP核提供GUI界面的互连功能。

2.2 组成原理实验参考实现

将组成原理硬件实验平台搭建完成,给出以picore32 CPU为核心的组成原理实验参考实现并叙述CPU外接各外设接口与模块的实现。接下来分模块对组成原理实验进行详细阐述。

2.2.1 硬件实验模块化

实验设计将计算机系统的基本部件分为三大模块,即CPU、存储器、外部设备。本实验将为学生提供一个完整的SoC系统作为参考,并让学生分别完成3个基本模块,然后逐步替换至预先提供的SoC系统之中,最终完成个人的SoC系统的设计。

为保证模块之间互连的可行性,各个模块之间的连接需要遵循统一的片上总线协议。对于实现Avolon、AXI总线接口的模块,可通过Quartus对其进行连接,在连接完成后由Quartus自行实现总线类型转换。在此实验设计中,总线转接桥将作为组成原理实验的支持模块提供给学生,让学生能够将实验重心置于各模块的设计与实现上。

2.2.2 CPU的设计与实现

CPU的工作原理是计算机组成原理课程内容的核心,其设计与实现也是本实验的重中之重。通过对数据通路和控制通路的构建,学生能够掌握CPU工作的基本原理,深刻理解控制器和运算器的运行流程。本实验提供的CPU参考设计是以picorv32 CPU为核心构造的AXI总线IP核。picorv32是开源的RISC-V软核,支持多种RISC-V指令集模块,具有小体积、高频率与低功率的特点。

在学生完成自己CPU的设计前,可使用picorv32软核,通过Quartus系统集成工具Platform Designer将其封装为AXI总线接口的IP核模块以实现外部模块的互连。

2.2.3 存储器的设计与实现

存储器是存储程序的重要部件,也是计算机组成原理中必不可少的一部分。本参考实验采用片内存储与片外存储相结合的方式形成硬件系统的存储模块。

片内存储模块使用的存储资源为FPGA内部存储部件,可使用Quartus提供的ROM IP核对该存储资源进行例化。为使系统正常运行,需将上述转换为Intel Hex格式的二进制程序随SoC系统综合后再下板。

由于片内存储存储容量的局限性,软件系统的功能尤其在操作系统加载时会受到一定的影响,为此可在使用片上存储的基础上,添加片外存储资源。STEP-CYC10开发板上集成的SDRAM可提供大小为64 Mb的外部SDRAM存储资源。SDRAM的启用、初始化及基本读写操作可通过Quartus提供的sdram controller IP核完成。

实验过程中,学生需要通过软件开发工具链将程序编译转换为对应的格式用于初始化片内ROM存储资源,并理解CPU对于存储设备的寻址方式和取数过程。

2.2.4 外部设备的设计与实现

外部设备是计算机系统中的重要组成部分,一般分为输入设备、输出设备和外部存储设备,起数据传输、转入和存储的作用。STEP-CYC10开发板上集成LED,数码管、串口等外部设备。本实验设计为SoC系统添加GPIO和串口设备。在SoC上运行的程序依赖于上位机可实现简易的用户交互功能。各外部设备控制器采用Quartus提供的IP核实现,如串口模块使用RS-232 IP核、GPIO设备采用PIO IP核。通过本模块的设计,学生可以掌握外部设备与CPU交互的基本原理,外部设备控制器的工作流程。

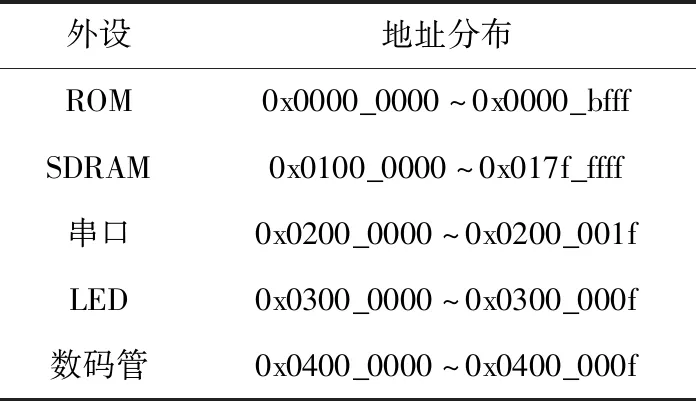

2.2.5 硬件系统的连接

CPU、存储器、外部设备3个模块实现时,若按照预先规定的总线接口,则可以直接在Quartus的Platform Designer中通过GUI连线方式将其连接成为SoC系统,极大地简化系统连接的实现流程。在连接硬件系统的过程中,需要为系统的存储设备和外部设备分配地址空间。本实验设计的SoC系统物理地址空间布局见表1。通过硬件系统连接实验,学生可加深对系统地址空间概念和外部设备寻址方式的认识。

表1 物理地址空间布局

2.3 组成原理实验建议

在计算机组成原理参考实现中,封装后的CPU与各个外设模块IP核均通过Avalon总线转换器进行互连形成完整的组成原理硬件实验平台。为排除运行故障需要通过标准测试集测试以验证系统功能,此外也可通过添加LED与数码管模块检测实验结果的正确性。

基于计算机组成原理实验的参考实现,在现有开发环境Quartus及其自带编译工具链的基础上,学生可用自行设计的CPU模块或其它模块替换参考实现中的模块。实验平台可根据学生基础提供从基本指令集到多种扩展的不同难度的实验。

3 软件开发环境和教学操作系统rCore

操作系统实验是操作系统原理课程的重要组成部分。通过操作系统实验,学生可加深对操作系统运行过程的理解。本操作系统实验要求学生在已完成的硬件SoC系统平台基础上设计和实现教学操作系统rCore核心功能、提供应用程序的运行环境。

3.1 软件开发工具链

本操作系统实验使用的实验环境为Linux系统下的开发工具链,包括RISC-V编译工具链、Rust编译工具链、qemu模拟器等。实验依据现有的RISC-V CPU设计实现小型教学操作系统rCore,并在qemu模拟器中完成核心功能的验证与调试,然后根据硬件系统适应性地调整操作系统的功能,并移植到硬件平台。在设计实现操作系统前,实验将提供RISC-V标准测试集对CPU硬件功能进行测试,以减少运行操作系统时硬件可能带来的错误。

3.2 教学操作系统rCore实验的参考实现

操作系统实验设计分为3层,分别为引导程序、操作系统内核、用户程序的设计与实现,通过上述3层结构构成完整的软件系统。

参考实现各模块关系如图2所示,引导程序设计分为ROM与SDRAM两段引导,包括设备初始化、解压缩、内核与用户程序加载等功能。操作系统内核模块实现中断处理、系统调用、用户程序解析等功能。用户程序设计为如何让操作系统加载解析ELF用户程序,跳转至用户空间执行用户程序。通过操作系统实验的3层设计实现可帮助学生理解操作系统设计方法,深化对操作系统运行过程的理解。具体参考实现如下。

图2 操作系统实验设计结构

3.2.1 引导程序设计与实现

引导程序的功能为初始化硬件系统、解析并加载操作系统内核至指定地址,并跳转至操作系统运行。受FPGA片上资源的限制,本实验针对picorv32 CPU设计了特定的引导程序。其具体的实现过程为:首先,引导程序初始化硬件设备,提供操作系统内核运行的基本环境。其次,引导程序将已经放置在引导程序后的内核压缩镜像解压至SDRAM后通过绝对跳转的方式跳转至SDRAM继续完成剩余引导启动工作。最后,引导程序跳转至操作系统入口地址完成内核启动。

为解决片上ROM存储空间不足导致内核镜像不能加载的问题,引导程序中的解压缩模块对内核映像进行压缩处理,为操作系统的启动提供支持。实验将操作系统内核镜像压缩为gzip格式文件后,转换为数组嵌入引导程序。引导程序调用解压缩库tinf[11]将内核压缩镜像解压至SDRAM,并通过绝对跳转的方式跳转至内核入口执行操作系统程序。此外,由于直接调用tinf解压缩库会占用太多的存储空间,因此实验需要对tinf解压缩库进行适应性裁剪,最终达到节省一半ROM存储空间的效果。

3.2.2 操作系统内核的设计与实现

操作系统内核的设计依赖于硬件平台资源,STEP-CYC10开发板上可用的资源包括48 KB片上存储资源、UART、GPIO、数码管等。其中,操作系统代码压缩后存储至ROM,解压缩至SDRAM后使系统能够被CPU正常加载执行。SoC中的串口设备保证了操作系统基本的输入输出功能,便于用户与实验平台上的操作系统进行交互。最后,在SDRAM开辟空间保证操作系统在运行时能够加载数据和设置堆栈等程序运行所必须的资源支持。

(1)rCore教学操作系统移植

已有的rCore 操作系统 RISC-V版本针对的硬件开发平台为 Sifive 公司发布的 HiFive Unleashed 开发板。为达到将 rCore 移植至自行搭建的STEP-CYC10 硬件平台的目标,实验需修改rCore操作系统的硬件支持,具体内容包括修改底层引导程序提供的结构函数,修改依赖的硬件资源。经过移植后,实验将选取部分rCore操作系统的功能模块作为操作系统的实验提供给学生。

(2)最小化内核实验

操作系统是一个直接在硬件上执行的程序,这使得操作系统的编写过程与一般直接在系统中运行的可执行程序不同,其最大特点是无法使用依赖于某特定平台的函数库。此外,由于目前编译器没有与硬件平台一致的目标结构,其编译也必须以特殊方式进行。最小化内核实验将作为引导实验使学生理解操作系统如何运行在裸机环境之中。实验参考过程的步骤如下。

首先,更改Rust编译的目标架构,然后使用json文件定义适用于新操作系统的目标三元组。在编译时通过--target json文件名指定[12,13]架构为riscv,端序为小端序等信息,同时指定自定义链接脚本对操作系统进行链接。

其次,由于操作系统程序无法访问标准库,需要设置不再链接标准库,不再使用Rust默认的函数入口点[12,13],使得最终编写的程序仅使用Rust语言中不依赖于特定平台的core库。

最后,使用汇编指令完成初始化堆栈功能。完成初始化工作后,通过call指令跳转到内核main函数执行。

(3)中断处理实验

中断是保证CPU及时处理外部设备请求的关键技术。中断处理程序的好坏是操作系统运行效率高低的重要影响因素。本实验的中断处理参考实现与picorv32 CPU的功能紧密结合。在picorv32 CPU中,系统预设的中断信号类型有3类,分别对应下标为0、1、2的中断掩码位。中断掩码位为0则为时钟中断,中断掩码位为1则为异常指令ebreak、ecall与非法指令,中断掩码位为3则表示访存地址不对齐异常。

中断处理函数的实现首先需根据传入的中断掩码判断中断类型,然后调用相应的处理函数。不同中断的处理函数规定了统一的参数接口,第一个参数为指向存储中断现场通用寄存器的内存指针,第二个参数为中断掩码类型,返回值为指向存储通用寄存器的内存指针。处理函数的具体实现由学生根据实验要求编写。比如,当运行遇到ebreak或非法指令时,参考实现将打印所有寄存器的值作为调试信息对软件进行调试。

(4)系统调用实验

系统调用是操作系统保护系统安全和为用户程序提供硬件资源访问的入口的有效手段。为实现对上层系统提供调用接口的功能,本实验设计通过ecall软中断的形式提供系统调用接口,并定义系统调用函数的参数传递规则。系统调用函数的参数传递规则见表2。

表2 系统调用函数参数传递规则

实验参考设计实现了两种系统调用,第一种为SBI_CONSOLE_PUTCHAR系统调用,即向console打印一个字符,通过将第一个参数a0传入的值传递给由输入输出驱动提供的print_char()函数实现功能,返回值为0。第二种为SBI_CONSOLE_GETCHAR系统调用,即向console打印一个字符,通过调用输入输出驱动提供的getchar()函数,对字符进行接收。

(5)串口驱动实验

为了完成操作系统与上位机的交互,需要实现串口功能。操作系统通过串口向上位机发送数据,上位机接收后,由串口调试工具进行显示。驱动程序的编写需针对特定的串口控制器,本实验参考实现的硬件平台中使用的是RS-232IP核。该硬件需使用的寄存器包括rxdata、txdata、status寄存器。

串口驱动函数的实现为print_char()函数与get_char()函数。print_char()函数的功能为向txdata寄存器发送数据,输入参数为需发送的字符返回值为0。在发送数据之前,调用trdy函数判断当前串口的状态,若为可发送状态,则向txdata寄存器发送数据。getchar()函数的功能为从rxdata寄存器读取数据,无输入参数,返回值为读取的寄存器数据并将其转换为char类型。在读取数据之前,调用rrdy函数判断当前串口的状态,若为可读取状态,则从rxdata寄存器读取数据。

(6)格式化输出实验

格式化输出是标准函数调用库中的常见函数,在用户交互功能中起到极其重要的作用,也可作为操作系统实验的一个调试手段。本实验设计将依赖于Rust core库实现println作为格式化输出函数,其实现需调用自行编写的底层函数。

实现格式化输出时,参考实现首先编写更为底层的用于输入输出的 putchar 和 puts函数,功能分别是输出单个字符和输出字符串,可理解为对串口驱动函数的封装。然后通过Rust core库中带有用于格式化和打印字符串的库fmt实现println。

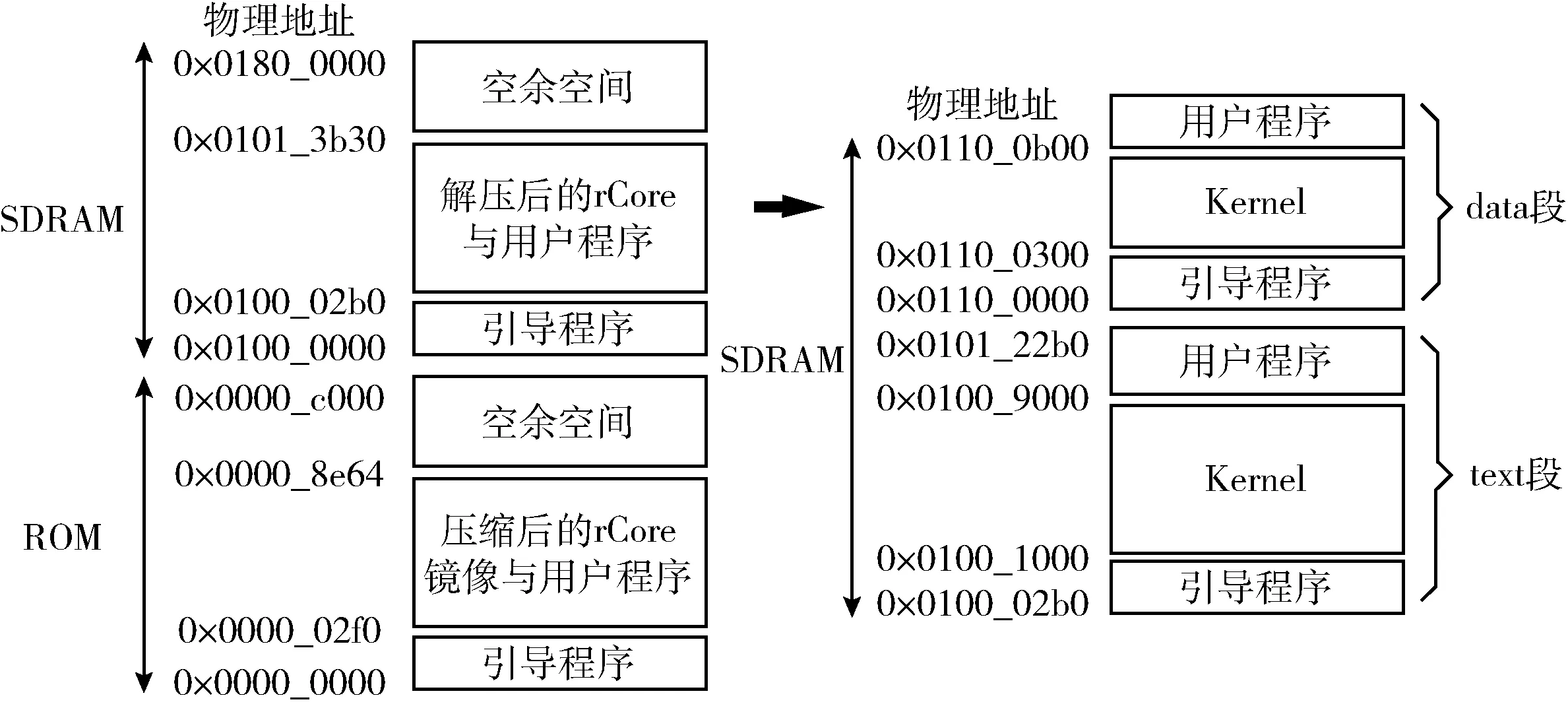

3.2.3 程序链接与加载

由于picorv32 CPU 并未实现MMU即内存管理单元,并且受到内存资源限制操作系统无法实现内存管理功能,所以实验中所有地址均为物理地址。代码与数据的地址由链接脚本指定,对引导程序的地址空间分配即为对全局的地址空间进行分配管理。比如,在链接脚本中使用MEMORY命令设置内存的起始地址与大小并指定内存类型;指定ROM存储可执行代码段以及只读数据,SDRAM存储数据段以及bss段;使用AT 命令指定数据段的加载地址等。

在将操作系统与用户程序链接完成后,本实验软件系统各部分地址分布如图3所示。

图3 操作系统与用户程序地址分布

在完成操作系统、用户程序与引导程序的链接后,通过工具链将上述3个模块合并为一个二进制文件,并转化为Hex文件作为ROM模块的初始化数据。为确保不会出现由于功能过多而导致的片内存储空间无法放置完整内核镜像的问题,实验将对操作系统内核进一步进行压缩处理。

首先,实验通过工具链将操作系统内核转化为数据段与代码段等不同程序段直接加载至引导程序指定位置,以简化操作系统内核加载流程。其次,将加载了操作系统内核代码段、数据段以及用户程序的引导程序编译链接为二进制文件,将该二进制文件进行gzip格式压缩得到操作系统压缩镜像,通过文件转换器将该压缩镜像转换为数组。最后,将数组嵌入解压缩程序。通过上述裁剪与压缩处理后的操作系统内核镜像仅占用一半左右片上存储空间,为丰富操作系统实验内容提供了可行性。

3.3 操作系统实验建议

本研究提供的操作系统实验参考实现在移植的rCore操作系统的基础上,选取部分核心功能,实现了中断处理、系统调用等模块,最终适配以picorv32 CPU为核心的SoC系统,并在STEP-CYC10开发板上成功运行。

在进行操作系统实验时,建议同学在教学提供的picorv32 CPU基础上,依据实验要求结合CPU的功能,以参考实现中给出的引导程序、解压缩模块等作为实验支持模块,在模拟器中调试,再进一步适配到STEP-CYC10硬件平台以完成操作系统的设计与实现。

4 组成原理与操作系统实验测试

为了方便故障检测,需通过标准测试集对实验平台进行测试。首先,硬件系统通过由算数和逻辑运算等指令构成的测试指令集对硬件实验中的CPU功能进行测试,测试结果通过串口进行打印。学生可通过打印结果判断实验是否通过或定位错误出现位置,也可添加LED与数码管作为支持模块协助检测错误原因。其次,软件系统通过打印中断信息、实现函数追踪与数据打印功能,若出现故障可通过串口向软件系统发送命令打印故障地址及地址对应数据深入查找故障。硬件系统与软件系统测试示例具体如下。

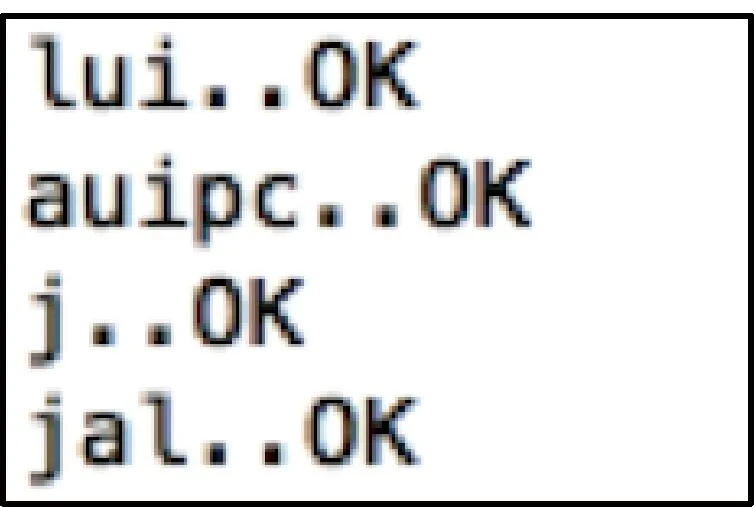

(1)组成原理实验测试结果

图4所示为基于picorv32 CPU测试指令集对搭建的硬件系统实验平台进行测试的部分结果,测试结果通过串口模块输出,打印至上位机串口调试工具。其中指令集每测试一条指令,若通过则打印“OK”。通过指令集测试验证了搭建的参考实现的硬件系统实验平台可正确运行。

图4 组成原理实验测试

(2)操作系统实验测试结果

图5所示为操作系统实验参考实现测试结果。操作系统通过串口与上位机实现了数据交互,完成了中断测试、解压缩、操作系统启动及用户程序解析等功能。同时通过串口对操作系统发出命令可实现流水灯、数码管显示、函数地址跟踪及数据监测等功能,完成了对自行设计的CPU核心功能的测试。

图5 操作系统实验测试

5 结束语

本文设计了一种计算机系统综合实验平台。该平台可根据教学需求完成计算机组成原理与操作系统实验,在有限的成本下达到综合教学的目的。实验平台以RISC-V CPU为核心在小型FPGA开发板上搭建了可用于计算机组成原理实验的硬件实验平台,同时在硬件平台上实现了rCore操作系统的移植,完成了操作系统实验的参考实现,最终形成了完整的计算机系统教学实验平台,并给出该实验平台的测试和应用方法。但由于受到硬件系统功能的限制,picorv32 CPU未实现mmu功能,因此操作系统未实现页表、虚拟内存等功能。其次由于片上存储资源不足,并未实现文件系统。针对上述问题,正在积极探索改进更换带有mmu功能的CPU,同时尝试增加片外Flash以求增加更多可用的存储资源来完善操作系统实验的功能。