基于FPGA 的载频通讯测试系统设计与实现

2021-04-20钱宏文郝刘周赵正杨文豪刘继祥

钱宏文,郝刘周,赵正,杨文豪,刘继祥

(中国电子科技集团公司第五十八研究所,江苏无锡 214035)

产品的环境可靠性试验是保障和提高军品环境适应性的重要环节,诸如军品需进行高低温工作、温度冲击、随机振动、老炼等标准化试验,才能保证产品使用过程中的稳定性。为简化研制过程中的测试操作步骤并提高测试效率,针对某传感载频数据处理板研制了专用的载频模拟及检测系统,该系统并行输出四通道载频数据,并实时检测4 块被测板卡信号处理单元的功能是否正常。

1 方案设计

载频通讯模拟测试系统能够同时并行输出四通道载频信号,并接收被测板卡的反馈,通过CAN 总线发至上位机进行处理。该系统由3 部分组成:方波电源发生器模块、信号传输背板、载频模拟及检测模块。

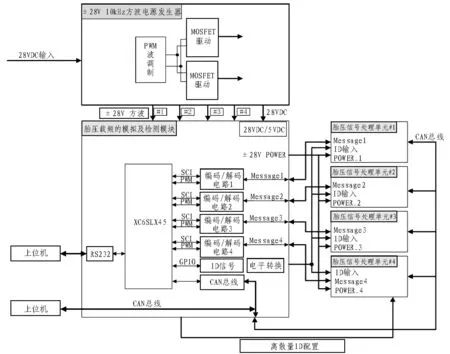

方波电源发生器模块由纯硬件实现,PWM 波调制器通过CT 和RT 参数调节PWM 产生频率,输出的两个信号VOUTA 和VOUTB 分别接在MOSFET 驱动器输入端的HIN 和LIN 引脚,控制NMOS 管的驱动输出交替变化的方波28 V 电源信号,频率由CT 和RT决定,最终输出±28 V,10 kHz 方波电源信号。整体的电路实现框图如图1 所示。

信号传输背板主要传输载频信号、ID 配置信号以及CAN 总线信号。

图1 电路实现框图

载频模拟及检测模块基于FPGA 实现,FPGA通过数字离散量向被测板卡配置ID,每块被测板卡拥有独立的ID 号,上电完成后首先配置ID。载频数据的模拟由FPGA 产生四路独立的1 kHz 和2 kHz的PWM 波,通过选择器将基波SCI 载频信号模拟数据调制至1 kHz 和2 kHz 的载频上,最终通过变压器耦合发出;数据监测部分由解码器通过配置频率为2 kHz 解调出目标数据。将检测数据以CAN 总线的形式上传至上位机进行比对,系统框图如图2 所示。

图2 系统实现框图

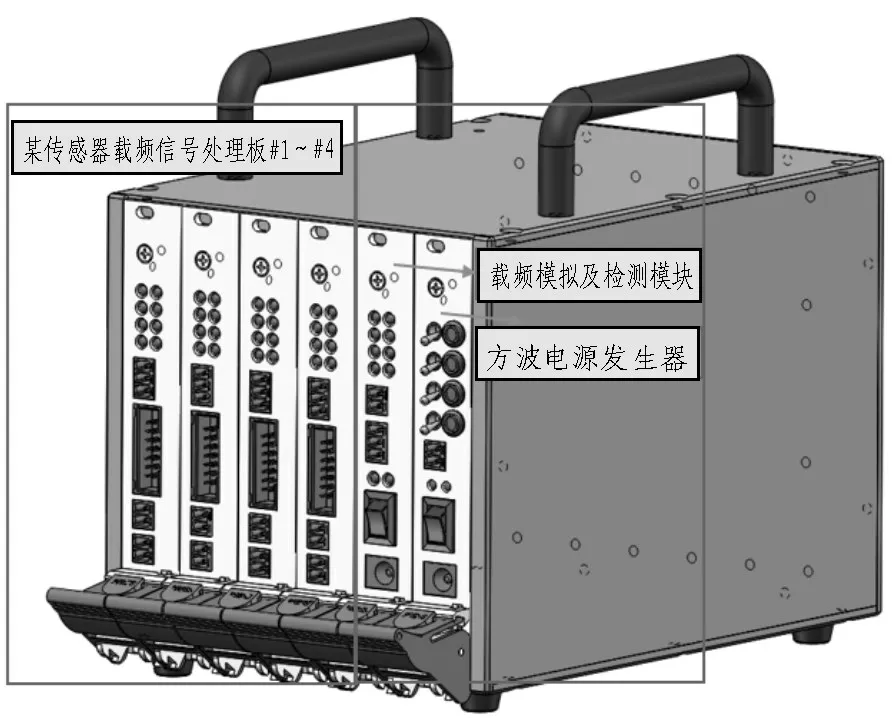

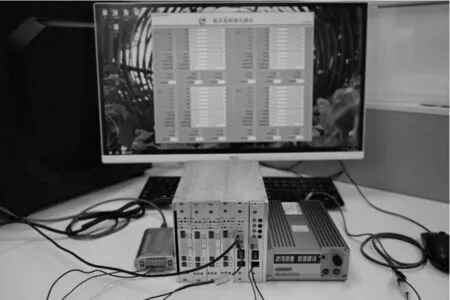

根据方案设计测试系统,效果如图3 所示,左侧4 块被测板为某传感器载频信号处理板#1~#4,右侧两块单板分别为载频模拟及检测模块和方波电源发生器模块,信号传输背板位于内部地面,上述6 张板卡均通过连接器固定在背板上。

图3 产品效果图

2 信号模拟及检测

2.1 信号模拟

根据某传感器载频信号处理单元接收1 kHz 和2 kHz 作为载波的SCI 信号,由信号模拟单元以固定间隔向4 块被测板卡模拟发送载频信号。被测板卡每接收到一次正确的信号后50 ms 内向模拟测试系统发送反馈信息。

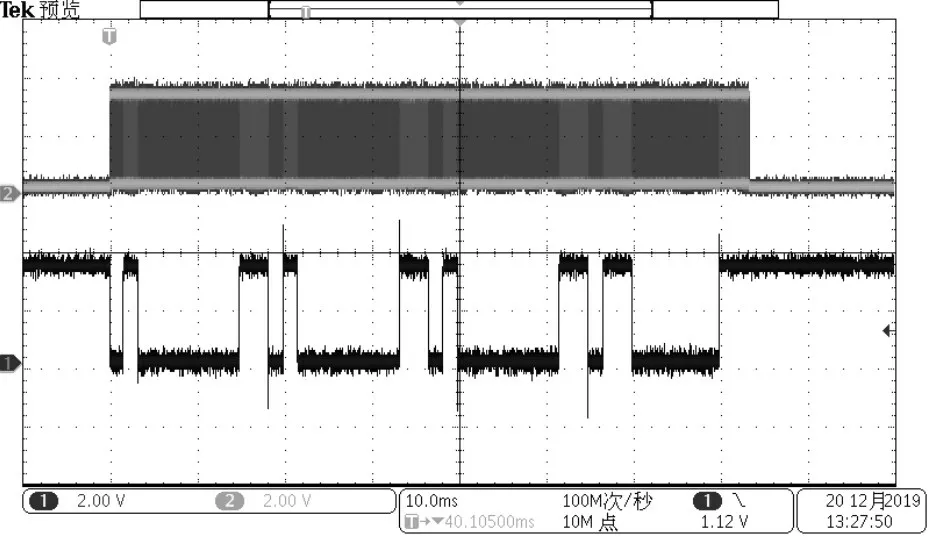

模拟检测系统并行发出4 个通道的载波信号和SCI 基波信号,经过选择器将基波信号调制至载波中,图4 所示CH1 通道为基波SCI 信号0x01、0x01、0x01、0x03,CH2 通道为调制合成后的波形。

图4 压力传感载频信号模拟

2.2 信号检测

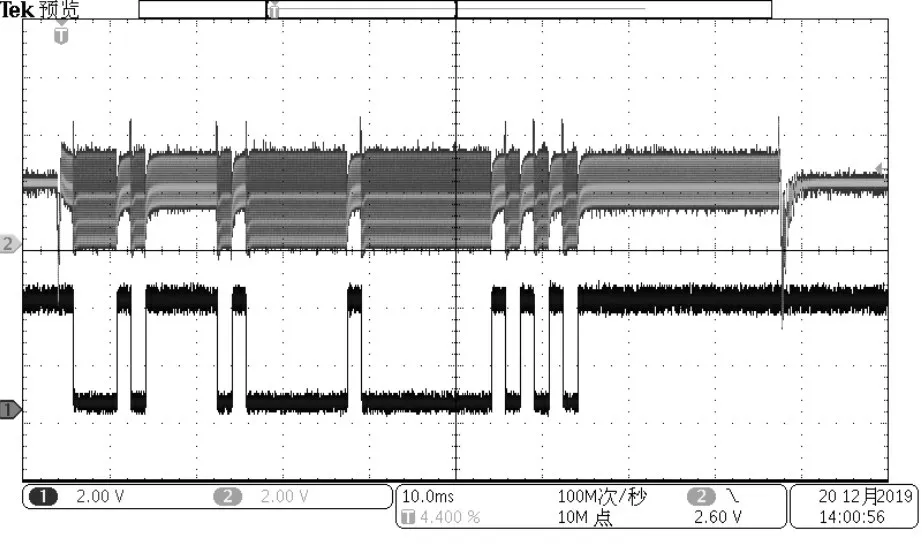

信号检测实为信号模拟的逆过程,解码出调制在1 kHz 和2 kHz 上的基波信号,由解码器芯片硬件解码,调节解码器的中心频率为1 kHz 和滤波带宽2 kHz,将目标信号解调出SCI 串口信号,FPGA 接收后通过另一路串口将信号上传至上位机,上位机以CAN 总线形式实时检测被测板卡的状态反馈数据,根据被测板卡通讯协议,与检测数据进行比对作出正误判断以实现各项测试。如图5 所示,CH2 通道为目标合成信号0xF4、0x01、0x00、0xF5,CH2 通道为解调出的目标信号波形。

图5 压力传感载频信号检测

2.3 ID离散量配置

每块被测板卡对应唯一独立ID 信号,整个系统上电后首先进行4 块产品的ID 配置,离散量由FPGA直连经过背板至载频产品,00 对应ID 号为0,01 对应ID 号为1,10 对应ID 号为2,11 对应ID 号为3。

3 软件实现

3.1 载频通讯协议

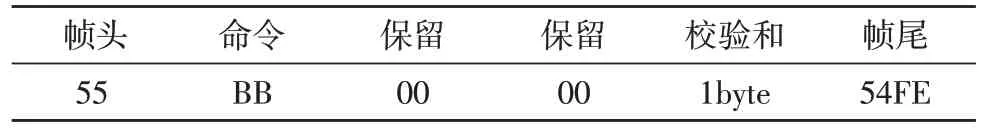

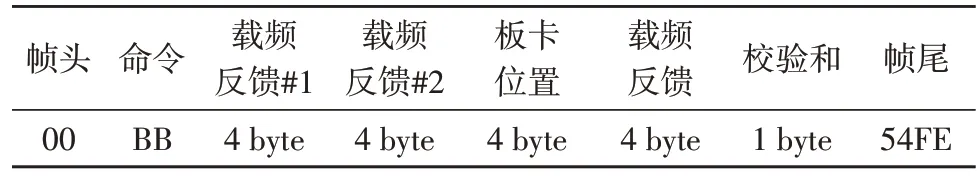

上位机下发载频通讯命令,“校验和”取保留信息之和的低8 位,载频通讯协议设置如表1 所示,波特率115 200,命令下发后四路载频信号并行发出,等待200 ms 后反馈至上位机,反馈信息共20 字节,将4 个载频信息同时反馈至上位机。载频通讯反馈的“校验和”取每个载频反馈数据之和的低8 位。载频通讯反馈信息如表2 所示。

表1 载频通讯协议的字节定义

表2 载频通讯信号反馈的字节定义

3.2 帧数据误码避免机制

FPGA 自接收到有效命令开始计时200 ms 反馈至上位机,且与上位机的串口通信具备错误可恢复机制:

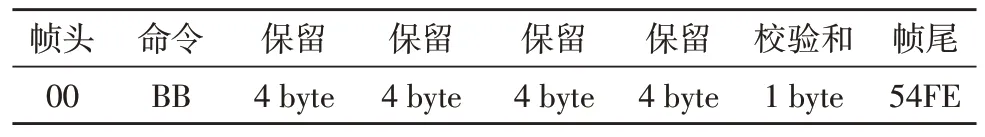

1)当接收到的命令为非有效信息(如校验错误、头尾错误)而长度正确时,反馈至上位机信息如表3所示。

表3 帧数据错误反馈的字节定义

2)当接收到的命令字节长度异常(如长于或短于正确帧长度)时,接收缓存以55 为帧头,若长于21 byte 长度,则截取前21 byte,发送帧错误反馈;若短于21 byte 长度,则直接清除,无反馈信息。

3.3 软件流程

完成一次四通道并行测试,需对产品的每项功能全覆盖,软件实现流程具体分为产品ID 配置及ID识别、指令报文、载频响应报文、载频通讯和系统状态。

1)ID 配置测试

以FPGA 直连的方式分别设置测试位ID 输出引脚为001、002、003、004。

2)ID 识别测试

采集CAN 总线上被测板卡的状态报文并进行判断,若收到ID 对应的CAN 报文,则ID 识别正确,否则测试失败并记录log 信息。

3)指令报文测试

采集压力传感载频处理单元CAN 总线指令应答,并进行判断,若数据内容正确,则指令应答成功,否则测试失败并记录log 信息。

4)载频响应报文及载频通讯测试

FPGA 接收到上位机发送的载频信息测试指令,并完成载频发送后进入检测接收模式,查看被测板卡的载频响应情况并进行判断,若数据内容与指令报文数据一致,则载频发送功能正确,否则测试失败并记录log 信息。

5)系统状态测试

CAN 总线采集每个通道压力传感载频处理单元的正常报文及实时自检状态,包括二次电源和关键器件功能检测,完成一次并行测试。

具体测试流程如图6 所示。

4 测试与验证

通过LabVIEW 显示各阶段测试数据,并将每个通道的测试结果以显示灯的形式表现,累计并记录错误log 信息,图7 所示为整体验证平台以及测试实时信息。

图7 整体验证平台及测试实时信息

5 结束语

该设计以FPGA 为控制核心,结合载频信号的调制与解调原理,实现了同时测试四路某传感器载频信号处理板的测试功能。经验证,已成功应用于该信号处理板的环境试验环节,在此基础上进行了系统测试,大大简化了测试流程,提高了测试效率,实现了对多款产品的并行测试成果。