基于FPGA 的图像边缘保护高斯滤波算法实现

2021-04-20赵冬青上官鹏储成群

康 宇,赵冬青,上官鹏,储成群

(1.中北大学电子测试技术国家重点实验室,山西太原 030051;2.北京控制与电子技术研究所,北京 100032)

在图像的生成与传输过程中,由于图像生成的工作环境、传感器材质、电子元器件特性、以及电路架构等各种原因,极易引入各种各样的噪声[1]。噪声降低了获取图像的质量,极大地增加了图像识别的难度,于是解决图像噪声成为了图像处理的一大要务。其中,高斯噪声由于其产生的普遍性成为图像处理必须解决的问题。高斯噪声属于高频噪声,噪点在图中表现为与周边像素点梯度大的特性,这一特性虽然为滤除高斯噪声提供了便利,但由于图像的边缘点一样拥有该特性,仅仅通过梯度很难区分噪点与边缘点。滤除与周边像素点梯度大的像素点,将同时滤除图像边缘点,造成图像边缘的平滑,使得图像边缘特征信息缺失,降低了图像在识别过程中的识别率。基于中值滤波与均值滤波对高斯噪声不敏感的特性,针对高斯噪声一般的处理方法,仍使用高斯滤波[2]。

随着集成工艺的不断进步,FPGA 器件也在不断发展,其可配置、功耗低、易于实现流水和并行结构的特点,提高了图像处理速度,能够满足现代图像处理对高可靠性与实时性的要求[3-4]。由于高斯滤波最佳平滑系数的确定因图而异,很难有定论,目前自适应确定平滑系数的算法复杂度较高,很难在FPGA上实现实时图像处理,造成目前FPGA 实现的高斯滤波算法有局部或整体性的过度平滑问题,导致图像边缘信息缺失,造成图像边缘模糊。

通过结合高斯滤波与动态阈值计算,划分图像边缘与离散噪点,以避开对平滑系数的计算,减少了计算量的同时也使图像的边缘信息得以保护,从而在FPGA 运算的实时性前提下提高图像滤波效果。

1 高斯滤波器及其改进方法的算法原理与仿真

1.1 高斯滤波器的算法原理

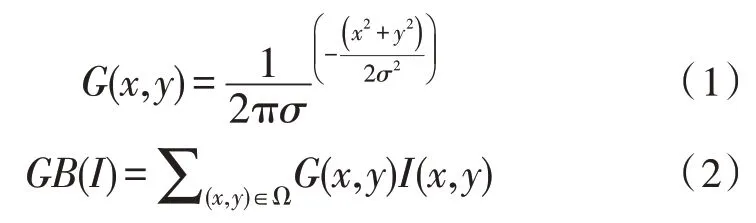

高斯滤波本质上是一种通过正态分布确定权重的低通线性平滑滤波器,相比其他线性滤波器,如均值滤波器、中值滤波器,高斯滤波器的权重由空间距离因子控制[5],在窗口中,距离待处理像素点越远的像素点权重越低,距离待处理像素点越近的则权重越高,对待处理像素点的影响力就越大,传统高斯滤波的数学表达式如下式所示[6]:

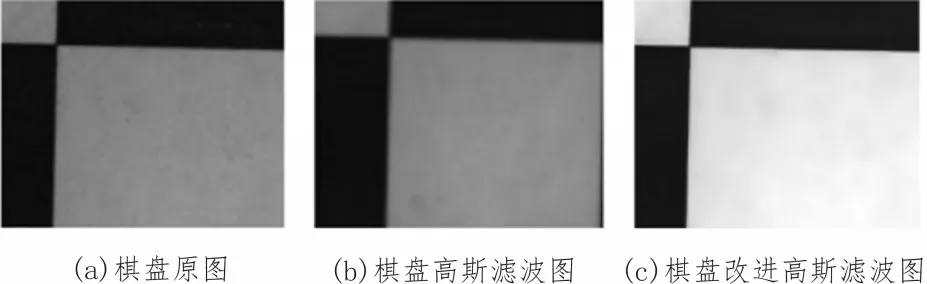

由于高斯滤波在考虑图像空间因子的同时没有考虑图像的梯度因素,这导致高斯滤波作为低通滤波器将滤除图像的高频信息,如图1 所示,在传统高斯滤波中,图(a)边缘细线将被当做噪声进行高斯滤波处理,大大降低了边缘与周边像素点的区分度,从而模糊了图像的边缘信息。检测并保护图像的高频信息将获得相比传统高斯滤波更完整的边缘信息。

1.2 改进高斯滤波器的算法原理与仿真

图1 高斯滤波图像边缘数据对比图

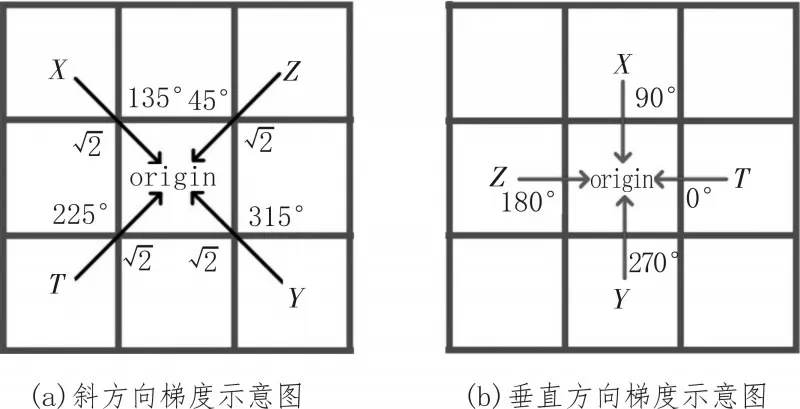

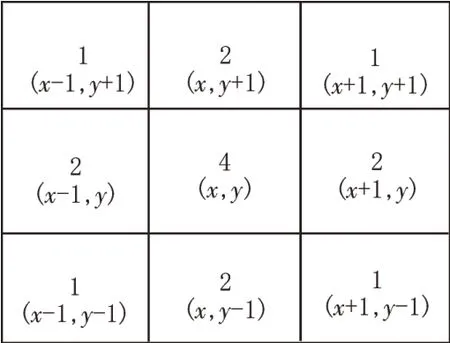

基于上文所述,高斯滤波本质上属于基于图像空间因子的平滑滤波,如引入传统高斯滤波缺失的梯度因子,就将大幅度改善传统高斯滤波破坏图像边缘信息的问题[7],在一副图像中,除图像最外侧像素点外,任何一个像素点都拥有8 个梯度值与4 个梯度方向,梯度求取原理图如图2 所示。

图2 四方向八梯求取示意图

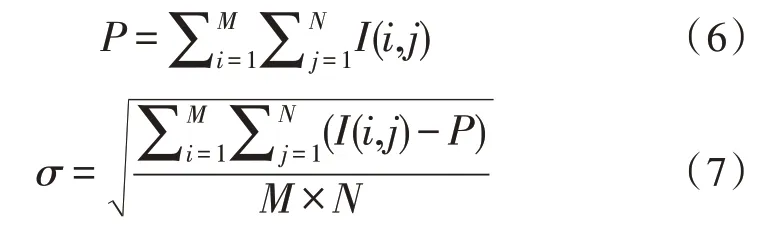

如图2 所示,八方向梯度计算方法为:

如图2 所示,求取平均梯度共需要4 个方向的8 个梯度值,其中平均梯度的求取方法如下:

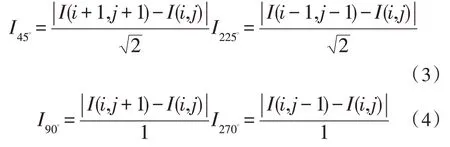

根据式(5)即可求取3×3 掩模的平均梯度,其中∑I指八方向梯度总和。求取3×3 掩模的平均梯度,通过和最终求得的阈值比较,判断该点是否为噪点,求取梯度阈值必须先求取整幅图像模板的梯度均值与像素点梯度均值的方差,而整幅图像模板的梯度均值与像素点梯度均值方差的求取方法则如下式所示:

其中,P代表整个图像梯度的均值,M×N代表整幅图像的像素数,σ代表像素点梯度与图像全局平均梯度之间的方差。在图像数据中,70%的像素点梯度均值数据在(P-σ,P+σ) 之间,仅0.3%的数据在(P-3σ,P+3σ)之外,可以认为(P-2σ,P+2σ)之内的数据为图像边缘点,大于(P-3σ,P+3σ) 的数据皆为噪声,对该点进行高斯权重滤波,通过以上运算,即可通过梯度阈值的方法判断噪点,从而形成对图像边缘保护的功用,以及精准去噪的功能[8]。

2 改进高斯滤波器的仿真测试与结论

2.1 图像的客观评价参数

图像的客观评价方法可分为全参考图像质量评价方法、半参考图像质量评价方法和无参考图像质量评价方法,全参考图像质量评价方法是目前使用最为广泛,最为成熟的评价方法。因此采用全参考图像质量评价方法进行图像质量评价,通过均方误差(MSE)与峰值信噪比(PSNR)评价方法,分别从图像与原始图像的近似程度与信息和噪声的最大功率比值两个方面入手,尽可能多角度、客观地评价图像质量[9]。

2.2 基于改进高斯滤波器的仿真结果

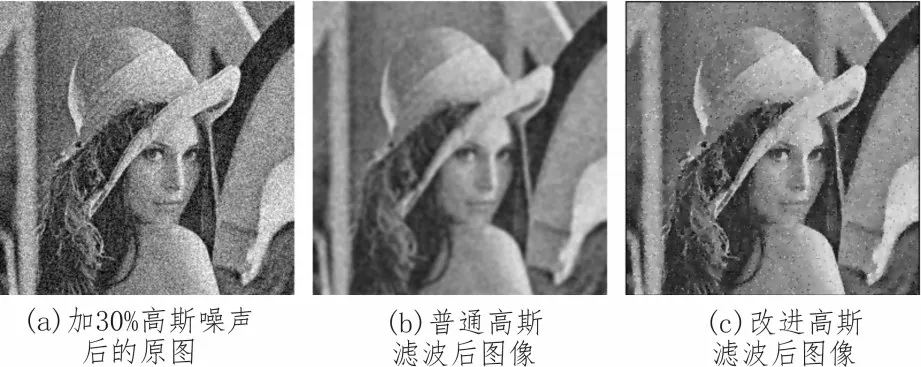

通过Matlab 仿真可得传统高斯滤波与改进高斯滤波效果图。如图3、4 所示,主观上相比传统高斯滤波,改进高斯滤波器得到的图像明显拥有更好的边缘特征与细节,而传统高斯滤波在滤波过程中明显造成了图像边缘的模糊现象。

图3 原图下的滤波效果对比图

图4 30%高斯噪声下的滤波效果对比图

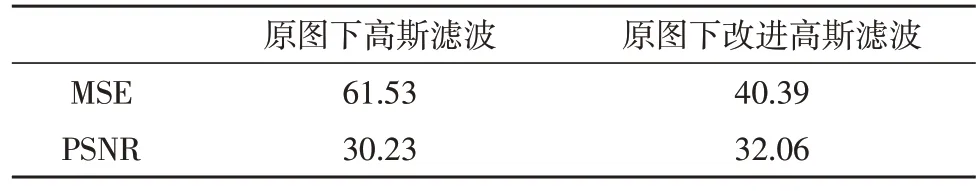

客观评价体系下,通过对比由改进高斯滤波算法得到的图像与常规高斯滤波算法得到的处理图像,如表1、表2 所示,在原图与添加30%高斯噪声的环境下,MSE 分别减少34%、26%,PSNR 分别提升6%、4%,所得数据对比如表2 所示。

表1 原图下图像客观评价数据对比表

表2 30%高斯噪声下图像客观评价数据对比表

3 改进高斯滤波器的FPGA实现

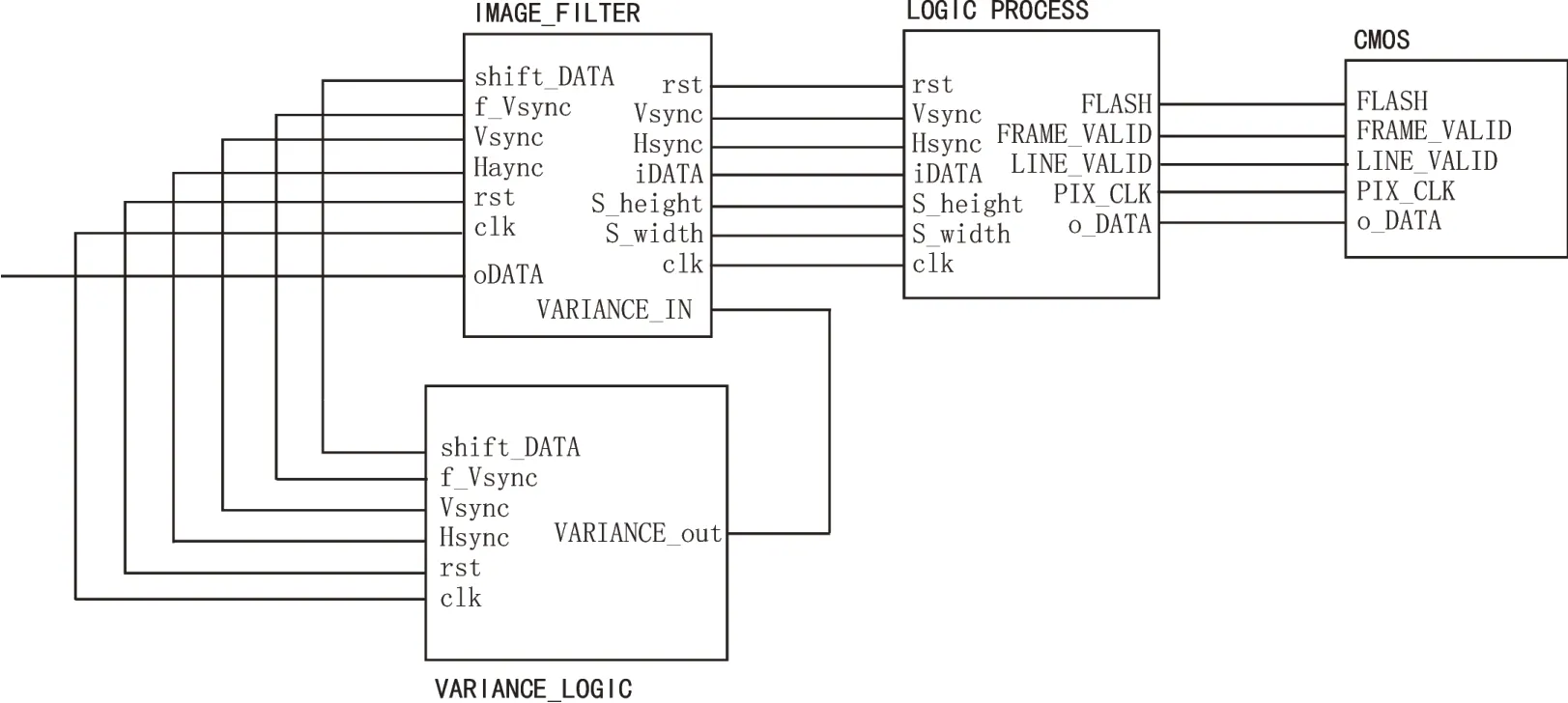

3.1 改进高斯滤波算法的RTL级电路图

由于实现的图像采集是实时性的,所以对图像处理有对实时性的要求。图5 为该改进高斯滤波器的rtl级视图,为保证实时性,流水线处理是高速设计中比较常见的设计步骤,且整个数据流的数据处理是单向操作[10],若将上述算法变为顺序执行,就将以如下流程进行:①cmos 传感器坏点矫正;②图像的高斯滤波模板创建;③利用3×3 模板求取模板梯度均值;④通过各模板梯度均值求取方差并求得阈值;⑤按与阈值的比较结果套用高斯模板权值输出或者不进行处理;⑥将输出数据输出至缓冲区,整合成为新的图片。其中阈值求取模块共需要使用4个乘法器与一个开平方ip 核。

3.2 前置坏点矫正模块

CCD/CMOS 图像传感器上的像素点存在问题、缺陷,在视频监控画面上呈现为黑色或者白色,称为坏点[11]。由上文可知,噪点检测算法是基于坏点校正后实现的,如不预先进行坏点检测,坏点对周边像素点的高梯度将大幅度影响全局梯度阈值的选取,降低检测准确率,造成大面积噪点误判,从而降低对边缘信息的保护效果。

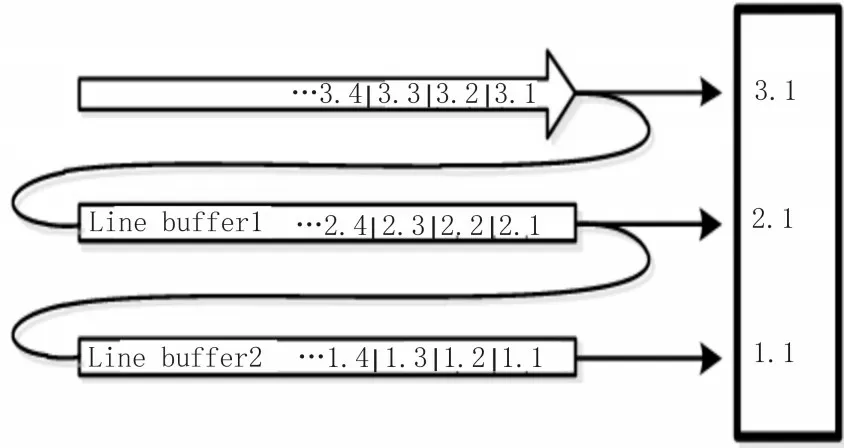

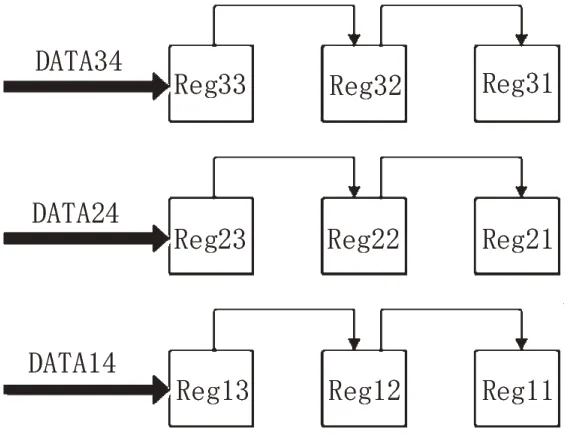

3.3 像素矩阵的行缓存与滤波掩模生成方法

如图6 所示,第一行为传感器发送而来的串行数据,而第二行与第三行皆为移位寄存器,移位寄存器大小视图像传感器行周期而定,当数据进入移位寄存器的同时也进行取数,于是当第三行数据开始进入第一个移位寄存器的时候,便出现了1.1、2.1、3.1像素点同时输出的情况,实现了生成模板的功能[12-13]。

图5 改进高斯滤波算法RTL级电路图

图6 掩模的FPGA设计原理图

如图7 所示,通过9 个寄存器存储两个移位寄存器的输出与串行输入值,则第三行第三个像素点像素值输入时将得到第一个3×3 矩阵。当第三行第四个数据输入时,第二列寄存器将赋值给第三列寄存器,随后第一列赋值给第二列,第三列存入图中最左侧的第一排,随后将重复如上步骤,直到最后一个像素点输出完毕为止[14]。

图7 3×3寄存器取数示意图

3.4 梯度阈值求取的FPGA实现

FPGA 实现梯度阈值的求取总共需要求取两个值,一个是图像整体的梯度幅度均值,一个是当前图像像素点对全局梯度均值的方差。求取图像整体平均值,要先记录第一个压入移位寄存器的像素值为初始值,随后三排输出的第一个像素点与初始值做差,并将所有差值的和存储于一个寄存器,最后将该寄存器中的差值和求取平均值,再与初始值相加,即可获得图像的整体平均像素值,将整体平均像素值带入到第二幅图像的计算中即可用于求取图像的方差[15]。方差的基本求取方法如式(5)所示。求取开根号值的方法选用xilinx公司的square_root ip核进行处理。

3.5 掩模滤波的FPGA实现

通过对梯度阈值的比较,得出该像素点为噪点,则通过高斯权重滤波的方式进行处理,如图8 所示。

图8 高斯滤波权值模板

通过对高斯滤波公式的分析,可以用近似的权值表示空间因子对像素点的影响权重,FPGA 实现高斯滤波权值模板的公式如下[16]:

式(8)的分子中每一变量代表在3×3 模板中像素点像素与该点权重的乘积,通过如上运算即可得到模板的最终高斯滤波结果。

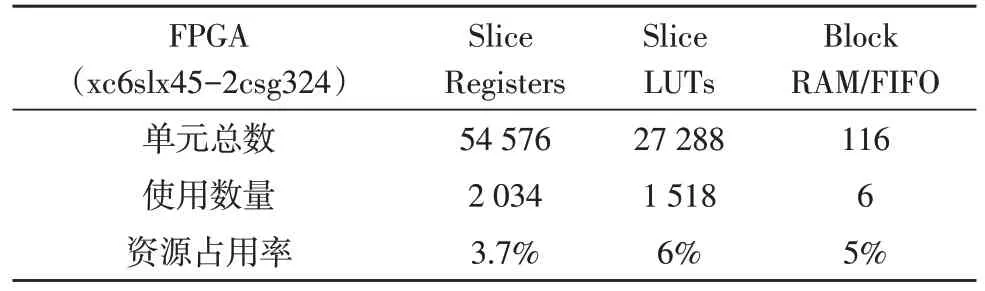

3.6 FPGA实现改进高斯滤波的资源占用情况

如表3 所示,此方案的FPGA 占用资源较少,拥有较大的改进与升级空间,满足了设计初衷,实现了改进高斯滤波的FPGA 实现。

表3 改进FPGA高斯滤波算法资源占用情况表

4 实验结果

该测试系统主要由赛灵思公司的6 系FPGA XC6SLX45-CSG324 驱动CMOS 传感器进行图像的采集与处理工作,系统通过FPGA 产生的驱动信号驱动CMOS 传感器采集图像,通过图像处理模块处理后,根据PIXCLK(像素时钟)、FRAMEVALID(帧有效信号)、LINEVALID(行有效信号)传输给上位机软件成像,还原出处理后的图像信息,实际测试平台如图9 所示。

图9 测试平台搭建图

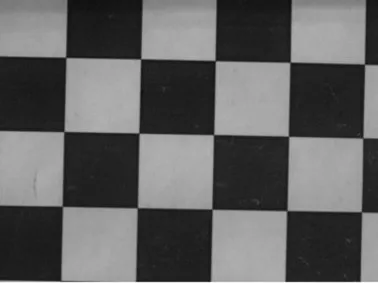

取图像原图,如图10 所示,放大后与采集到的改进高斯滤波处理过的一帧图像以及常规FPGA 处理的图像对比。

图10 未经处理的图像原图

图11 测试结果对比图

如图11 所示,可见实际测试结果基本符合仿真结果,图像边缘相比常规FPGA 高斯滤波得到的图像得到了保护,且完成了图像实时性处理输出的目标。

5 结论

该文实现了一种基于FPGA 的改进型高斯滤波器,该算法于上位机需较长的实现时间,要求主机有较强的运算能力。采用FPGA 实现该算法,大大提升了该算法的运行速率,保证了FPGA 实时图像处理能力,并将梯度因素引入到高斯滤波中来,成功经过图像处理实时输出了视频流。

且经过对比发现,基于FPGA 的改进高斯滤波算法得到的滤波后图像相比传统FPGA 高斯滤波拥有更好的边缘细节。但该算法用于较为复杂的大图像时,可能会遇到全局阈值没有典型性的问题,随着图像大小和复杂度的提高,全局阈值或被拉到较为不合理的数值,大大降低了全局阈值对图像边缘的保护效果,另外,如果对信噪比过低的图像采用此滤波方法将导致噪声被放大的情况。如采用图像分割滤波技术,将图像分区块求取阈值单独处理,或将得到更好的滤波效果,这也是下一步应着重研究的改进办法。