基于锁相环的低杂散细步进频率合成器

2021-04-09罗江虎廖志雄冯术成

孙 科,罗江虎,廖志雄,张 意,徐 伟,冯术成

(1.成都西科微波通讯有限公司,四川 成都 610091; 2.国网攀枝花供电公司,四川 攀枝花 617000)

0 引言

频率合成器是各类雷达、通信、电子对抗系统的重要组成部分,其性能直接决定了系统的性能好坏,传统的频率源技术指标包括相位噪声、杂散、频率步进、带宽范围和频率精度等,而各个指标之间往往相互制约,很难做到兼顾;而随着系统的体积越来越小,小型化也成为了频率源技术主要的发展方向之一。

国外在频率源技术上的研究一直处于领先地位,ADI、国家半导体以及Peregrine等国外芯片研制公司都拥有成熟的芯片生产、设计和制造经验,能够研发高性能的PLL芯片。ADI研发的ADF4371,输出信号带宽达0.62~32 GHz;国家半导体公司的LMX2595,输出信号可达到0.1~19 GHz,噪声基底可以做到低于-236 dBc/Hz;

国内频率源技术的研究随着系统对频率源技术的更高要求及技术的不断发展,目前主要解决的问题是高频率、小体积、快速切换、超低相噪[1]和低杂散[2]等方面的技术提升。而要实现频率合成器的小步进和低杂散性能,仅采用单锁相环是难以实现的,原因是锁相环的参考信号和输出信号非整数倍,会引入各种类型的杂散,包括小数频率步进的杂散、整数边界点杂散和鉴相杂散等;而且频率步进越小,相应的杂散抑制能力就会越差,直至差到不满足雷达系统的要求。

随着雷达系统的需求越来越高,往往对小步进和低杂散2个指标提出了兼顾的要求,国内各个频率源厂家为满足这样的指标要求,纷纷进行了各种尝试,主流的解决方法是将DDS与PLL进行各种结合,取长补短,文献[3-4]将DDS作为PLL的参考进行的尝试,通过DDS的小步进实现PLL的细步进,但是在引入DDS后,相比于单PLL,尺寸会成2.5倍的增加,无法实现小型化;文献[5]将DDS与PLL进行多次的环外混频并频谱搬移,最终实现宽带细步进的要求,但是多次的混频搬移需要多级开关滤波,在尺寸受限的情况下并不适用;文献[6]利用双锁相环实现细步进,利用前一级锁相环频率的巧妙变化避开后级锁相环的小数杂散。

国内频率源技术领域中,小型化细步进低杂散频率合成器一直是一个技术难点,利用传统锁相环,频率步进越小时,杂散水平会越差[7];而加入DDS后又无法满足小型化的要求。查阅国内外大量文献资料和相关专利后,找不到现成的解决方案,本文在传统锁相环基础上通过多环锁相的方式实现小步进,利用参考信号的巧妙变化避开主锁相环的杂散点,在满足小型化的基础上实现了小步进及低杂散。

1 频率合成基础

传统的频率合成方式由PLL、DDS、直接频率合成(梳线发生器为主)组成[8],而直接频率合成方式体积较大,在小型化要求越来越高时,直接频率合成方式的应用范围也越来越窄[9]。

1.1 锁相频率合成

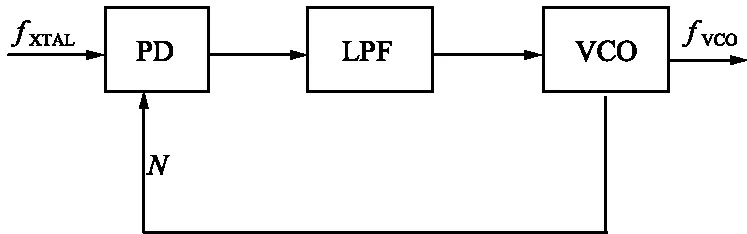

传统理解的锁相环就是利用锁相的原理将参考信号和锁相输出信号的相位同步,其本质上是一个负反馈电路,主要由鉴相器(PD)、环路滤波器(LPF)和压控振荡器(VCO)组成,如图1所示。

图1 PLL的基本构成Fig.1 Basic structure of PLL

传统锁相环参考频率与输出频率的关系为:

(1)

式中,fVCO为压控振荡器(VCO)的输出频率;fXTAL为参考输入频率;R为参考分频比;Nint,Nfrac分别为寄存器中的整数及小数N值。

锁相环内部环路滤波器的低通滤波对杂散信号有一定的抑制作用,而当输出信号与参考信号不成整数倍时,会出现小数分频杂散,特别是当杂散信号出现在环路带宽内时,是很难滤除掉的,虽然很多方法可以改善,比如很多锁相环可以通过∑-Δ调制的方式改善小数分频杂散,还有很多锁相环芯片可以调节电荷泵电流进行改善,但是仍然无法从本质上消除,特别是当频率步进越小时,杂散水平越差。这就是限制锁相环使用范围的一个主要因素,虽然通过合理的设计,可以将锁相环输出信号的相位噪声、频率范围、跳频时间和输出功率等指标做到最优,但是频率步进和杂散总是一个不可兼得的指标。

1.2 DDS频率合成

DDS频率合成技术是一种直接数字频率合成方式,其核心原理是利用奈奎斯特采样定理对参考信号进行采样, DDS作为频率合成方式的特点是频率低、步进小,而DDS参考信号的相位噪声至关重要,直接决定了DDS输出信号的相位噪声;由于DDS是一种数字频率合成方式,其杂散水平也受到限制,通常的设计方法是选用宽带频率范围内杂散较好的窄带范围进行使用。

DDS频率合成器基本结构如图2所示,在参考时钟的作用下,内部的相位累加器、相幅转换器、D/A转换形成输出幅度相位可控的模拟信号。

图2 DDS的基本构成Fig.2 Basic structure of DDS

DDS的输出频率与DDS的参考时钟的关系为:

,

(2)

式中所列的就是参考信号fSYSCLK与DDS输出信号fOUT的关系,其中FTW表示DDS的频率控制字;N表示DDS的频率控制位。

2 技术难点的探索

传统采用单锁相环的宽带频率源,当频率步进较小时,必须采用小数分频模式,而采用这种模式会引入小数分频杂散,目前单环锁相的小步进下的杂散水平仍然不能满足系统的使用要求。

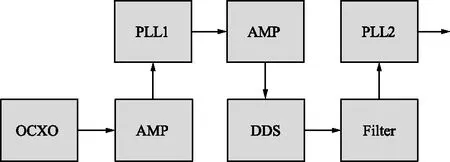

DDS数字频率合成方式[11]可以弥补细步进的缺陷,所以产生了很多DDS+PLL[12]的方案,其中最常用的一种是DDS激励PLL的方案,这种方案简单,可行性强,工程中大量使用,但是存在几个致命缺陷:① DDS的相位噪声无法达到恒温晶振的水平,最终导致锁相环输出信号的相位噪声比用晶振做参考差;② DDS杂散[13]的成倍恶化,DDS的窄带无杂散动态范围是有限的,而作为锁相环参考时,输出信号的杂散也会成20×lgN恶化[14-15],尤其是在高频输出时,杂散会恶化最多,最终导致锁相环输出信号的杂散不满足使用要求,必须进行前期大量的测试分析才能形成成熟方案;③ 无法实现小型化,相比于单环方案,这种方案的尺寸会成2.5倍增加,无法满足小型化的需求。一个传统的DDS激励PLL方案的原理框图如图3所示,其中晶振(OCXO)作为锁相环1(PLL1)的参考信号,该信号经过放大(AMP)后作为DDS参考,DDS信号经过简单滤波(Filter)后作为锁相环2(PLL2)的参考信号。

图3 DDS作为PLL参考Fig.3 DDS as reference of PLL

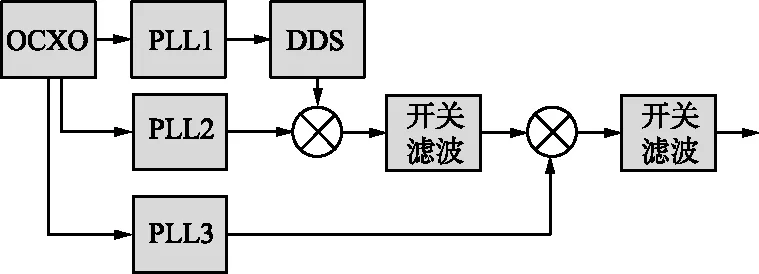

另一种实现宽带低杂散细步进信号的方法是利用DDS和PLL进行频谱搬移,如图4所示,其工作原理是在低频的窄带细步进信号,通过多次的混频搬移进行扩频,这也是很多工程中常用的方法。该方案的主要问题是:① 混频交调杂散的处理,通过多次频谱搬移后交调杂散的分量会比较多,所以在设计中必须进行复杂处理;② 尺寸大,多次变频就会有多次的开关滤波,尺寸会非常大。

图4 DDS与PLL混频Fig.4 Frequency mix of DDS and PLL

为了解决细步进问题,多环锁相的方式简单易行。多环锁相的原理如图5所示。第一级锁相环采用Hittite的集成锁相环芯片HMC833(或者HMC830)产生频率fref作为第二级锁相环的参考输入,第二级锁相环采用ADF41513通过小数分频锁相最终产生Ku波段,频率步进为1 MHz的信号。通过对参考锁相环的频率变换,可以实现第二级锁相环输出的细步进,这种方法可以替代DDS的方式,更容易实现小型化,但是仍有几个突出的问题:① 无法覆盖所有频点,当第二级锁相环采用小数分频模式时,依赖于芯片的性能,无法保证所有频点的低杂散性能,但是当第二级锁相环工作在整数模式时,又无法覆盖所有频点。② 相位噪声恶化,依赖于第一级锁相环的性能,当第一级锁相环输出信号作为第二级锁相环的参考信号时,其相位噪声会影响第二级锁相环的相位噪声;为实现第一级锁相环的输出信号可变,第一级锁相环常用芯片为HMC830或者HMC833,如图6所示,以HMC833为例,在低频时的电特性为-136 dBc/Hz@1 KHz@100 MHz。

图5 多环锁相Fig.5 Multi-PLL

图6 HMC833低频电特性Fig.6 HMC833 low frequency electrical characteristics

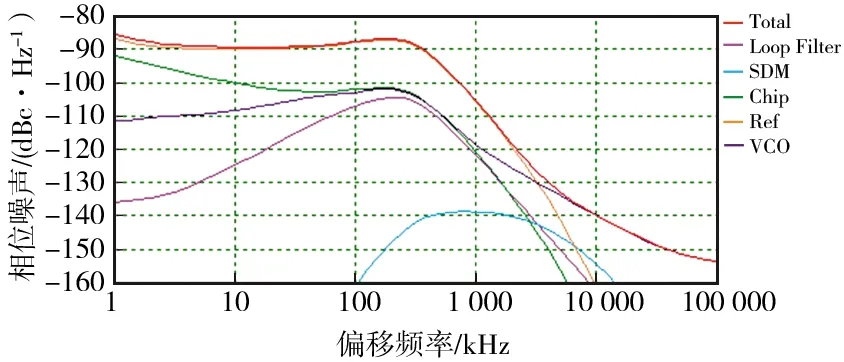

根据ADIsimPLL仿真软件,依据20 GHz参考信号的相位噪声,对双环锁相的方式进行仿真,如图7所示。根据仿真分析,当采用锁相环HMC833作为后级锁相环的参考时,输出Ku波段信号的相位噪声比用传统晶振做参考时差5 dB左右。

根据Ka波段频综模块的实际需要,结合频率源技术的发展趋势,对比上面叙述的多种方案的优缺点后,采用更易于小型化的方案进行实施。

(a) 单环锁相相噪仿真曲线

方案框图如图8所示,该方案的设计思路是:为了解决HMC833输出信号覆盖频点少的问题,用HMC833产生一段整数频点范围后,再用一个高性能点频混频后再分频进行鉴相,这样做的优点是可以减小鉴相频率的最小步进,增加输出整数频率的覆盖频点;又可以利用高性能点频源的超低相位噪声性能,提升PLL3参考信号的相位噪声水平,弥补传统方式的相位噪声缺陷。

图8 方案框图Fig.8 Scheme block diagram

3 详细设计

对于低杂散细步进频率合成器,本文通过设计一个工程实例对低杂散细步进频率合成器的工作原理进行详细叙述,该频率合成器工作于Ka波段,相位噪声指标为:-85 dBc/Hz@1 kHz;杂散抑制:-70 dBc(近端),频率步进:1 MHz。首先对各个指标进行仿真分析。

3.1 仿真分析

3.1.1 相位噪声

相位噪声是指单位Hz的噪声密度与信号总功率之比,表现为载波相位的随机漂移,重点影响了系统的目标分辨能力及探测精度,是评价频率源频谱纯度的重要指标。

传统理解的锁相环相位噪声主要指偏离主频1,10,100 kHz,1 MHz的相位噪声指标,设计中重点对环路带宽内的相位噪声进行详细设计。

锁相环的环路带宽内的相位噪声有2个经典计算公式:

(3)

(4)

式中,PNfloor为锁相环的噪声基底;fPD为鉴相频率;fOUT为输出频率。

环路带宽内的相位噪声由晶振信号、鉴相器的噪声基底、鉴相频率和N分频比共同决定。

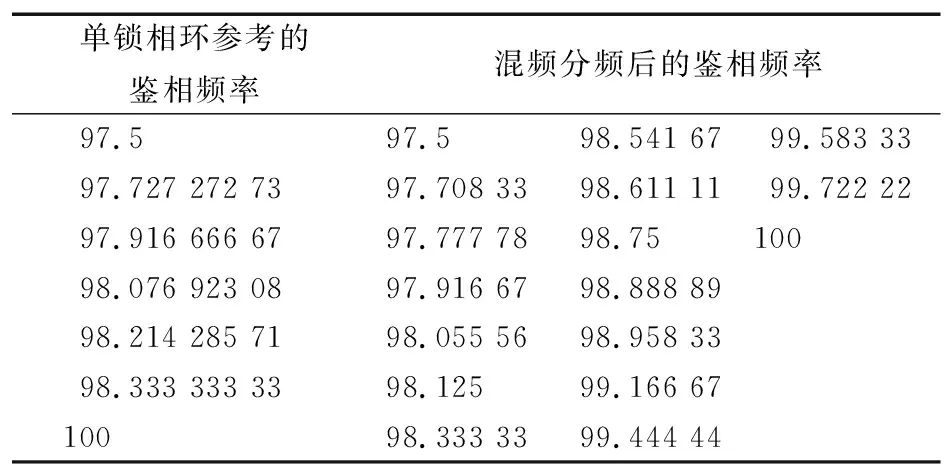

利用ADI锁相环仿真软件ADIsimPLL相位噪声进行仿真,仿真结果统计后如表1所示,随着参考信号相位噪声的恶化,输出20 GHz信号相位噪声仅有几dB的恶化。

表1 相位噪声关系

本设计实例中,由锁相环1和锁相环2混频分频产生的参考信号产生电路,相比于传统的单环锁相,其相位噪声由高性能混频本振分频决定,理论计算结果比传统单环相位噪声提升3~5 dB。

3.1.2 杂散

采用多环锁相可以利用参考信号的变化避开主锁相环小数分频较差的位置,在提升杂散水平的同时降低频率步进。

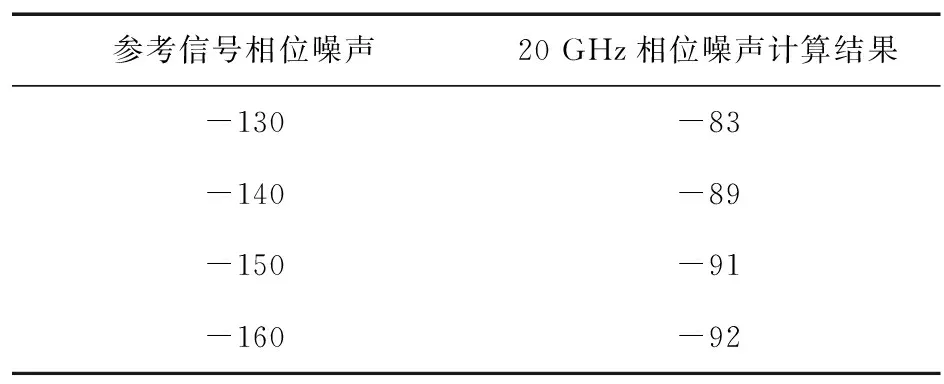

以鉴相频率从97.5~100 MHz的一段为例,经过多环混频分频后的方案比传统的单环参考方案,可用的鉴相频率增多如表2所示,这样在输出频率步进及杂散上会有更多优势。

表2 鉴相频率比较

利用仿真软件可以对输出频段范围的杂散水平进行初步的仿真预估,并作为最终设计指标及程序选择的参考如图9所示。根据表2进行相应的频率变换,通过仿真分析,可以将输出信号的杂散分量进行消除,并最终使输出信号杂散水平做的更高。

图9 杂散仿真曲线Fig.9 Spurious simulation curve

3.1.3 细步进信号的产生

利用三环锁相可以实现更细的频率步进,其核心是使PLL3的参考信号实现更细步进。传统锁相环的参考频率fref是固定值,而通过本方案的设计,将使得参考频率产生更多变化,最终更容易实现低杂散细步进的信号。

(5)

式中,fref为参考频率,一般取100 MHz;R1为参考分频比,为实现更高的相位噪声,此处取R1=2;N1的取值范围为30~60;R2的取值范围为1~62(偶数);R3的取值范围为5~160;N2的取值范围为23~511,其中包含多个可调节的小数分频比。

3.2 电路设计

电路设计中充分考虑小型化设计要求,整体设计在40 mm×55 mm×15 mm的密封腔体中,并充分考虑电容兼容影响。

实物图如图10所示,相比于传统的DDS激励锁相环的方案,省去了DDS参考电路及DDS电路,其硬件尺寸得到明显降低,极大地节省了硬件空间。

图10 本方案实物图Fig.10 Product picture of the scheme

产品局部设计图中最为关键的设计重点是:

① 高性能本振的信号串扰:高性能本振的工作频率为S波段,电磁兼容设计不合理的情况下很容易形成串扰通道,并最终使得锁相环3的输出信号中引入杂散,设计中高性能本振的供电及空间辐射进行了专门设计。

② 参考混频的交调信号:参考混频的交调信号经过PLL3的倍频放大后形成杂散,设计中通过频点选择及带通滤波2条途径进行错频和滤波处理,虽然混频后信号经过分频后可以将杂散进行20×lgN的优化,但是仍需要进行充分的滤除。

③ 设计中PLL3通带内的大部分频点可以用锁相环的整数模式产生,但是少数频点仍然需要用小数模式产生,在小数模式下的杂散需要通过参考的复杂变换来实现,这就增加了软件设计的难度,设计中需要针对小数分频频点进行专门的软件更改与调试。

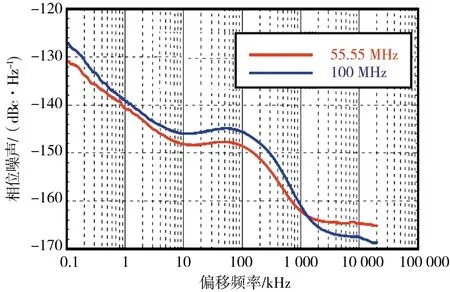

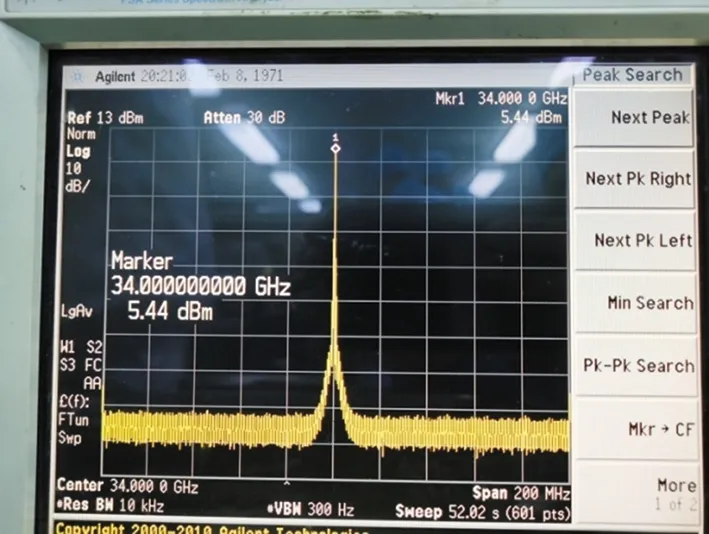

3.3 测试验证

产品测试过程中需对各个指标进行逐一分析,相位噪声在前期仿真中按照仿真值进行设计,经过初测,相位噪声的指标与仿真值接近;而杂散的指标需要进行详细的调试分析,虽然设计初可以对杂散进行仿真分析,设计过程中也可以对杂散进行预估,但是实际测试中往往有一些未知的杂散,大多数原因都是电磁兼容问题,调试中并没有一招制胜的方法,只能针对具体问题具体分析,从空间、链路和供电各个维度仔细分析,经过不断地调试改进;模块最终的测试结果满足技术指标要求,其中杂散、相位噪声的测试结果如图11和图12所示,其中杂散测试指标为-70 dBc,选取34 GHz为典型的相位噪声测试点,根据图12的测试曲线,相位噪声测试指标为-87 dBc/Hz@1 kHz,满足指标要求。

图11 杂散实测曲线Fig.11 Spurious test result

图12 相位噪声实测结果Fig.12 Phase noise test result

4 结束语

本文给出了一种基于锁相环的低杂散细步进频率合成器的设计实现方法,采用多环锁相的方案简单易行,可兼顾步进、杂散、相位噪声各个指标,且更容易实现小型化。测试结果表明,该频率合成器在各项指标上均有优异性能,尤其是在杂散分析中具有独特方法。

该频率合成器是一种性能优异的频率合成器,目前已应用于某雷达系统中,其性能亦可拓展应用于各类电子装备的本振及自检源中。