压阻式小量程SOI加速度敏感芯片设计与分析

2021-03-24杨宇新揣荣岩

杨宇新,揣荣岩,张 冰,李 新,张 贺

(沈阳工业大学信息科学与工程学院,辽宁沈阳 110870)

0 引言

MEMS(微机电系统)加速度传感器因具有体积小、质量轻、功耗低、可靠性高等优点,已被广泛应用于航空航天,汽车电子,生物医学和军事等各行各业[1-3]。随着MEMS技术的成熟,推动了加速度传感器向小量程方向的发展。小量程加速度传感器在建筑物健康监测、地质勘探和地震预警监测等应用中倍受关注[4],如桥梁工程中,需要依靠小量程加速度传感器对桥梁的振动情况进行在线长期的监测[5],从而衡量安全系数,为桥梁维护与维修提供依据。在这些应用领域,现阶段较多采用电容式加速度传感器,其优势在于灵敏度高,但是存在线性度差、工艺和接口电路复杂等缺点[6],此外,小量程的加速度传感器在使用和保存过程中很容易发生过载损坏,过载能力问题也亟待解决。

针对电容式加速度传感器的不足,本文选用压阻式加速度敏感结构,同时,为弥补压阻式加速度传感器测量小信号精度低这一不足,采用SOI(绝缘体上硅)技术制作高质量单晶硅应变电阻,设计优化一种带有微梁和支撑梁的压阻式小量程加速度敏感芯片,既解决了普通“悬臂梁-质量块”结构中灵敏度与固有频率相互制约的矛盾[7],又提高了敏感芯片抗冲击能力,同时兼有线性好、成本低的优势,可以实现对小信号的高精度、高分辨率测量。

1 加速度敏感结构

基于SOI技术设计的量程为0.1g的加速度敏感结构如图1所示,主要由敏感微梁、支撑梁、质量块和硅基框架构成,Z轴为其敏感方向。整体结构是由2片不同规格的SOI硅片(A和B)通过硅-硅键合技术制成。首先在SOI硅片(A)的顶层单晶硅薄膜上掺P型杂质作应变电阻层,热氧化二氧化硅作微梁结构层,之后将SOI硅片(A)与刻蚀有质量块和支撑梁的SOI硅片(B)直接键合构成整体结构。最后通过剥离技术去除SOI硅片(A)的硅衬底和氧化层,留下其顶层薄膜制作敏感微梁和应变电阻,并将位于微梁上4个应变电阻连成惠斯登电桥,构成加速度测量电路。

图1 加速度敏感结构示意图

2 敏感芯片设计

2.1 应变电阻

由于压阻式传感器对于温度变化较敏感,为使应变电阻温度效应最小化,根据单晶硅的应变因子温度系数(TCGF)和电阻温度系数(TCR)与掺杂浓度之间的关系[8],将电阻的掺杂浓度设定为3×1018cm-3(电阻率ρ约为0.02 Ω·cm),使得单晶硅的TCGF和TCR可以得到最佳匹配。

本文将应变电阻R设计为2 kΩ,方块电阻Rs设计为1 kΩ,则电阻厚度d=ρ/Rs=0.2 μm。下面依据单晶硅压阻元件的最大允许功耗对电阻的宽度进行确定,进而依据其宽度和阻值来选取长度。

单晶硅电阻单位面积的功耗P可写为

(1)

式中:I为通过每个电阻的电流;R为电阻阻值;w和l分别为电阻的宽度和长度;Rs为方块电阻阻值。

硅薄膜单位面积的最大允许功耗PM=5×10-3mW/μm2[9],将P=PM代入式(1),可得电阻单位宽度允许通过的最大工作电流IM:

(2)

惠斯登电桥中,采用1 mA恒流源供电时,通过每个电阻的电流I=0.5 mA,则电阻最小宽度wMin为

(3)

综上,将应变电阻的宽度设定为8 μm,则电阻长度l为

(4)

得到应变电阻各项参数为:阻值R=2 kΩ,长度l=16 μm,宽度w=8 μm,厚度d=0.2 μm,分布如图2所示。

图2 微梁上应变电阻及铝线分布示意图

2.2 结构参数设计

单晶硅材料在应变不超过500×10-6时,其应力与应变之间可以保持良好的线性关系[10],为保证传感器的输出线性和精度,同时兼顾抗冲击性能,本设计将满量程最大应变设定为300×10-6,并以微梁上最大应变和结构固有频率的乘积值(M)作为评价敏感芯片性能的指标。在设计敏感结构参数的过程中,需要先保持传感器的灵敏度基本一致,然后找出结构参数的变化与M值之间的规律,从而达到最大限度地同步提高固有频率和灵敏度的目的。

对于图1所示的加速度敏感结构,影响其性能的参数主要有质量块、主梁以及微梁的长度、宽度和厚度。通过之前的研究可知[11],当保持质量块和支撑梁尺寸不变,并施加同样的加速度时,微梁的长度和宽度越小,微梁上的应变越大。因此,微梁的长度和宽度越小,灵敏度越高,但也不能过小,要满足微梁上电阻和铝线的分布要求。基于此,初步将微梁长度和宽度分别选定为37 μm和24 μm。下面基于有限元仿真分析对量程为0.1g加速度敏感结构的其他参数进行设计。

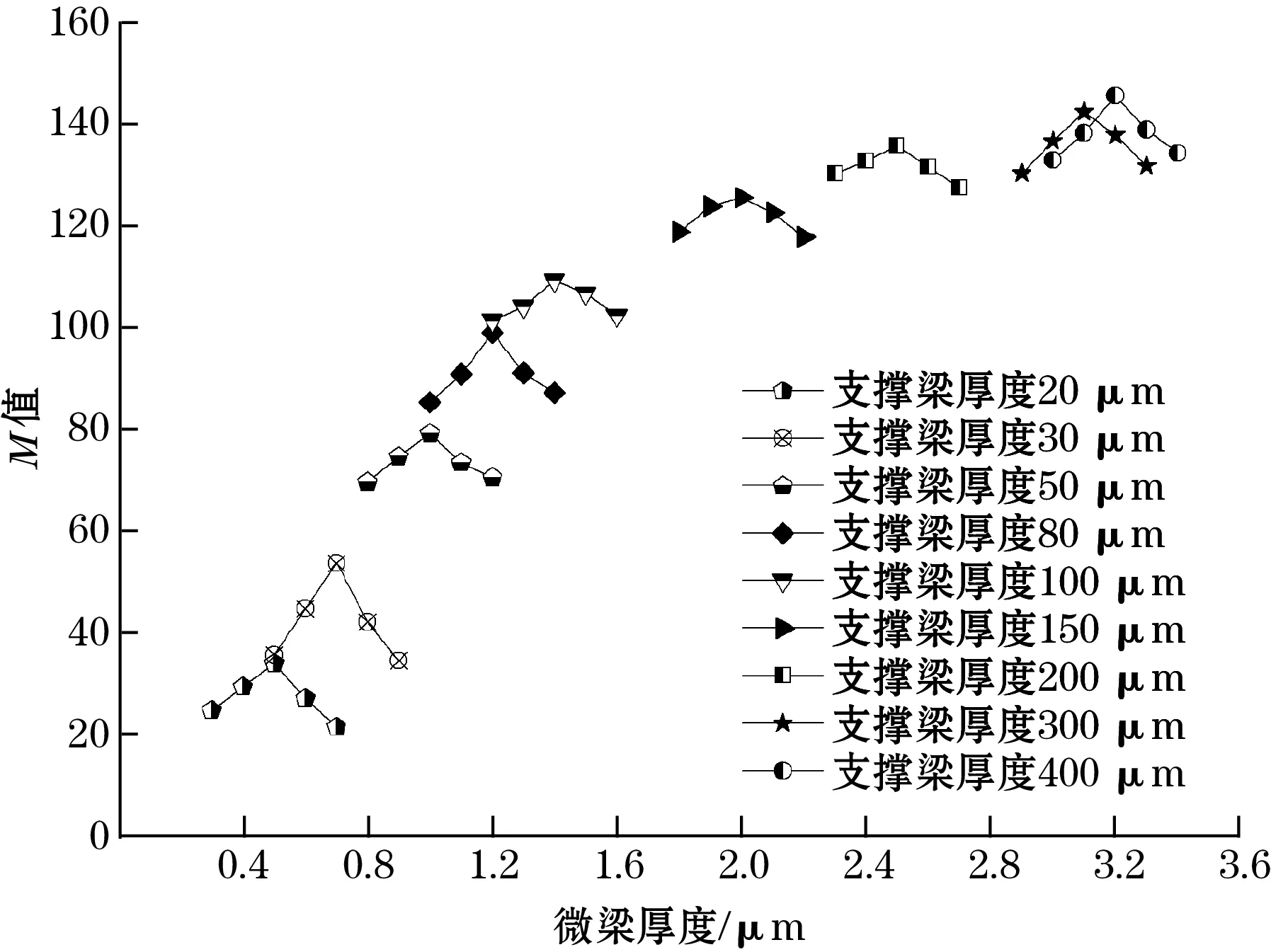

根据4英寸(1英寸=2.54 cm)SOI硅片的常规厚度值,将主体结构厚度(即质量块厚度)设置为520 μm。首先选定一个支撑梁厚度初值,同时选择一个合适的微梁厚度,调整质量块的长度、宽度以及支撑梁的长度和宽度,使得满量程时微梁两端应变达到约3×10-4,得到该微梁厚度下所对应的结构参数,并仿真出该参数下结构的固有频率,从而得到应变值与固有频率的乘积值M;再改变微梁厚度,利用同样的方法可以得到该支撑梁厚度下,一组不同微梁厚度所对应的M值。然后改变支撑梁厚度,重复上述步骤,这样便得到了不同支撑梁厚度的情况下,M值与微梁厚度之间的关系曲线如图3所示。

图3 不同支撑梁厚度的情况下,M值与微梁厚度之间的关系

从图3的仿真结果可知,对于一组给定的主体结构尺寸,总存在一个与之匹配的微梁厚度,使得敏感结构在应变和固有频率的综合性能上达到最优。将图3每组支撑梁厚度中的最大M值记为Mmax,Mmax所对应的结构参数即为该支撑梁厚度情况下的最优结构参数,由此可以得到不同支撑梁厚度与Mmax值之间的关系曲线,如图4所示。

图4 支撑梁厚度与Mmax值之间的关系

从图4可以看出,随着支撑梁厚度的增加,Mmax值也随之增加,当厚度增加到200 μm左右时,Mmax值趋于饱和,此后随着支撑梁厚度的变化其增加幅度不再明显;但支撑梁厚度如果较厚,若使微梁在满量程时产生相同的应变,则需要搭配尺寸较大的质量块,这会导致芯片面积也相应增加。因此,对于所设计量程为0.1g的加速度敏感芯片,在综合考虑Mmax值和芯片整体面积后,最终选取的支撑梁厚度为50 μm,由图3可得,该支撑梁厚度下对应的最佳微梁厚度为1 μm,其他尺寸参数如表1所示,结构的固有频率约为264.3 Hz。

表1 敏感结构的尺寸参数 μm

3 讨论

基于上述方法,在兼顾灵敏度与固有频率这两个技术指标情况下,确定了量程为0.1g加速度敏感芯片的尺寸参数。下面分别对所设计敏感芯片的输出特性、交叉耦合以及过载能力进行讨论分析。

3.1 输出特性

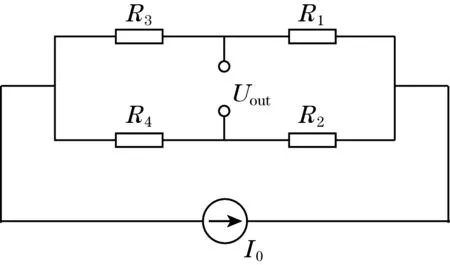

将微梁上的应变电阻按照图5所示的惠斯登电桥电路进行连接,采用1 mA的恒流源(I0)供电,其中,R1、R2、R3、R4为所设计的应变电阻。无加速度作用时,R1=R2=R3=R4=R=2 kΩ,芯片的输出电压(Uout)为零。

图5 惠斯登电桥

当敏感芯片的Z轴方向受到加速度作用时,电阻R1和R4受到张应变作用,R2和R3受到压应变作用,阻值发生变化,即R1=R4=R+ΔR1,R2=R3=R-ΔR2,芯片的输出电压可以表示为

Uout=Iin(R1-R2)=IinG(ε1-ε2)R

(5)

式中:Iin为电桥的单桥臂电流,Iin=0.5 mA;G为单晶硅的应变因子,电阻的掺杂浓度为3×1018cm-3时,室温条件下,G取值为105[12];ε1与ε2分别为电阻R1和R2上的平均应变。

传感器的灵敏度(S)为

(6)

式中:a为加速度;U(a)为加速度为a时的电压输出;Δa为加速度变化量。

采用不同的加速度作用在敏感结构上,分别对其进行应力分析,得到压阻微梁上的应变分布情况,根据式(5)便可得到该传感器芯片的输出特性,如图6所示。

图6 加速度敏感芯片的输出特性

由图6可以看出,在1 mA恒流源供电条件下,该加速度敏感芯片的满量程输出达到约34 mV,通过式(6)计算得到灵敏度为340 mV/g。

3.2 交叉耦合

交叉耦合是加速度敏感芯片一个比较关键的性能参数,反映了非敏感方向加速度信号对传感器输出的影响,交叉耦合系数过大会严重影响加速度传感器的正常输出,在应用中一般要求交叉耦合系数不超过5%[13]。

对于本文所设计的加速度敏感结构,在Z轴方向上,微梁与质量块的上表面处连接,支撑梁与质量块的下表面处连接,同时,两根支撑梁在X-Y平面内采用中心对称的方式分别布置在质量块的左右两侧,这增加了敏感结构的横向扭转刚度,使得压阻微梁在敏感Z轴方向的形变成为主要的变形方式,而X轴和Y轴的加速度所引起的变形则尽可能小,大幅度提高了敏感芯片的横向抗干扰能力。通过仿真分析可知,在敏感芯片的X和Y方向分析施加0.1g的加速度作用时,微梁上的应变分别为1.932×10-6和4.223×10-6,而满量程时芯片在敏感方向的应变可达到300×10-6左右,因此所设计敏感结构的交叉耦合系数约为1.4%。

3.3 过载能力

关于芯片的过载问题,主要取决于敏感结构上的应力分布和材料的断裂强度。当梁结构上的最大应力超过单晶硅的抗拉强度时,梁就会发生断裂,导致传感器失效。单晶硅材料的抗拉强度具有尺寸效应[14-15],即材料的抗拉强度随试件几何尺寸变化而变化的现象,所以不同尺寸的梁会表现出不同的抗拉强度。对于本文所设计的加速度敏感芯片,梁结构的断裂强度主要受厚度的影响,其支撑梁厚度为50 μm,微梁厚度为1 μm,参照文献[16],可计算得到支撑梁和微梁的断裂强度分别约为2.15 GPa和9.77 GPa。通过仿真得到,当在敏感芯片上施加8.7g加速度时,支撑梁上最大应力为72.6 MPa,远低于2.15 GPa,而此时微梁上的最大应力值达到1 μm厚度所对应的断裂强度值。因此,该芯片结构可承受不超过 8.7g的过载冲击。

对于普通的“悬臂梁-质量块”加速度敏感结构,其自身的过载能力通常只有满量程的2~5倍左右[17]。若要提高过载能力,一般需要额外设计过载保护结构,如Henry V.Allen和Stephen C.Terry等人通过减小质量块与上下硅基盖板的间距来限制高冲击情况下质量块的位移,从而实现过载保护,但过载能力也仅达到23倍量程[18],且对技术的要求很高。而本文所述结构与其相比,在无过载保护的情况下,过载能力可达到87倍量程。

4 结论

本文基于SOI技术,采用“微梁-质量块-支撑梁”结构设计了量程为0.1g的压阻式加速度敏感芯片,通过有限元法对敏感结构进行了仿真分析,结果表明,微梁的引入可以在保证灵敏度的前提下,有效提高芯片的固有频率和抗冲击能力。

所设计的敏感芯片,在1 mA恒流供电条件下,其满量程输出约为34 mV,固有频率约264.3 Hz,交叉耦合约1.4%,过载能力可达到量程的87倍。