基于FPGA 的PPM 调制解调系统设计

2021-03-11施洪生

侯 欢,施洪生

(北京交通大学 电气工程学院,北京100044)

0 引言

在数字电路设计中,现场可编程门阵列(Field Programmable Gate Array,FPGA)技术得到越来越广泛的应用,特别是在通信领域。 对于FPGA 处理器之间的通信,一般采用传统的有线连接,例如UART、CAN 等方式。 可当FPGA 处理器之间存在相对运动(即一个FPGA 处理器在旋转侧,而另一个在固定侧)时,传统有线通信方法会带来不便,而无线通信恰好适用于此情况。 将基于FPGA 的PPM 调制解调无线数据通信技术应用在风机齿轮箱应力测试中,可以规避传统有线式齿轮箱测量的种种风险[1],并且可以简化复杂的滑环工装设计,更加准确地对齿轮箱应力进行测试,同时也可以将此技术应用于其他旋转器件的信号测试场合,例如,在数控机床技术中对其卡盘在不同转速下的夹紧力性能进行实时监测;在航空航天技术中对其航空发动机旋翼的应力、扭矩等进行测试。

随着无线通信技术的不断发展,无线通信的方式也不断出现,其中各种方式的误码率、抗干扰能力和传输速率也不同,为了提高数据传输的速率和抗干扰能力,本设计采用光电耦合的无线数据传输方式,其具有良好的抗干扰能力,它利用光波作为载波对信号进行传输,可以达到很高的传输速率,在光无线通信领域中,保证一定的速率下,要求传输功率尽可能小。脉冲位置调制(PPM)是一种正交调制方式,相比于传统的开关键控(OOK)调制,它具有更高的光功率利用率和频带利用率,并能进一步提高传输信道的抗干扰能力[2]。 且基于FPGA 的脉冲位置调制(PPM)可以在高转速、数据量大的旋转件中快速、可靠地传输测量到的数据,因而本设计采用基于FPGA 的脉冲位置调制(PPM)方式。

1 系统整体结构

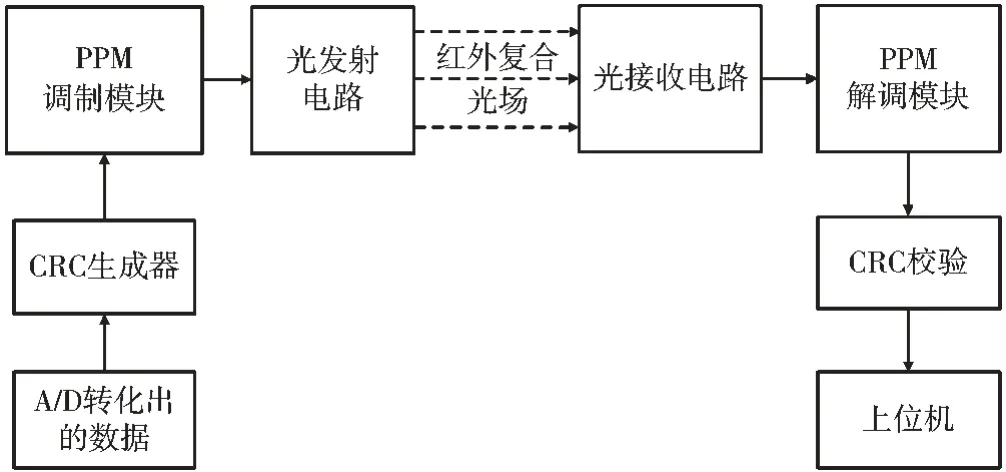

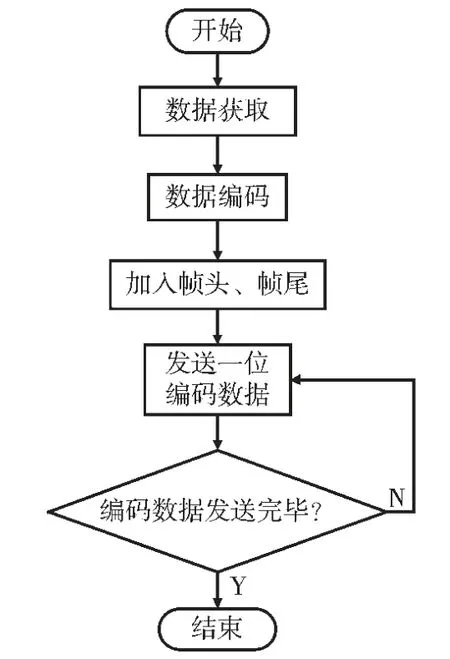

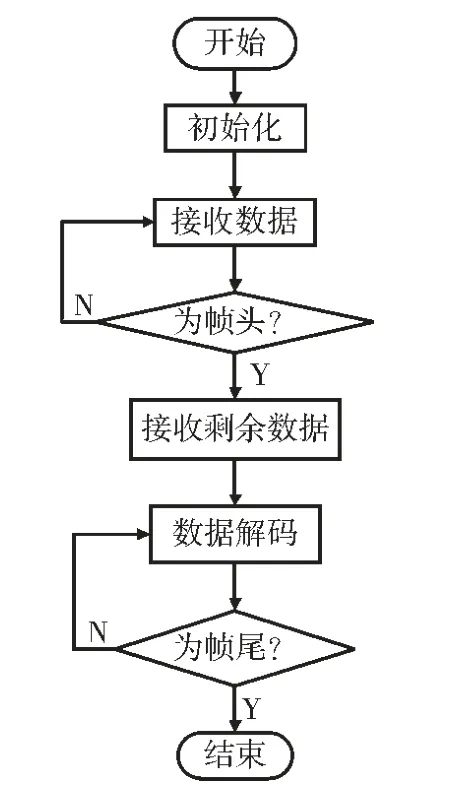

本设计由旋转侧数据的采集和发送以及固定侧数据的接收和处理两部分组成,其中发送侧包括PPM 调制电路的实现,接收侧包括PPM 解调电路的实现。 发送侧是将A/D 转化后的数据通过CRC 生成器加入CRC 校验码,再通过PPM 调制模块转化为PPM 脉冲信号,最后通过发送电路的红外发射二极管以光的形式发送出去。接收侧是将接收电路中的红外接收头接收到的数据通过PPM 解调模块将数据解码出来,再将数据进行CRC校验,最后将数据传给上位机进行显示和处理。 系统整体设计流程如图1 所示,图2 为发送数据流程图,图3为接收数据流程图。

图1 系统整体结构

图2 发送数据流程图

图3 接收数据流程图

2 PPM 调制系统设计及仿真

PPM 调制的编码方式是将输入的n 位二进制数据映射在脉冲位置调制一帧的L(L=2n)个时隙中,即在L个时隙中对应的第l 个时隙发送一个光脉冲信号[2],l 代表的是时隙的位置数。

2.1 PPM 调制系统设计

PPM 调制是将输入数据转化为不同时隙位置的脉冲,此过程可以用一个计数器来进行计数,从而在不同时隙输出脉冲的过程[2]。 以时钟脉冲作为一个标准的时间间隔,将计时过程转换成一个计数的过程。 计数模块在时钟的上升沿开始计数,当计数数据与二进制调制数据相等时就在相应的时隙输出高电平,其余时隙输出低电平,由此得到一个不同周期内不同位置上出现脉冲的波形。

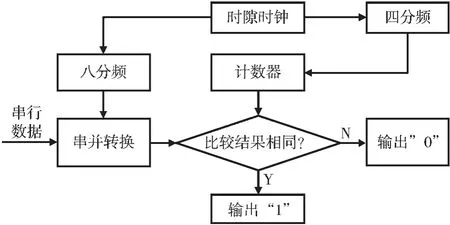

在程序设计中PPM 调制思路如下,将系统时钟分别进行四分频和八分频,其中四分频时钟是计数器的时钟信号,八分频时钟是串并转换的时钟信号。 串行数据经过串并转换模块转化为并行数据,根据系统所需要的是4PPM,将系统时钟信号经过四分频器转化为周期为4的计数器,把串并转换输出的数据和计数器数据输入到比较器模块中进行比较,如果两者相同则输出高电平,反之输出低电平。最后经过一个脉冲成形模块输出窄脉冲,这样可以减小邻近信道对其的干扰。 图4 是PPM 调制Verilog 流程图。

图4 PPM 调制Verilog 流程图

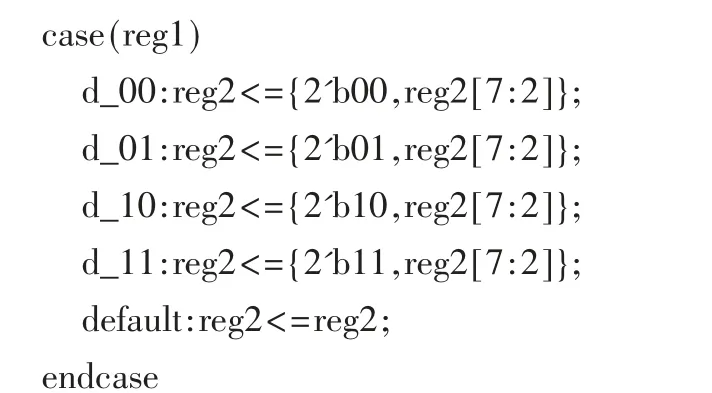

本设计是对4PPM 调制系统的设计,因此需要将A/D转化出来的数据进行串并转换,使这些数据转换为两位一组的数据,此部分是实现PPM 调制的关键。 串并转换可以通过移位寄存器来实现,本设计的思路是:先将第一位进入系统的数据缓存到寄存器中,等到第二个数据进来后,在下一个时钟的上升沿到来时将这两位数据同时输出。 其主要代码如下:

2.2 PPM 调制仿真

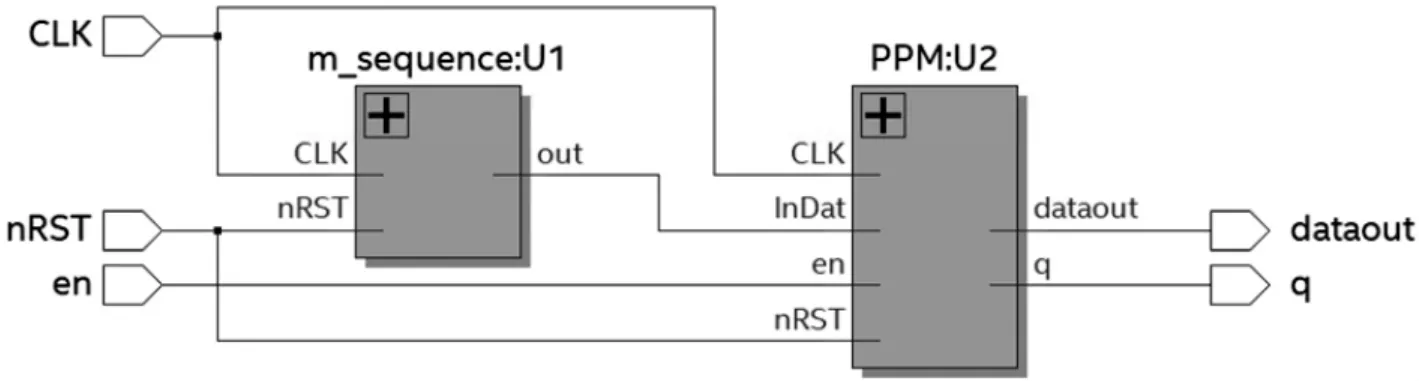

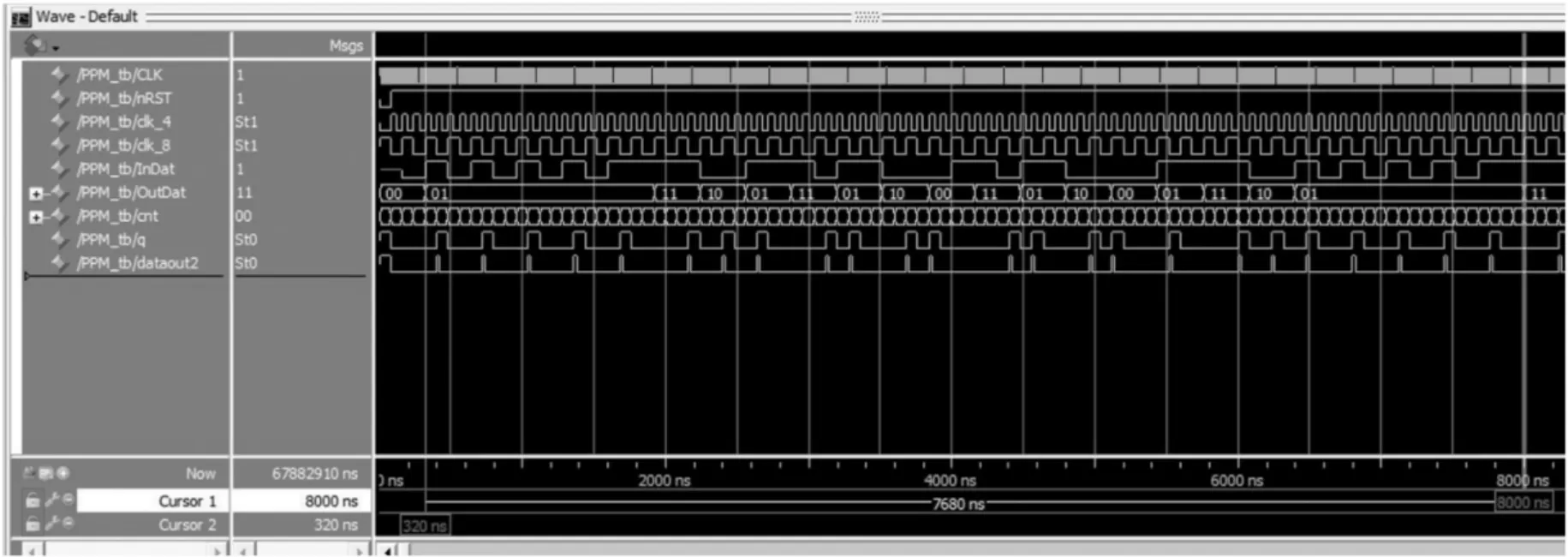

PPM 调制的顶层设计就是将调制部分的所有模块都拼接在一块,最终来实现调制的功能。 由于本设计是将A/D 转换后的数据作为PPM 调制模块的输入数据,因此编写Verilog 代码来产生一个随机的m 序列来代替A/D 转换后的数据,最后在顶层设计中将m 序列发生器和PPM 调制模块连接到一起形成完整的PPM 调制系统。 4PPM 调 制RTL 级 图 如 图5 所 示。 4PPM 调 制 仿 真 图如图6 所示。

在图6 的4PPM 调制仿真中,截取其中一段如图所示,PPM 调制系统输入的数据为InDat(0x55、0x79、0xd8、0xd8、0x55、0x79),其中0x79(0111_1001)经串并转换后变为01、11、10、01 四组数据,4 位计数器依次计数00、01、10、11,当串并转换后的数据与计数器的数值相等时,输出数据q 就为高电平,得到输出的q 之后,再将其高电平的宽度缩小为原来的四分之一,这样可以减小邻近信道对其的干扰。 由此得到了最终的4PPM 调制波形dataout。在图7 中,输入0x79 时间段中,经过了8 个八分频时钟,输入数据依次为01、11、10、01,在与计数器值count 相比较后,分别在4 个时隙的第二个位置、第四个位置、第三个位置、第二个位置输出了一个脉冲,这刚好与PPM 调制原理一致,从而证明了系统设计的正确性。

3 PPM 解调系统设计及仿真

3.1 PPM 解调系统设计

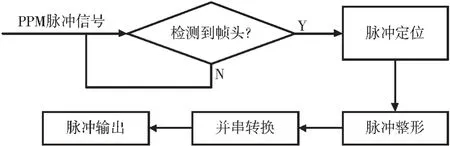

PPM 解调可以由PPM 调制的逆向思路来实现,在FPGA 解调过程中首先要提取帧同步信号,本设计中采用在数据的头和尾分别插入特殊的帧头和帧尾,以此来判断数据的起始位和终止位。 进入FPGA 的是有一定规律的脉冲信号,检测到帧头后,再确定脉冲在一帧数据中所占据的时隙位置。

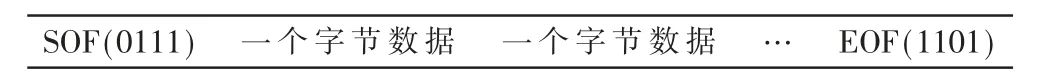

4PPM 的编码格式为:00 对应1000;01 对应0100;10 对应0010;11 对应0001,一帧PPM 数据由帧头SOF(0111)、n 个字节的数据以及帧尾EOF(1101)组成,一般每帧数据有1 到16 个字节,而且两帧数据之间的时间间隔是任意的。

表1 PPM 数据帧格式

本设计中,首先每16 个时钟周期采集1 位PPM 信号(din),所以需要一个16 位的计数器count0;解码2 bit需要采到4 位din 信号, 因此需要一个3 位的计数器count1;完成一个完整的8 位信号,需要解码2 bit 数据4次,所以还需要一个3 位的计数器count2。 其次,用移位寄存器将输入的8 位数据进行暂存以便对其进行读取,与此同时, 输出的8 bit 数据是2 bit 数据输出累加到8 bit,所以也需要移位寄存器对输出数据进行暂存。设计一个4 位寄存器reg1 对输入的数据进行移位操作,一个8 位寄存器reg2 对输出的数据进行暂存,等待8 bit 移满,就进行数据的输出;最后需要设计一个状态机来判断是否进行解码,S0 表示没有收到帧头,处于未工作状态;S1表示收到帧头,开始进行解码。 图7 是PPM 解调Verilog流程图。

图7 PPM 解调Verilog 流程图

图5 4PPM 调制RTL 级图

图6 4PPM 调制仿真

在PPM 解调过程中,将最后解调出的数据以8 位数据的形式进行数据的输出,所以需要一个8 位寄存器对数据进行缓存,等8 位数据移满后将数据输出。 其主要代码如下所示:

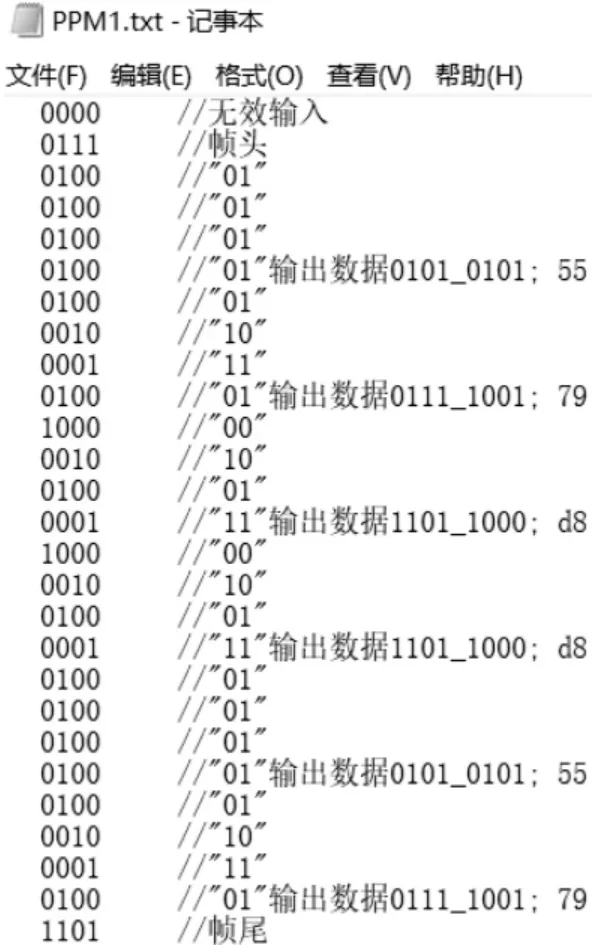

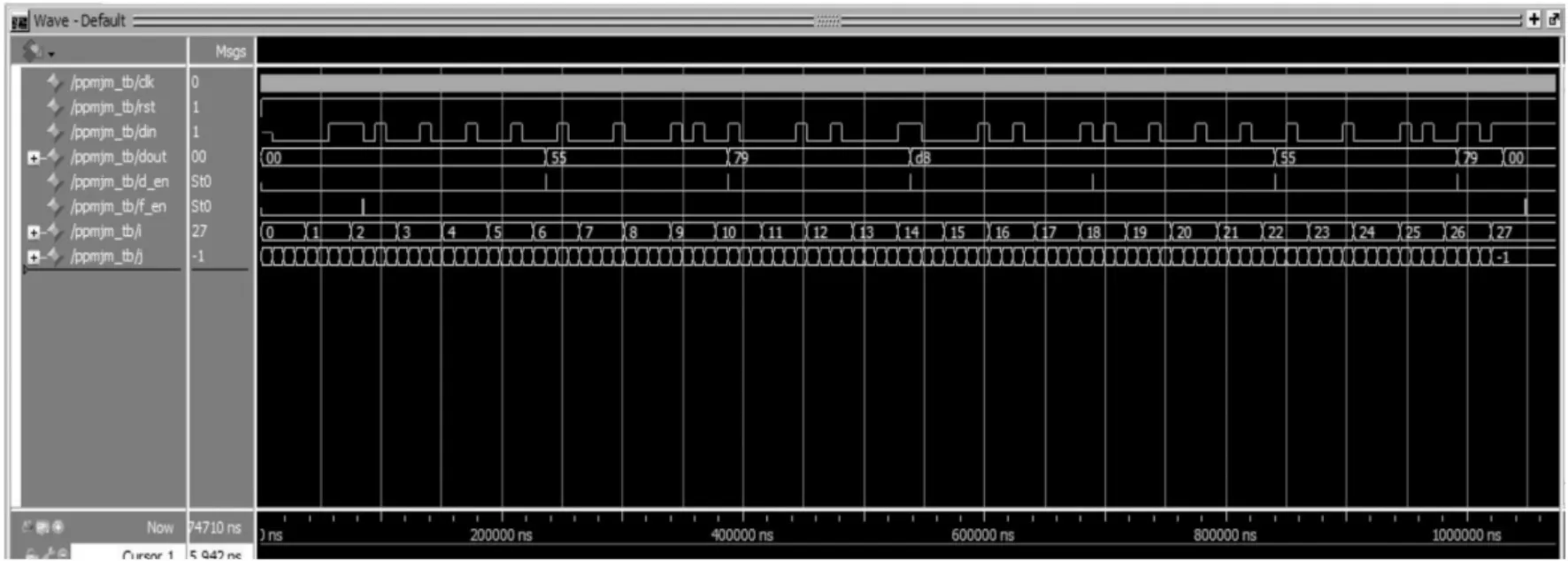

3.2 PPM 解调仿真

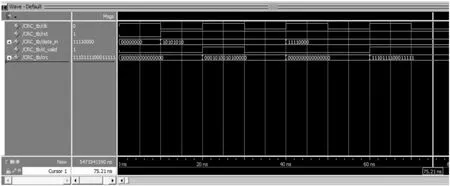

在进行PPM 解调系统的仿真之前,首先需要编写测试文件,然后将各个模块加入到工程中[3]。 测试文件通过读取"F:/PPM1.txt"的文件中的数据作为PPM 脉冲数据输入到解调系统中,其中PPM 脉冲输入数据如图8所示,4PPM 解调仿真图如图9 所示。

图8 PPM 脉冲输入数据

由图9 可以看出,解调出来的数据为0x55、0x79、0xd8、0xd8、0x55、0x79,与输入的数据一致,而且输出的数据都是在输出数据有效标志位高电平之后输出下一个字节的数据。 由此验证了代码功能的正确性。

4 CRC 生成器及CRC 校验

在红外数据传输过程中,由于存在较多的干扰源,因此数据传输的过程中容易发生错误。 采用CRC 校验进行差错控制,可以比较正确可靠地实现红外数据传输[4]。首先将A/D 转换后的数据生成CRC 码,将CRC 码加入到A/D 转换后的数据后面一起进入到调制模块,将调制出来的PPM 数据经过发射电路发送出去,之后将红外接收头接收到的数据进行CRC 码校验。 这样可以保证红外传输部分的数据更加可靠。 本设计将CRC 校验码的Verilog 实现方法展现出来。

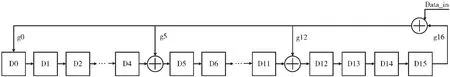

由于CRC-CCITT 的生成多项式G(X)为x16+x12+x5+1,输入数据用多项式表示为C(X),将C(X)左移R 位,用C(x)×2R除以生成多项式G(x)得到的余数就是校验码[7]。根据CRC 校验码的生成原理,采用模二除法在程序设计中得到CRC 码。 其结构图如图10 所示。 在接收侧的CRC 校验是一边接收数据一边进行校验,当把数据都接收完毕后, 最终得出的CRC 校验码与固定的CRC 值进行比较,如果两者相同则接收到了正确的数据,反之则接收到的数据有误。

在测试文件中输入数据为10101010 和11110000,最终得到的CRC 码生成器仿真结果如图11 所示,为0001010010100000 和1110111100011111, 与 用 理 论 计 算结果一致,因此确定了此电路设计的可行性。

5 结论

本文通过研究PPM 调制解调的原理,设计了基于FPGA 的PPM 调制解调系统,详细论述了调制解调系统的程序设计原理以及CRC 校验码的实现。 用Verilog HDL 硬件描述语言编写了PPM 调制代码、PPM 解调代码和CRC 校验代码,并在Modelsim 中进行了联合仿真,从仿真结果可以看出PPM 调制解调系统设计的正确性。 加入了CRC 校验,提高了后续实际应用中数据传输的可靠性。

图9 4PPM 解调仿真图

图10 CRC 电路结构图

图11 CRC 码生成器仿真图

实际应用中与仿真必定会有偏差,在后续实用化中还需要对其进行完善与改进。