面向微处理器核的片上老化检测模块设计*

2021-03-05虞致国洪广伟顾晓峰

刘 帅,虞致国,洪广伟,顾晓峰

(江南大学 物联网技术应用教育部工程研究中心 电子工程系,江苏 无锡 214122)

0 引 言

集成电路工艺特征尺寸的缩小和集成度的提高导致器件特征对缺陷的敏感度显著增加,从而给电路的可靠性带来了严峻的挑战,电路老化已成为影响其可靠性和性能的一个重要瓶颈。负偏压温度不稳定性(negative bias temperature instability,NBTI)效应是一种主要作用于PMOS晶体管的老化效应[1],导致晶体管的阈值电压增大、驱动电流减少,使PMOS管的导通时间延长,最终导致电路路径延迟增大[2]。

对于微处理器核,由于NBTI效应的存在,导致数据通路的延时增加[3],使触发器不能保证正确的建立时间,无法完成相应的功能,直接导致微处理器核的功能失效。目前,针对NBTI效应导致电路老化的研究工作有两类,一类是在芯片的设计阶段,对NBTI效应进行理论分析和验证[4],指导芯片的设计工作;另一种则是在流片后,在芯片使用阶段对NBTI效应进行在线防护,采用片上检测器模块对电路进行检测[5]。然而,目前大多数研究是对电路老化的检测,判断电路是否进入老化状态,并不能细粒度地反映出电路老化程度。

针对上述问题,本文设计了一种NBTI效应的检测电路,能够分别检测出处理器核不同关键电路的老化延时信息,准确地评估电路的老化程度,提供细粒度的防护信息。

1 NBTI效应的机理

目前,主要使用反应—扩散模型来解释NBTI效应的原理[6]。对于NBTI效应而言,根据栅源电压的不同,可将其分为两个阶段:受压阶段和恢复阶段。在受压阶段,PMOS的栅源电压处于负偏置状态,经历一段时间的受压状态以后,会导致作用力较弱的Si-H键发生断裂,导致沟道内的氢原子不断增加,最终使得PMOS管的阈值电压不断升高[7,8]。这也是NBTI效应使电路发生老化的原因所在。

在恢复阶段,其和受压阶段属于相对的情况。此时,PMOS的栅源电压处于正偏置状态,之前由于负偏置状态形成的氢离子和硅离子会重新结合形成Si-H键,随着时间的推移,沟道中的氢原子不断减少,PMOS管的阈值电压会得到恢复[9],使得电路的NBTI效应缓解。

2 延时检测模块的整体结构设计

如图1所示,延时检测模块主要由老化探测模块、老化测量模块、多路复用器模块、控制模块构成,老化探测模块嵌入到处理器的每条关键路径的末端的触发器中。捕获处理器运行时信号跳变信息,转换成脉冲信号。接下来,脉冲信号被输送到老化测量模块测量脉冲宽度,由脉冲信号的宽度反映路径的实际时间裕量。多路复用器模块来选择不同的关键路径脉冲信号输入到测量模块。同时,为减少功耗的开销,使用控制模块控制探测模块及测量模块的开启与关闭。

图1 NBTI检测电路结构

为了节省电路的面积开销,保证低功耗的要求,所有的老化探测模块共用同一个老化测量模块。同时,如果多条待测路径以同一个触发器为结束点,其可共用同一个老化探测模块。

3 片上检测模块各子模块的具体设计

3.1 老化探测模块设计

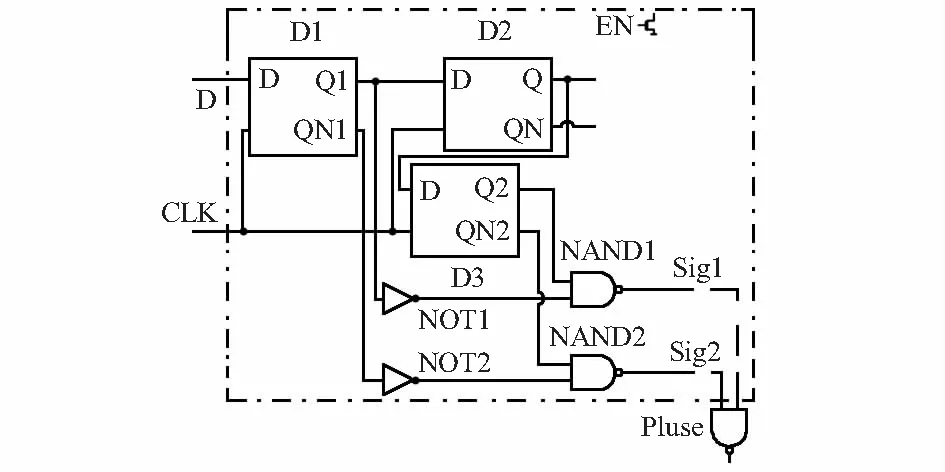

如图2所示,老化探测模块由一个锁存器、两个非门及两个NAND门组成。该模块嵌入到关键路径的D触发器中,锁存器不仅能够在模块探测路径翻转信号,还能避免毛刺的影响。

图2 老化探测模块原理

当使能信号EN为1,整个电路进行工作。信号D为关键路径上时序信息,通过老化探测模块以后,分别得到Sig2,Sig1信号,然后与老化测量模块中的第三个与非门生成脉冲信号Pluses。当不需要探测的时候,可以将EN设为0关闭探测模块。如图3所示,使能信号开启时,老化探测模块开始工作。在CLK=0时,即为低电平信号时,信号D上的信息变换通过主锁存器,使得Q1端的信号变化,这个变化最终会导致Q2输出发生转换。其模块中的两个NAND门与测量模块的另一个NAND门构成异或门,捕获到0—1或者1—0的翻转信号并生成脉冲信号。

图3 老化探测模块时序

假设路径的时间裕量t为D转换到达时间与时钟上升沿之间的时间差。但是在探测器模块实际产生的脉冲宽度为t+T/2,这是因为NAND门的脉冲宽度由Q1 转换和Q2转换之间的时间差确定,而两者之间存在锁存延迟,因此有T/2个周期被加入到脉冲宽度中。实际的脉冲宽度需要减去加入的半个周期。

3.2 老化测量模块设计

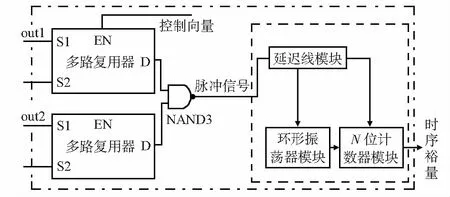

本文设计了混合模型的老化检测结构,结合合了环形振荡器结构和延迟线结构的优点,由多路复用器,延迟线模块,环形振荡器模块以及N位计数器模块组成,如图4所示。其面积开销比单纯的延迟线型检测器结构小。

图4 老化测量模块

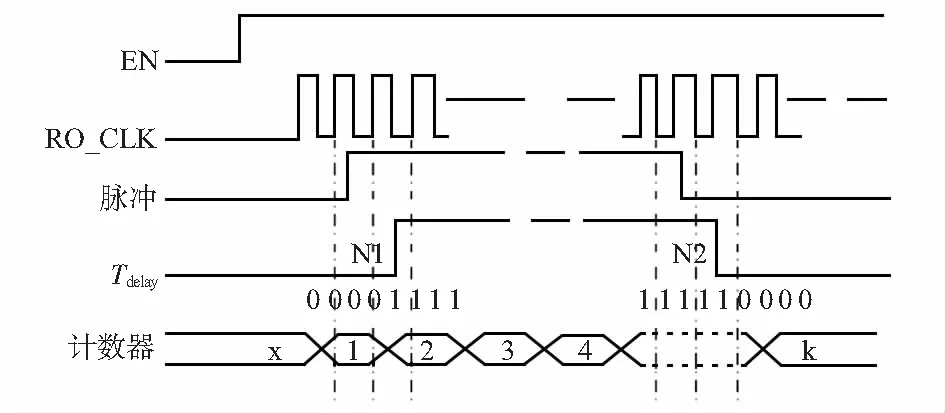

由于老化测量模块仅有一个。因此,要测量多条路径的具体延迟,两个多路复用器是必要的,其分别连接到每个老化探测模块的输出端Sig1,Sig2。多路复用器模块选择不同Sig1与Sig2的组合,通过老化延时测量模块的与非门NAND3,形成不同关键路径的脉冲信号。将形成的脉冲信号输入带延迟线模块以及环形振荡器模块,通过计数器模块的输出数据,测量出脉冲的实际宽度,也就是路径的时间裕量,从而反映出电路的实际老化状态。其波形图如图5所示。

图5 老化测量模块波形

当使能信号有效时,老化测量模块进入工作状态。脉冲信号通过老化测量模块以及延迟线模块,根据计数器输出经过的环形振荡器的周期数,来计算脉冲的宽度,计算公式如下

width=N1×Tdelay+k×TRO-N2×Tdelay

=k×TRO+(N1-N2)×Tdelay

(1)

式中k为脉冲信号到来环形振荡器经过的周期数,TRO为环形振荡器的周期,Tdelay为延迟线的周期,N1为延迟线模块在脉冲信号到达之后由低电平转换为高电平时环形振荡器的周期数,同样,N2为有高电平转换为低电平环形振荡器的周期数。

3.3 改进型环形振荡器结构

环形振荡器由奇数个非门组成,其震荡周期为T=2Ntdelay,其中N为非门的个数,tdelay为每个非门的传输延迟时间。改变电路中非门的数量即可以改变电路的振荡频率。

然而,传统的环形振荡器模块采用模拟的方法设计[10],或者采用数字的方法采用非门串联,在综合时,奇数个非门的级联可能会被综合成一个非门,偶数个非门的级联被综合成一个缓冲,很难保证完成相应的工作要求。因此,本文采用了一种改进型的环形振荡器结构,易于在EDA工具中综合,并且,相比于传统的方法,本文所采用的结构更加的灵活,其结构图如图6所示。

图6 改进型环形振荡器结构

为了保证正反馈的振荡,传统的非门级联必须是奇数个。而本文所采用的改进型环形振荡器只需要保证第一个与非门起到反相作用,而其他的与门起到延时缓冲的作用。可以通过改变门的数量Out输出端的震荡频率,不用受到必须为奇数个非门的限制,只需要第一个门得到正反馈就可以产生振荡。控制端En[n:0]为振荡使能信号,当其置高电平时,与非门的输入和输出在缓冲级联的反馈作用下产生自激振荡,环形振荡器正常工作。

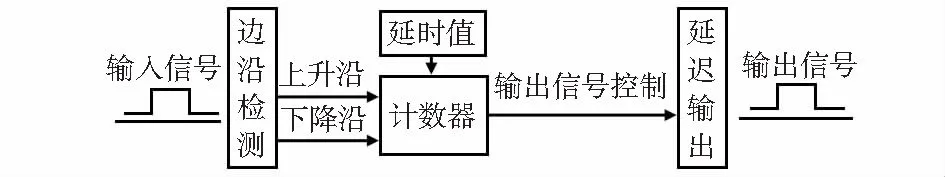

3.4 延迟线模块设计

延迟线模块的周期需大于环形振荡器的周期,当脉冲信号到来之前,延迟线模块由低电平变成高电平(或由高电平变为低电平),这时,可以通过环形振荡器的周期作为基准,计算脉冲的实际宽度。其结构图如图7所示。

图7 延迟线模块图

目标脉冲信号的上升沿到来时,计数器开始工作,当计数器的计数值等于之前预置的需要延时值时,延时信号置为高电平。此时计数器清零。当目标脉冲信号的下降沿到来时,同样地,在计数器的计数值等于延时值时,延时信号置为低电平。这样就完成了脉冲信号的延迟输出。

4 实验结果

4.1 有效性分析

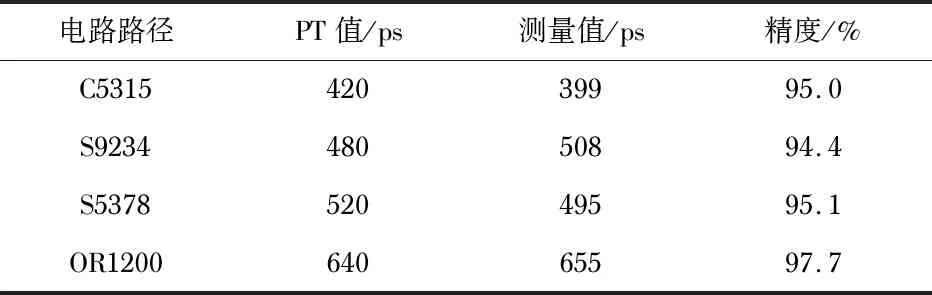

为了验证方法的有效性,在ISCAS基准电路及OR1200核上进行实验。通过PT(prime time)进行静态时序分析,静态时序分析能够准确地得到电路的实际的时间裕量,通过与测量值进行比较,可评估本方法的有效性。具体实验结果如表1所示。

表1 PT实际值及测量值

表1第一列为实验中在每个电路中所选取的关键路径,第二列是该路径通过PT测得该关键路径的时间裕量,第三列是通过本文所设计的模块得到的测量值。由表中数据可知,虽然测量值与实际的时间阈值存在细微的偏差,但总体精度均高于94 %。

4.2 面积开销

为了评估本文所设计模块的面积开销,使用Synopsys公司的Design Compiler综合工具及65 nm标准单元库上实验,结果如表2所示。第一列为所采用的测试电路,第二列为通过综合得到其的门数量,最后一列为检测模块在该测试模块所占的面积开销。

表2 检测模块面积开销

表3显示了本文所采用的混合结构与单环形RO模型和延迟线模型的对比情况。单环形RO模型具有很好的面积开销,但其有一个显著的不足就是精度比较低,测试所需时间较长。而延时线模型虽然具有较高的测试精度,但其是以牺牲面积开销为代价的。本文设计的混合模型很好地结合了两者的优点。

表3 几种老化检测模块的比较

5 结束语

本文设计了一种混合结构检测模块,包括集成到多个关键路径上的老化延时探测模块及一个共用的老化测量模块,用于监控功能路径上的信号转换,然后精确地测量实际的时间裕量(即路径延迟),并将其转换为数字值。该模块能够在片上实现对时间裕量的实时测量,为老化防护提供细粒度的信息。实验表明,其测量精度可达到94 %以上,满足了微处理器核老化延时的测量要求。