传输线中高速信号反射建模分析与优化

2021-03-01陈章进王文磊黄舒平

陈章进,王文磊,季 渊,3,黄舒平,3

(1.上海大学微电子研究与开发中心,上海 200072;2.上海大学计算中心,上海 200072;3.上海昀光微电子有限公司,上海 200072)

随着集成电路技术的发展,信号频率提升迅速,部分服务器设计中已经出现了25 Gbit/s的设计.在高速电路设计中,单向点对点传输线在印制板布线中占有很大比重.在传统的电路中如控制总线、地址总线均采用单向点对点传输线.在印制板的设计中,随意绘制的信号线虽然在理论上能够起到信号传输的作用,但在高速电路中寄生电容与电感将严重影响信号的传输质量,产生不必要的信号振荡与过冲.信号振荡与信号过冲广泛存在于各种低速、高速电路中.过冲与振荡不仅会削弱信号质量,造成信号能量的损失和误码,过高的过冲电压还会对输出端器件与接收端器件造成损害,严重的会造成器件的烧毁.

传统电路分析方法大多是逐个因素分析,Doi[1]对高速互连线的基本特性进行了比较详尽的分析研究.Ahn 等[2]对差分线的阻抗匹配等问题进行了比较详尽的研究.在工程上,文献[3-8]对高速电路中的过孔、传输线特性、信号振荡进行了比较系统的阐述.在实际工程应用中,传输线中信号振荡与过冲往往是多个因素作用的结果,因此振荡与过冲的解决除依靠工程师的经验,还需要进一步的建模和仿真分析.

本工作采用电路分布式模型与集总模型相结合的方式,对单向点对点传输线进行建模,分析构成传输线的过孔、线长对单向传输线信号振荡的影响,推导振荡与信号过冲的理论公式,并提出了解决信号振荡与过冲的方案.最后,通过仿真验证了方案的正确性,目前本设计方案已经成功应用于多个产品的设计中.

1 电路模型构建与分析

1.1 信号反射原理

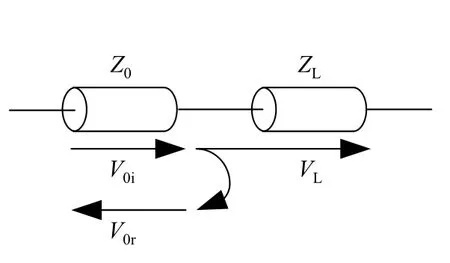

信号反射是信号在传输线上的回波,是影响信号传输质量的一个最基本也是最主要的原因.多次的信号反射叠加形成信号振荡[9].本工作通过分析信号反射原理,对传输信号电路建立集总参数模型(见图1).

图1 传输线信号反射示意图Fig.1 Transmission line signal reflection diagram

在传输信号电路中增加一个负载电阻ZL,输入电压为V0i,传输电压为VL,反射电压为.此时

从反射系数方程可以看到,当Z0=ZL时,反射系数Γ=0,此时信号无反射,这种情况是最理想的阻抗匹配状态.阻抗的反射会与新输入的信号发生叠加,产生信号过冲,多次反射会形成信号振荡.

理论上解决传输线信号反射的问题除了控制线宽、优化过孔设计与数量外,最为常见也是最有效的方法是采用合理的阻抗匹配方案.阻抗匹配方案主要有4 种:串联阻抗匹配方案、并联阻抗匹配方案、戴维南阻抗匹配方案、RC 串联阻抗匹配方案[11].在通常情况下,阻抗匹配方案采用串联阻抗匹配或并联阻抗匹配方案.串联阻抗匹配方案直接便捷,但电路中的串联电阻会造成信号电压的分压,衰减的信号电平可能造成信号数据丢失.而并联阻抗匹配方案的优势是并联阻抗匹配端接电压(termination voltage,VTT)的存在使得信号有着更好的信号边沿特性,当采用特定端接电压时,信号具有更好的上升沿与下降沿.但端接电压的存在会改变信号的占空比,可能会导致数据的丢失.

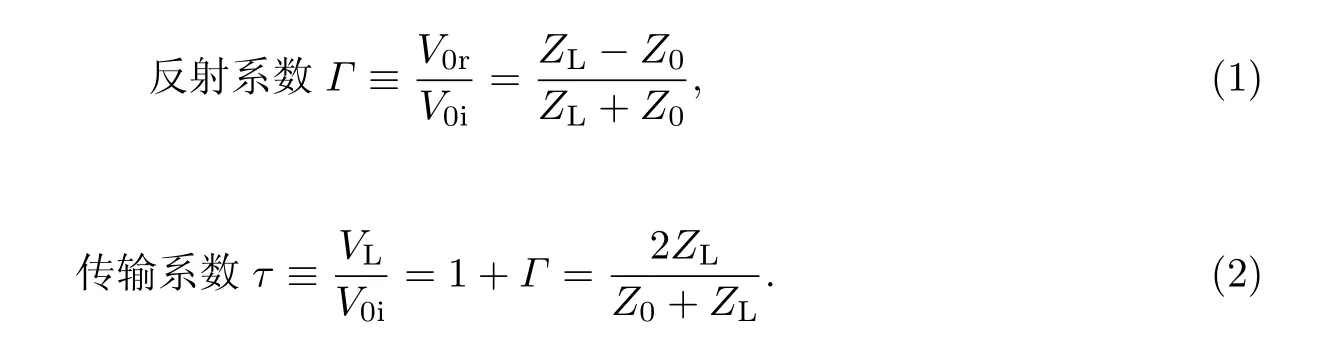

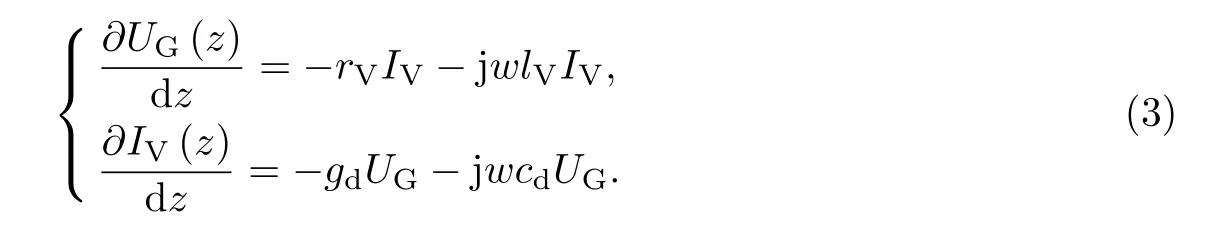

1.2 传输线分布式模型

在印制线路板(printed circuit board,PCB)中,任何传输线都或多或少会存在一定程度的信号反射问题.本工作在传统集总电路模型基础上,结合电路的分布式模型进行分析(见图2).

图2 传输线分布式模型Fig.2 Transmission line distributed model

在图2 中,rV和lV是电路的分布电容与分布电感,gd和cd是对参考面的等效电容与等效电抗.根据基尔霍夫电路定律,建立如下微分方程求解图2 中UG与IV,

根据Z0=UG/IV,可以求得传输线特征阻抗

在高频情况下,传输线的分布感抗远远大于分布电阻,分布容抗远远大于分布电导,即,此时可以对Z0进行化简,

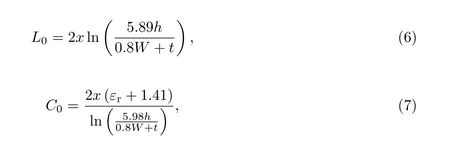

根据文献[3,10]对rV,lV分布电容(nH)与分布电感(pF)进行积分,得到传输线的等效电感L0和等效电容C0,

式中:x为传输线长度;h 为传输线与基准面的高度;W为传输线线宽;t 为铜箔厚度;εr为印制板介电常数.此时传输线造成信号的上升延迟

从式(8)可以看到,传输线特征阻抗与传输线的长度无关,与印制板的材料、叠层设计有关.此时传输线的过冲电压为

在一定频率下,为了防止信号反射回波影响后续信号输入,同时保证不发生信号反射,求取最大传输线长度为Lmax.根据文献[12]以及工程经验,传输线最大信号传输频率fmax与信号的传输延时tpd存在经验公式:

此时最大传输线长度

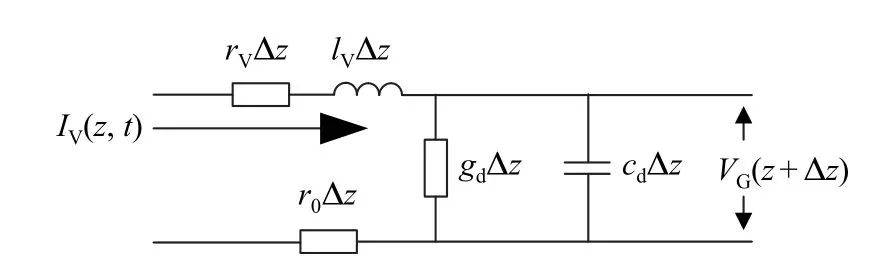

1.3 传输线中过孔建模

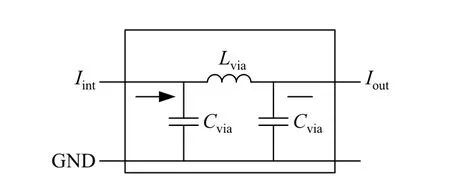

过孔是电路设计中不可缺少的一部分,过孔的主要功能是实现信号的换层.在高密度互连(high density interconnector,HDI)设计过程中,信号扇出需要大量的过孔,过孔的存在对信号传输质量有一定影响.对过孔的分析需要建立电路等效集总模型,根据文献[13]建立如图3所示的过孔模型(图中GND 代表地线).

图3 过孔等效模型Fig.3 Via equivalent model

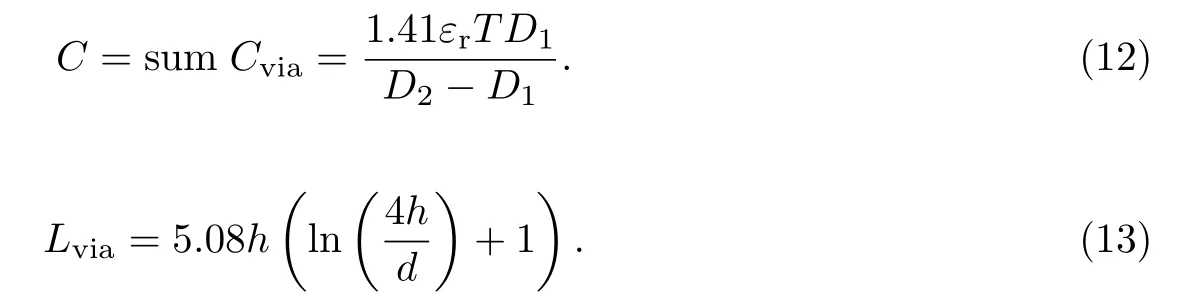

过孔等效电容与等效电感的大小与印制板的设计密切相关.通过计算分析得到过孔的等效电容和等效电感为C 和Lvia.过孔焊盘的直径为D1,过孔在铺地层上的隔离孔直径为D2,基材介电常数为εr,PCB 板层厚度为T,d 为中心钻孔的直径,h 为过孔长度.

根据式(10),过孔对传输信号最大的影响是电容与电感造成的信号延迟,从而导致信号边沿劣化.为降低信号反射的风险,过孔传输延时需要满足

2 设计仿真验证

2.1 硬件系统平台搭建

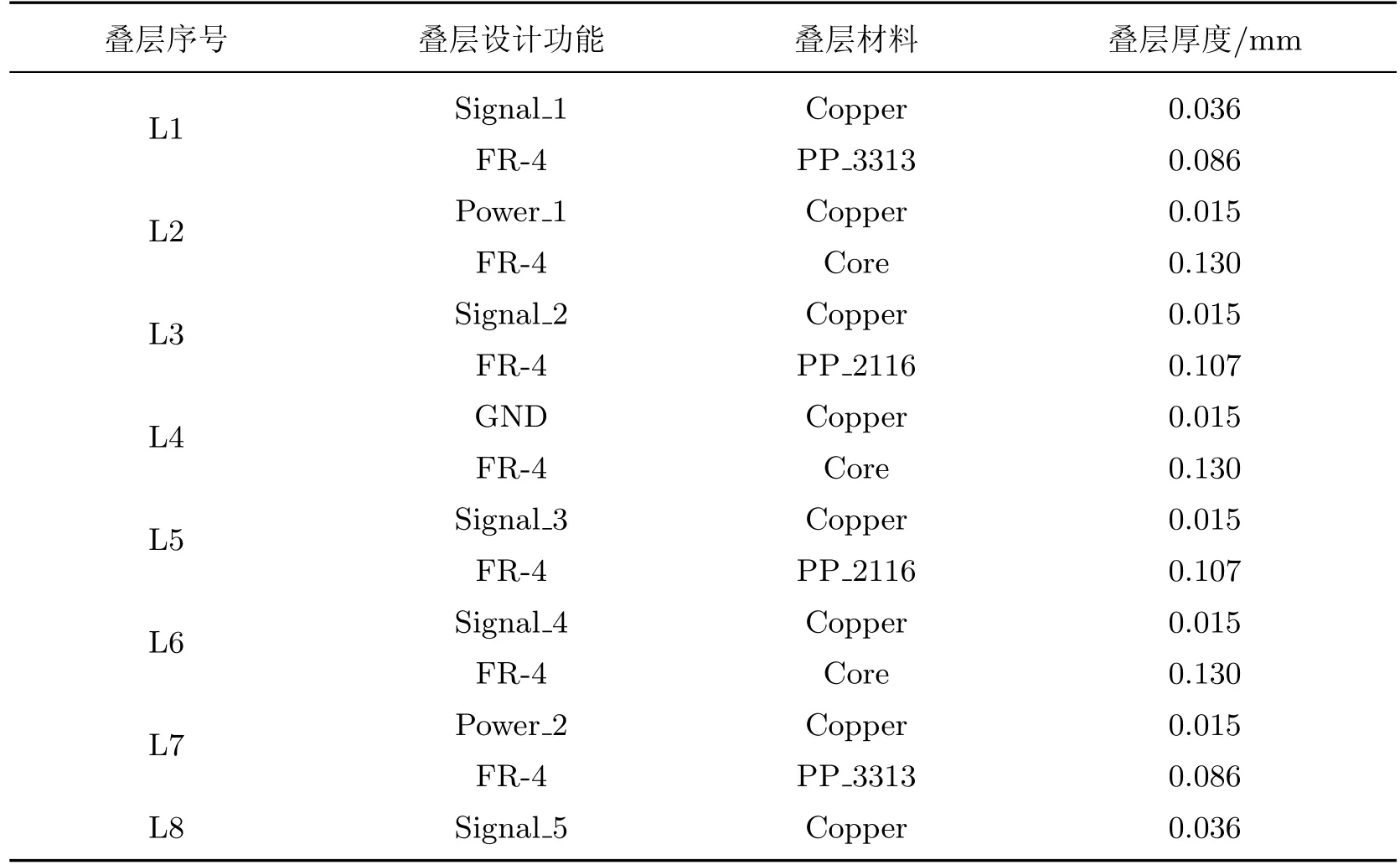

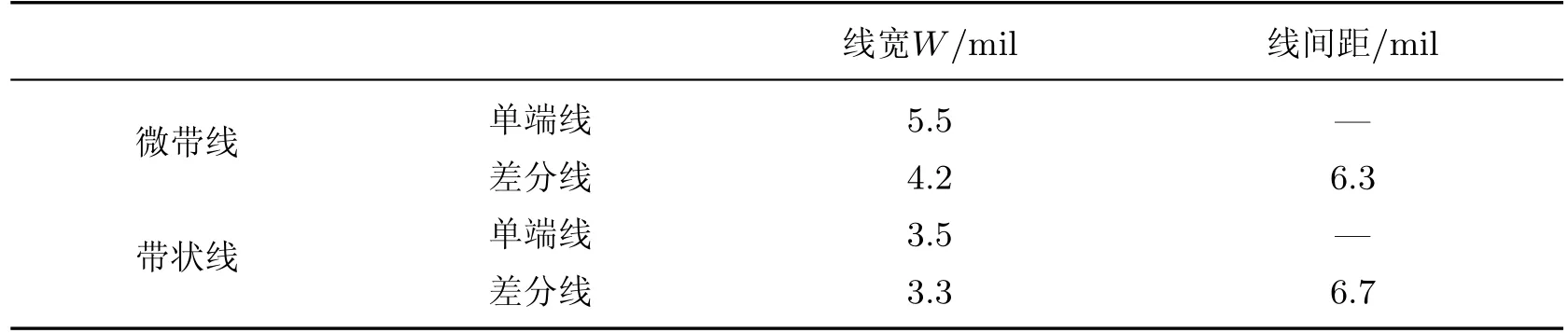

为解决某款高速现场可编程门阵列(field programmable gate array,FPGA)存储系统设计中所遇到的信号反射问题,为工程设计提供一套可复用的规范化设计流程,本工作采用具有代表性的硬件产品.系统包含两个DDR2,传输线类型为SSTL18[14],主控芯片采用Xilinx 的SPARTAN-6 系列.印制板设计采用了普通的FR-4 材料作为基材,介电常数εr为4.6,铜箔传输线损耗角为0.02[15].叠层设计采用了8 层电路板,印制板厚度为1.0 mm,具体配置如表1所示.差分线按厂家参考设计(见表2,表中1 mil=0.025 mm),传输线采用的是单端信号50 Ω阻抗匹配、差分100 Ω 阻抗匹配的方案.

表1 PCB 叠层设计参数Table 1 Design parameters of PCB stack

表2 PCB 厂家建议设计参数Table 2 Design parameters of PCB manufacturer’s suggested

在800 MHz 频率下,通过式(5)∼(7)计算得到,微带线传输线特征阻抗Z0为48.8 Ω,等效电感L 为7.307 2 nH/inch(1 inch=0.025 4 m),等效电容C 为3.065 6 pF/inch,传输延时tpd为149.670 7 ps/inch.根据式(11),传输线临界长度Lmax为2 936 mil.此时输入1.8 V 的冲激信号,接口内阻RS为50 Ω.根据式(8)和(9),谐振系数Q 为0.976,产生的输入端过冲电压Vovershoot为0.277 V,信号增益为1.24 dB,不会对信号产生很强干扰.

考虑到目前国内制造工艺的限制,过孔内径d 为8 mil,外径D1为10 mil,PCB 总厚度h 为1.0 mm,反焊盘尺寸D2为16 mil.利用式(12)和(13),过孔电容C 为0.425 6 pF,过孔电感Lvia为0.796 0 nH,过孔等效阻抗为43.247 Ω,谐振频率为8 647.203 MHz,单个过孔对传输信号产生的信号延时tpd为20.245 9 ps.经过上述计算获得,传输线长度不超过2 936 mil,过孔谐振频率f 远远高于设计目标频率Ftarget,单个过孔不会产生信号谐振影响传输线信号质量.通过式(14)计算,在保证信号质量的前提下,最大过孔数量为4 个.

2.2 设计仿真验证

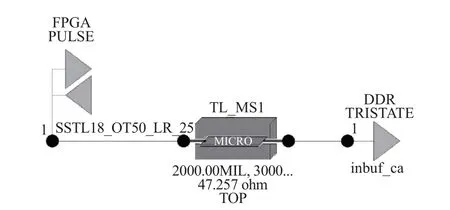

为了验证理论推导的正确性及优化对设计方案的有效性,本工作采用Cadence Sigrity 软件进行电路拓扑结构的提取与仿真,仿真模型采用Spartan-6 与Micrion DDR2 的IBIS 模型,Sparta-6 芯片接口类型为SSTL18-OT50-LR25,此时接口内阻为50 Ω,管脚位置在芯片的左侧,FPGA 芯片的辅助电压为2.5 V.仿真传输线为内存地址线,采用地址线进行仿真所获得的解决方案具有很高的可复用性.

2.2.1 传输线线长对信号的影响

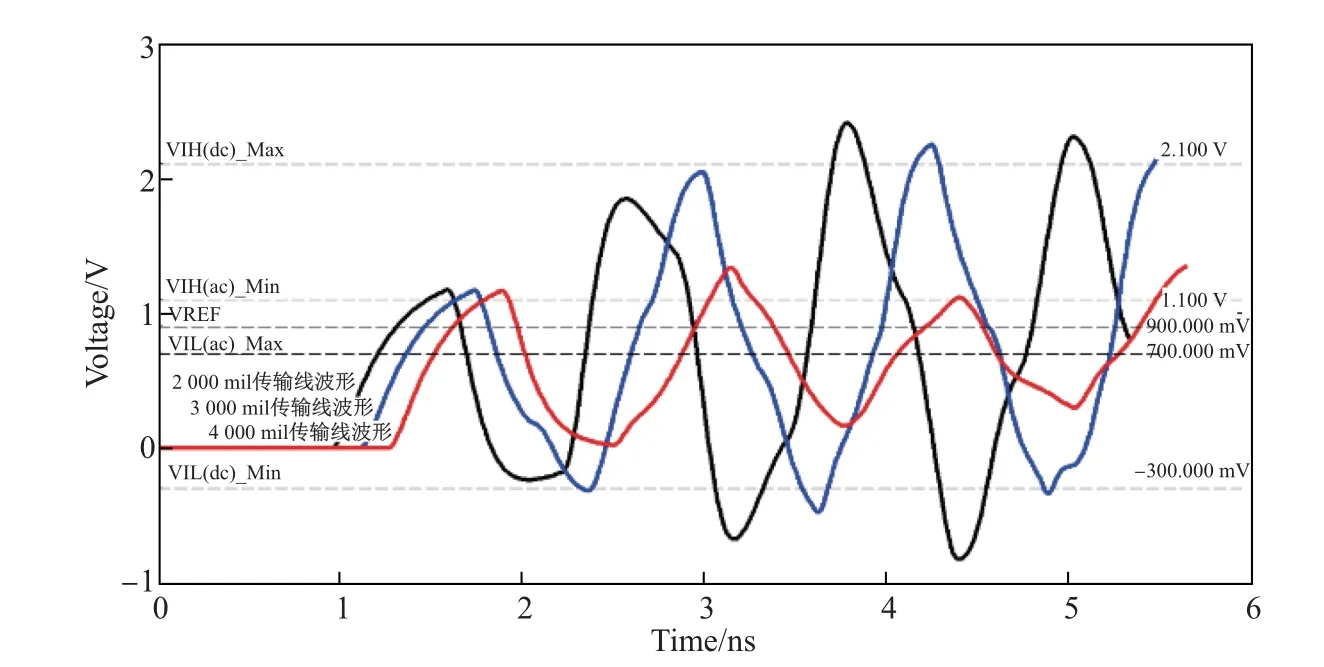

通过式(6)和(7)的分析,传输线的长度会影响传输线的电容与电感.在不考虑信号串扰和电磁干扰/电磁兼容性(electromagnetic interference/electromagnetic compatibility,EMI/EMC)的情况下,增加的传输线电感与传输线电容会导致信号线产生信号振荡.传输线仿真参数参照表1,仿真叠层为顶层,传输线中不添加过孔.通过计算可知,传输线的临界长度为2 936 mil,因此仿真线长分别为2 000,3 000,4 000 mil(见图4).

图4 2 000,3 000,4 000 mil 仿真拓扑结构Fig.4 2 000,3 000,4 000 mil simulation topology structure

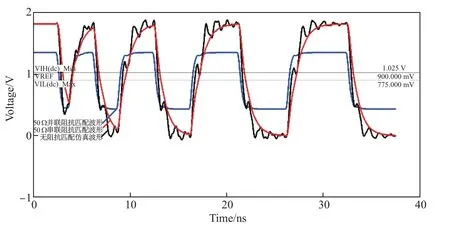

Cadence 计算阻抗为47.825 7 Ω,获得仿真波形如图5 和6 所示.图5 和6 中VIH(high input voltage)代表最高输入门限电压,VIL(low input voltage)代表最低输入门限电压,VREF(voltage reference)代表输入基准电压.由图5 可见,在没有其他空间干扰的情况下,4 000 mil 传输线已经不能保证信号电平达到信号的门限电压,而在2 000 与3 000 mil 的传输线波形中,信号的过冲已经达到了信号的最大门限电压.

图5 传输线长度与信号反射仿真波形(脉冲序列)Fig.5 Transmission line length and signal reflection simulation waveform (pulse sequence)

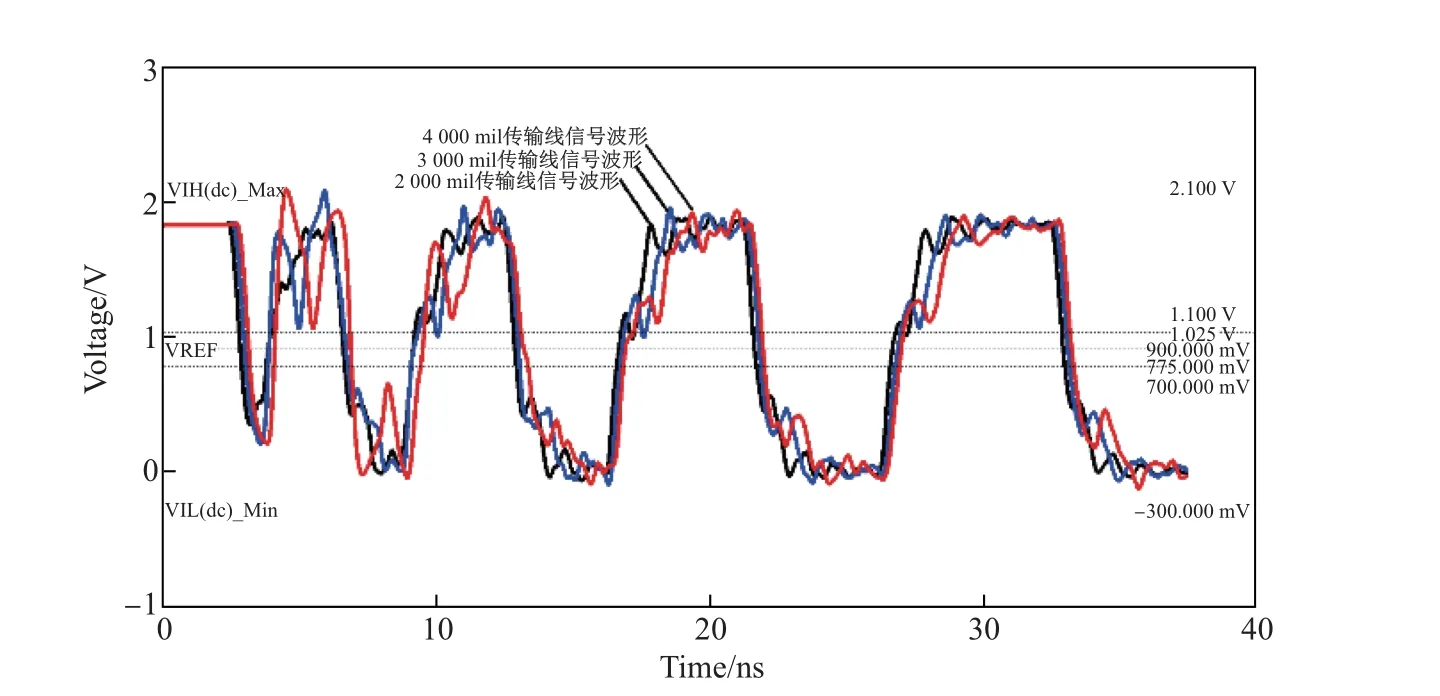

由图6 (仿真序列101100111000111100001111100000) 可见,进行脉冲序列仿真时,3 000 mil 传输线信号过冲已经达到门限电压最大值,信号下冲也刚好达到了VIH(ac)高电平的下限值,存在较大的信号误码风险,同时也证明了理论计算Lmax的正确性.但在800 MHz 频率下,虽然更短的传输线可以提供较好的信号电平,但2 000,3 000,4 000 mil 传输线均出现了比较严重的信号过冲与信号振荡,在这种情况下,采用合理的阻抗匹配方式对保持信号质量有着重要意义.

图6 传输线长度与信号反射仿真波形(仿真序列)Fig.6 Transmission line length and signal reflection simulation waveform (simulation sequence)

2.2.2 阻抗匹配方案设计

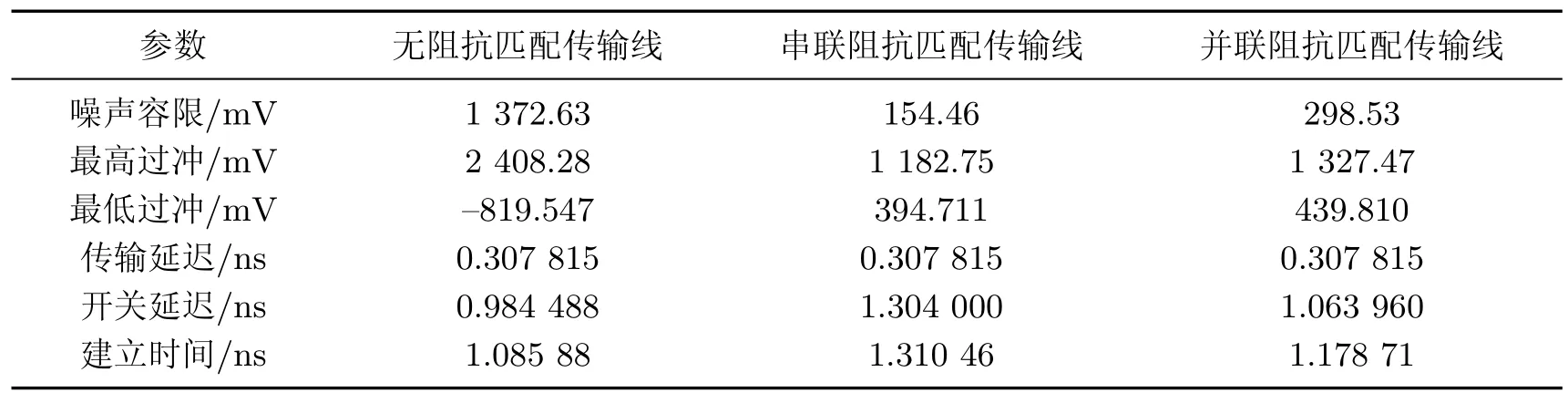

解决信号振荡与过冲的方法主要有各类传输线的阻抗匹配方案,在仿真情况下,采用的阻抗匹配电阻均是50 Ω.如图7 所示,在800 MHz 频率下,串联阻抗匹配与并联阻抗匹配对传输信号质量均有改善.根据2.1 节的分析,串联阻抗匹配在削弱信号过冲的同时也削弱了信号强度.根据表3,并联阻抗匹配相对串联阻抗匹配在信号的建立时间与噪声容限方面均有较大的改善,各项性能均优于串联阻抗匹配,因此高速单向点对点的传输线阻抗匹配最优方案是采用50 Ω 并联阻抗匹配方案.

表3 串、并联阻抗匹配与无阻抗匹配仿真参数Table 3 Series,parallel impedance matching and impedance matching simulation parameters

图7 串、并联阻抗匹配与无阻抗匹配仿真波形Fig.7 Simulation waveform of series,parallel impedance matching and impedance matching

2.3 并联阻抗布局设计

并联阻抗匹配设计涉及端接电压值的设计,端接电压能够解决过长传输线导致的信号压降问题,同时也能够优化信号边沿.但端接电压的存在可能会导致信号占空比发生改变,影响信号质量.为获得具有可复用性的方案,本工作通过仿真验证并联阻抗匹配方案中的端接电压对信号质量改善的效果.

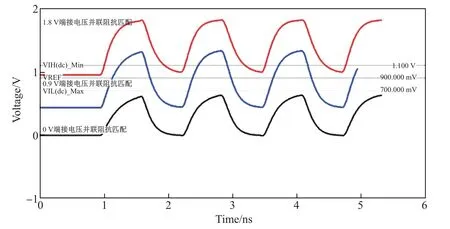

由图8 可见,不同的端接电压值会影响信号传输质量,导致信号的传输电平异常,影响信号的边沿特性和占空比.在设计并联阻抗匹配时,端接电压值根据信号频率与信号幅度综合仿真确定,本方案中最佳端接电压为0.9 V.

图8 端接电压与信号传输质量仿真波形Fig.8 Simulation waveforms of terminal voltage and signal transmission quality

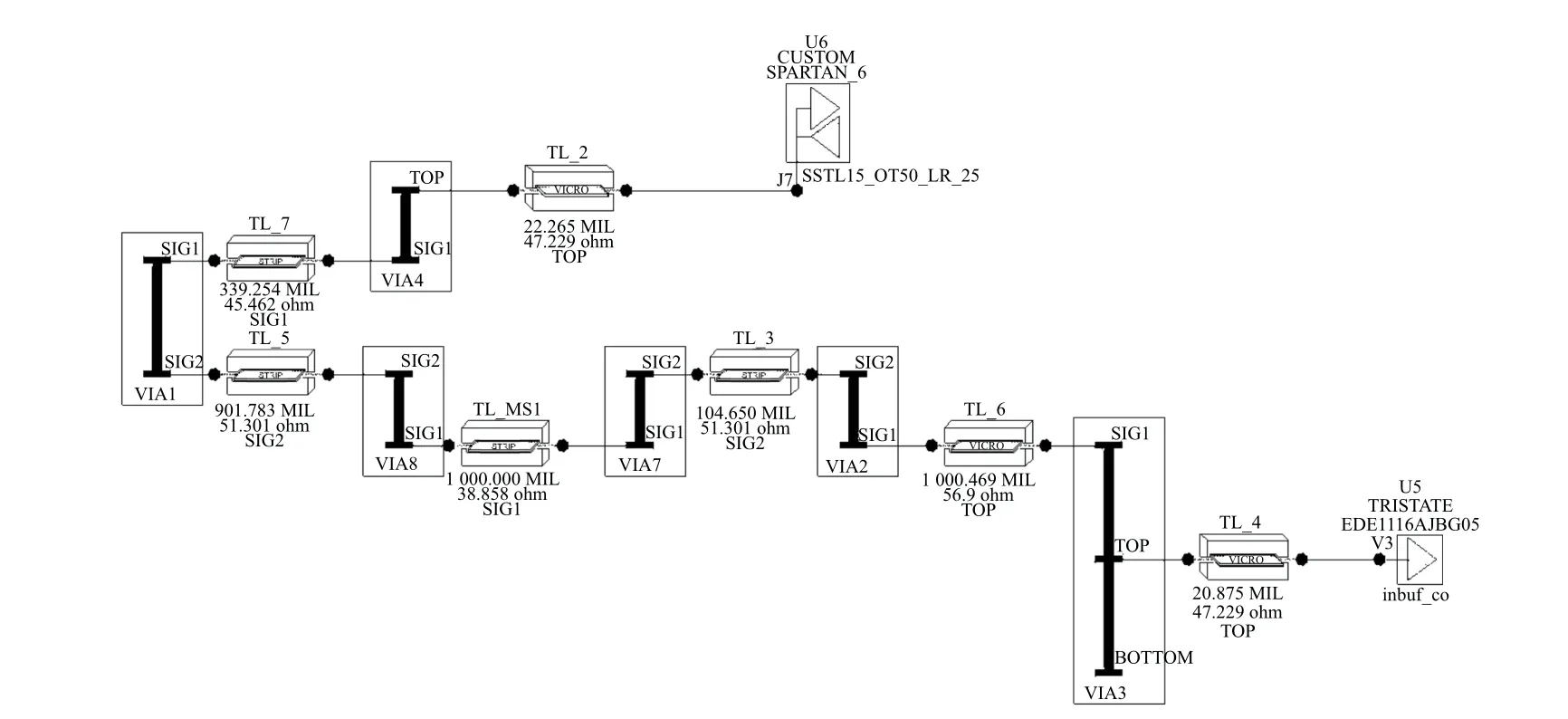

2.4 现实方案设计优化

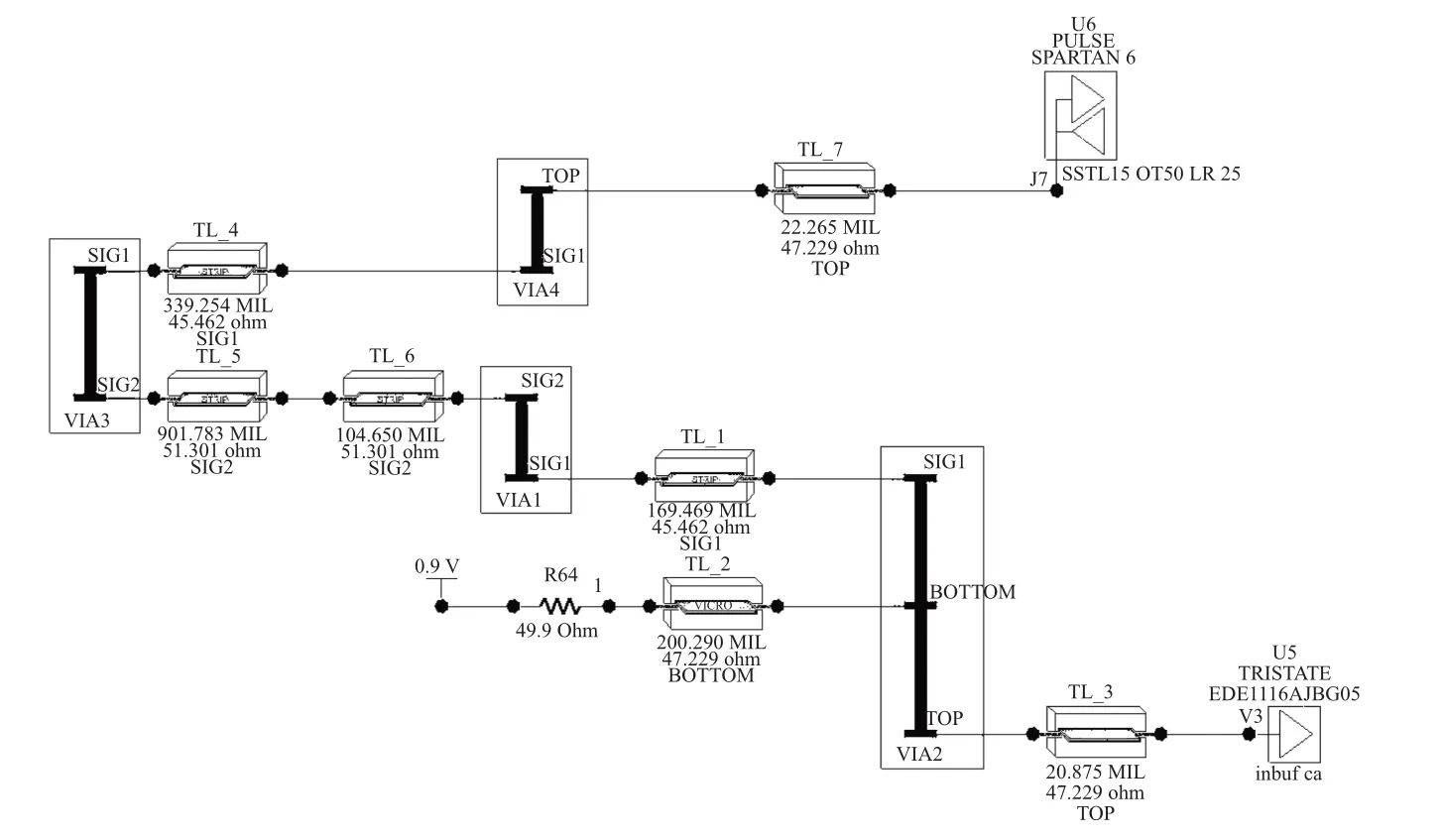

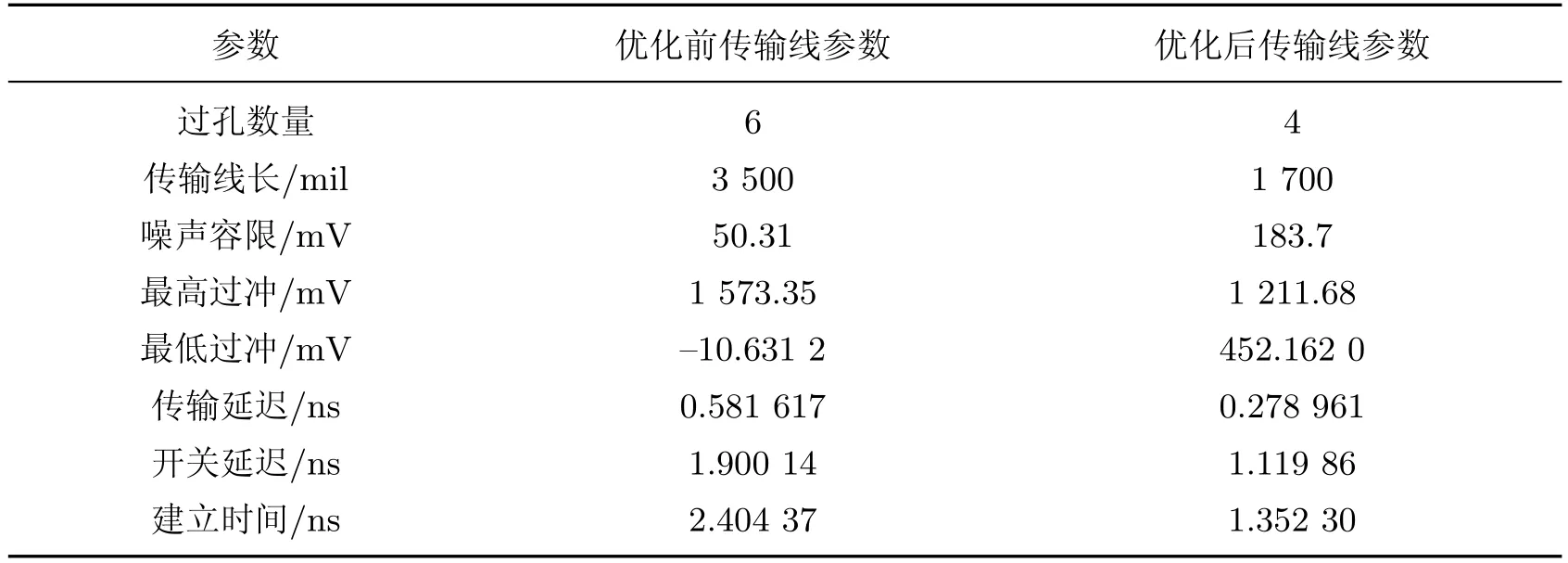

通过理论分析和建模仿真,本工作在高速单向点对点传输线设计中,采用0.9 V,50 Ω 末端阻抗方案.对设计方案进行优化后,过孔的数量减少为4 个,传输线长度缩短到1 750 mil,端接电压采用0.9 V VTT 基准电压,匹配电阻为50 Ω,采用的是末端并联电阻匹配方案.信号输入接口标准采用SSTL18.优化设计前后,利用Cadence Sigrity 对电路板进行拓扑提取对比设计优化差异,如图9 和10 所示.

图9 优化前传输线拓扑结构Fig.9 Transmission line topology before optimization

图10 优化后传输线拓扑结构Fig.10 Transmission line topology after optimization

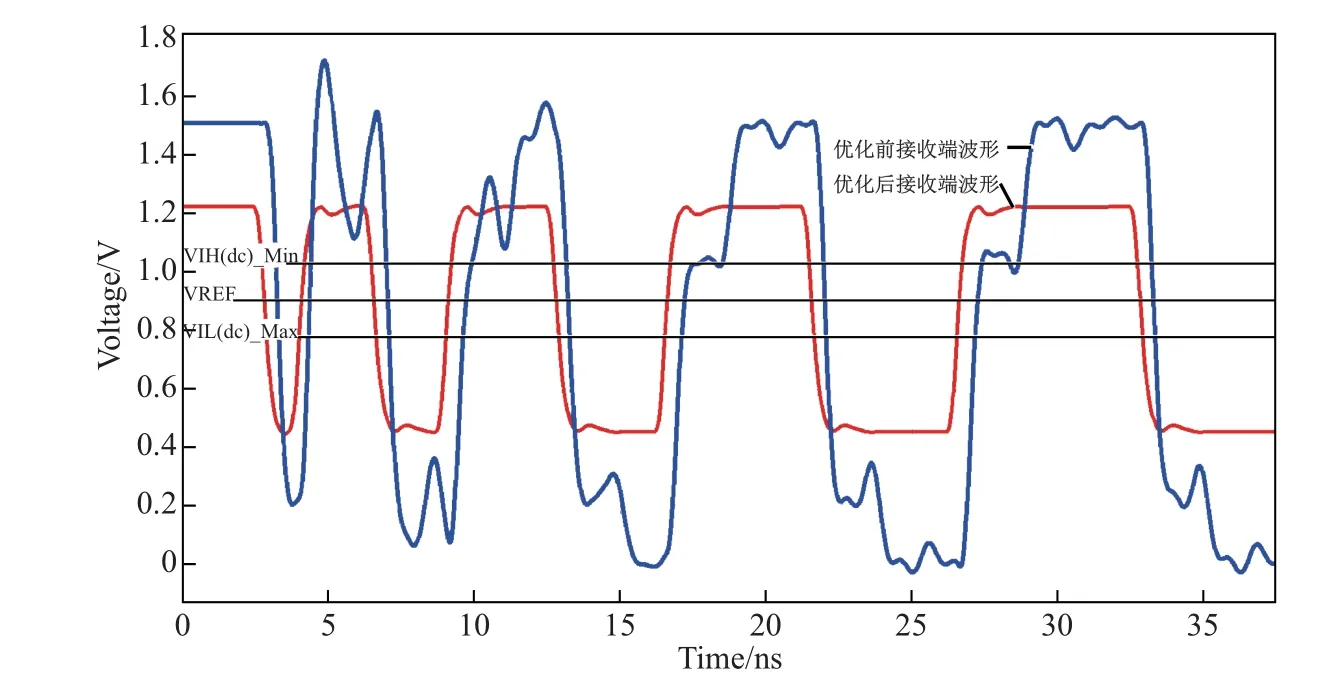

由图11 和表4 看可见,在800 MHz 频率下,相较于优化前的传输线波形,传输线信号质量有明显的改善,信号振荡明显改善.优化后信号最高过冲电压为1.2 V,最低过冲电压约为0.45 V,波形信号没有出现明显的振荡与过冲.优化后,信号传输稳定,信号边缘明显,从信号的上升时间、信号幅值、传输延迟等参数上看,优化效果非常明显,均满足DDR2 的设计标准[16].

图11 传输线优化前后信号波形Fig.11 Signal waveforms of transmission line before and after optimization

表4 布局布线优化前后仿真参数对照Table 4 Simulation parameter comparison before and after layout and routing optimization

3 结束语

本工作针对实际应用中出现的信号反射和信号过冲现象,对原有单向传输线模型进行了总结与推导.通过理论推导计算最优值,对原有设计进行了优化,同时通过仿真验证了高速单向点对点传输线设计中的匹配电阻值、长度、过孔数量以及布局布线中器件放置位置等设计要点,提出了一套具有复用价值的方案.本设计方案能够有效简化原有设计方案,提升设计性能,节约设计开支,在工业领域有着重要的应用价值.本工作所研究的高速点对点单向传输线理论与设计优化方案已应用于某型高速FPGA 控制器产品中.