一种用于遥感卫星中稳像相机设计和实现①

2021-02-23侯作勋

刘 明,侯作勋,李 馨

(北京空间机电研究所,北京 100094)

0 引言

随着成像传感器分辨率的提高以及卫星平台复杂性和敏捷性的增强,平台抖动对空间遥感相机影像成像质量、几何处理等方面的影响愈发显著[1]。当空间遥感相机工作时,由于高帧频CCD 相机的积分时间非常短,近似于冻结了图像的低频运动,对于高频分量少的扰动,仍然可以采集到清晰的图像。当高频分量扰动较大时,会影响空间遥感相机的成像质量。 空间遥感相机凝视的积分时间较长,为了在较长的积分时间内能够稳定成像,需要设计稳像控制系统,解决成像积分时间内由于卫星平台的残余抖动引起的图像模糊问题[2-3]。

针对上述问题,Janschek 等提出了一种采用辅助的面阵图像传感器和光学相关器来完成实时光轴偏移测量,利用光学反馈的闭环控制系统完成实时的光轴测量,利用光学反馈的闭环控制系统在光路上通过主动光机补偿焦平面上的运动图像的稳定成像方法[4]。 徐之海等提出采用高帧频CCD 相机获取光轴偏移量,再采用微位移平台驱动焦平面跟踪光轴的偏移来对光轴的偏移进行有效的补偿[5]。

稳像相机是获取信息实现闭环控制的输入和核心,是稳像系统的重要组成部分[6]。 本文设计的稳像相机和遥感相机使用同一光路,稳像相机获取光轴上的图像,稳像控制器计算光轴偏移量,再根据偏移量调节摆镜,使光轴始终位于遥感相机的焦平面中心。 为了获得较高的稳像控制带宽,要求稳像相机必须具备千赫兹量级的成像帧频,这就要求相机具备高灵敏度、低噪声的特点,并可以在极短曝光条件下获取图像信息;同时相机需要具备大面阵成像能力,以期拍摄获得足够大的地物场景,为寻找细节丰富的区域开展帧间关联提供可能[7-9]。 综合而言,相机需要具有大面阵、高动态范围、低噪声成像和动态高帧频开窗成像的能力。 此外,由于稳像相机通常和遥感相机共用一个光路,可利用面积较小,需具备轻小型的特征,这些都是稳像相机需要攻关的技术难题[10]。

1 稳像相机电子学设计

1.1 稳像相机架构设计

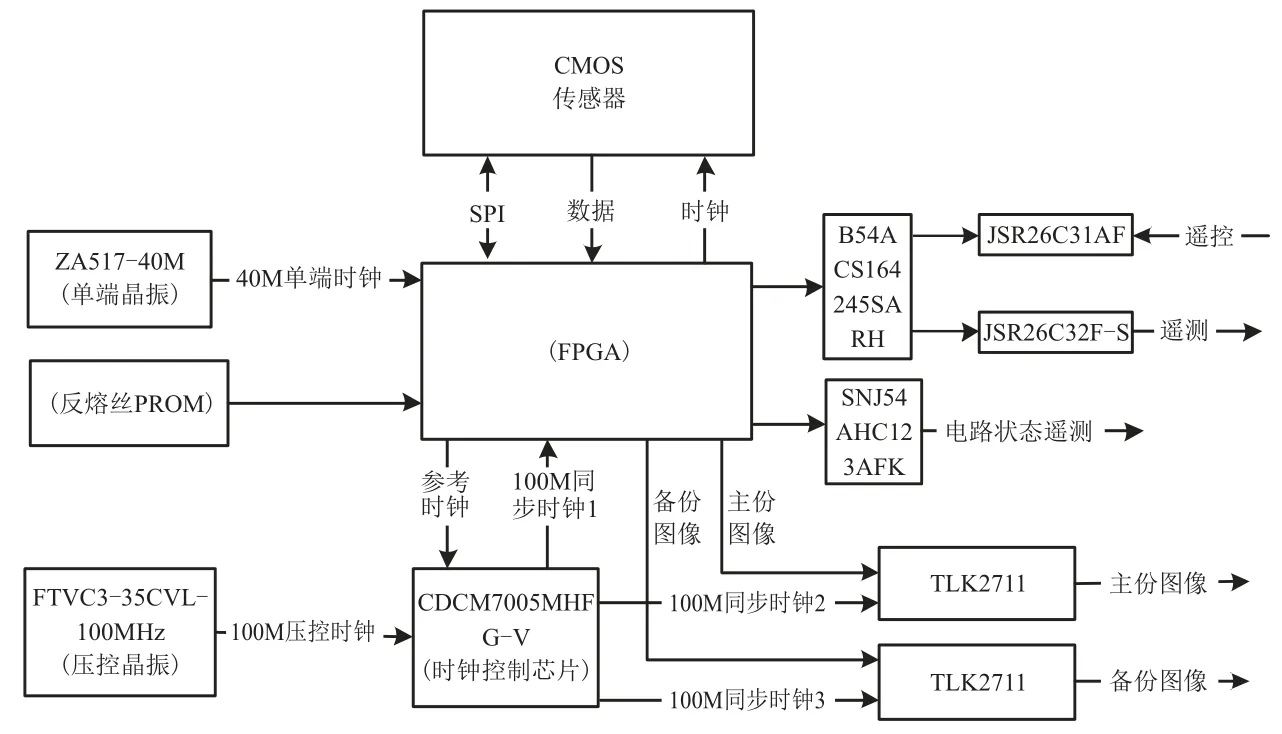

本文所设计的稳像相机采用宇航级元器件设计方案,核心元器件有CMOS 传感器、FPGA、驱动高精度时钟控制芯片(CDCM7005)和SERDES 高速传输芯片(TLK2711),电路架构如图1 所示。

图1 稳像相机电路原理框图Fig.1 Schematic diagram of image stabilization camera circuit

FPGA 驱动CMOS 图像传感器成像,CMOS 图像传感器的图像数据经过FPGA 预处理后直接发送至TLK2711 芯片实现并串转换功能;反熔丝PROM 芯片实现FPGA 的配置功能;B54ACS164245SARH 芯片实现 LVTTL 电平和 LVCMOS 电平件的转化,JSR26C31AF 芯片实现遥控数据的接收、JSR26C32F-S 芯片实现遥测的发送;ZA517-40M 晶振是FPGA 的启动时钟,当FPGA 启动后驱动时钟同步芯片(CDCM7005MHFG-V)实现两个TLK2711接口芯片和FPGA 时钟严格同步。

1.2 高速SerDes 电路设计

FPGA 驱动CMOS 图像传感器,传感器输出12通道并行数据,FPGA 将数据进行排序后将高四位填充0,按照16 bit 并行输入到 SerDes 型 TLK2711芯片。 以SerDes 为物理层协议充分利用8b/10b 编解码功能来提高可靠性,采用简单的用户接口,为实现与不同上层协议的接口提供了良好的兼容性[11]。

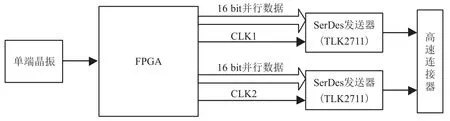

由于SerDes 接口电路采用16 bit 数据高速并行传输,设计电路时需要重点考虑时钟的完整性。 传统的设计方案如图2 所示,FPGA 的时钟由外部晶振提供,再由FPGA 的时钟控制单元DCM 产生时钟输出至SerDes 芯片。 时钟管理单元产生的全局时钟 jitter 为 150 ps,全局时钟 skew 为 110 ps。 SerDes型 TLK2711 芯片要求钟 jitter 小于 40 ps。 因此,传统设计方案不能满足设计要求。

图2 原始SerDes 接口电路设计方案Fig.2 Original SerDes interface circuit design

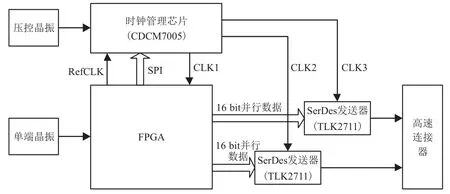

本文提出一种新的设计方案,新方案采用CDCM7005 芯片实现FPGA 时钟与TLK2711 时钟的抖动清除和同步控制。 CDCM7005 是德州仪器公司推出的一款具有低噪声性能的时钟同步与抖动清除器,外部控制器可以通过其逻辑接口对其实现编程控制,该器件可以实现2.2 GHz 压控晶体振荡器频率与基准时钟中同步,具有较大的应用灵活性[12]。改进后的设计方案如图3 所示,电路上电时,FPGA首先接收外部晶振的时钟进行初始化,FPGA 启动后通过 SPI 总线驱动 CDCM7005;CDCM7005 以外部压控时钟为基准时钟,以FPGA 输出时钟为参考时钟,产生3 个同步时钟,供2 路 TLK2711 和1 路FPGA 使用,达到3 个时钟完全同步且抖动较小。

图3 改进后SerDes 接口电路设计方案Fig.3 Design scheme of improved SerDes interface circuit

1.3 高速宇航级PCB 布局设计

稳像相机焦平面和遥感相机焦平面共用成像光路,因此稳像相机可用电路面积较小。 为了满足稳像相机的可靠性设计要求,需要整机除传感器外都采用面积较大宇航级元器件。 传统的CMOS 相机通常使用板间连接器连接各电路板,该方法占用面积较大,不能满足目前的实际情况。 本方案中通过优化PCB 布局设计,将大面积的宇航级元器件合理的摆放在焦平面电路、信号处理电路和接口电路上,并将3 种电路集成在一块刚挠板上,最大限度节省电路面积。

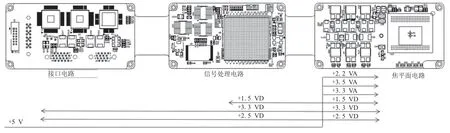

稳像相机需要+2.2 VA、+3.5 VA、+3.3 VA、+1.5 VD、+3.3 VD 和+2.5 VD 等 6 路二次电,焦平面电路板上图像传感器对电压精度要求较高,在焦面电路上采用6 路LDO 实现电源供电,在PCB 布局过程中,LDO 就近放置于传感器供电引脚,LDO芯片转化电压后就近给图像传感器供电;信号处理电路板需要+1.5 VD、+3.3 VD 和+2.5 VD,接口电路板需要+3.3 VD 和+2.5 VD,焦平面电路电路板转化后的电源输送至信号处理电路和接口电路。 进行PCB 设计时需要对电源层进行详细划分,尽量将供电相同的芯片放在一个供电条带上,电源层上下需要设置地层,减少电源层对高速信号的干扰,稳像相机PCB 的布局和电源走向如图4 所示。

图4 高速宇航级PCB 布局图Fig.4 Layout of high speed Aerospace PCB

1.4 稳像相机软件设计

稳像相机工作时首先进入全画幅成像模式,搜索到特定目标后,进入闭环控制成像模式。 稳像相机接收全画幅的成像指令后,FPGA 配置CMOS 图像传感器分辨率为1 280×1 024,并根据遥控指令要求配置图像传感器曝光时间、增益以及是否打开片上FPN 校正。 FPGA 能够根据遥控指令设置的帧频定时生成曝光触发信号,驱动CMOS 图像传感器根据设定的曝光时间完成全局曝光,并按照传感器预设的视频输出时序对视频进行接收和采集[13-14]。

稳像相机闭环控制成像模式与全画幅工作模式基本相同,但在稳像相机闭环控制模式下,FPGA 需要根据遥控指令的调整开窗位置。 由于传感器以SLOT 为基本单元读取数据,一个SLOT 读取24 个像元,在开窗采集时,一行32 个像元可能需要2 或3 个SLOT 完成读取,具体数量同开窗位置有关。FPGA 应根据遥控指令设置的开窗起始位置,计算读取一行数据涉及的SLOT 数量并及时调整CMOS传感器的配置参数。

FPGA 对于从CMOS 图像传感器采集到的原始视频流进行预处理,要求剔除掉帧开始、行开始、帧结束、行结束、灰/黑校正列数据、校验数据、列不一致定校正以及同步训练数据,仅保留有效视频图像数据。 将有效视频图像数据按照行列递增逐点扫描方式进行重排,对重排后的数据存入 FPGA 上SRAM 构建的 FIFO 进行缓存。 当 FPGA 接收到待机指令后,不再驱动CMOS 图像传感器,此时将不输出视频图像。

2 测试与试验

2.1 帧频测试

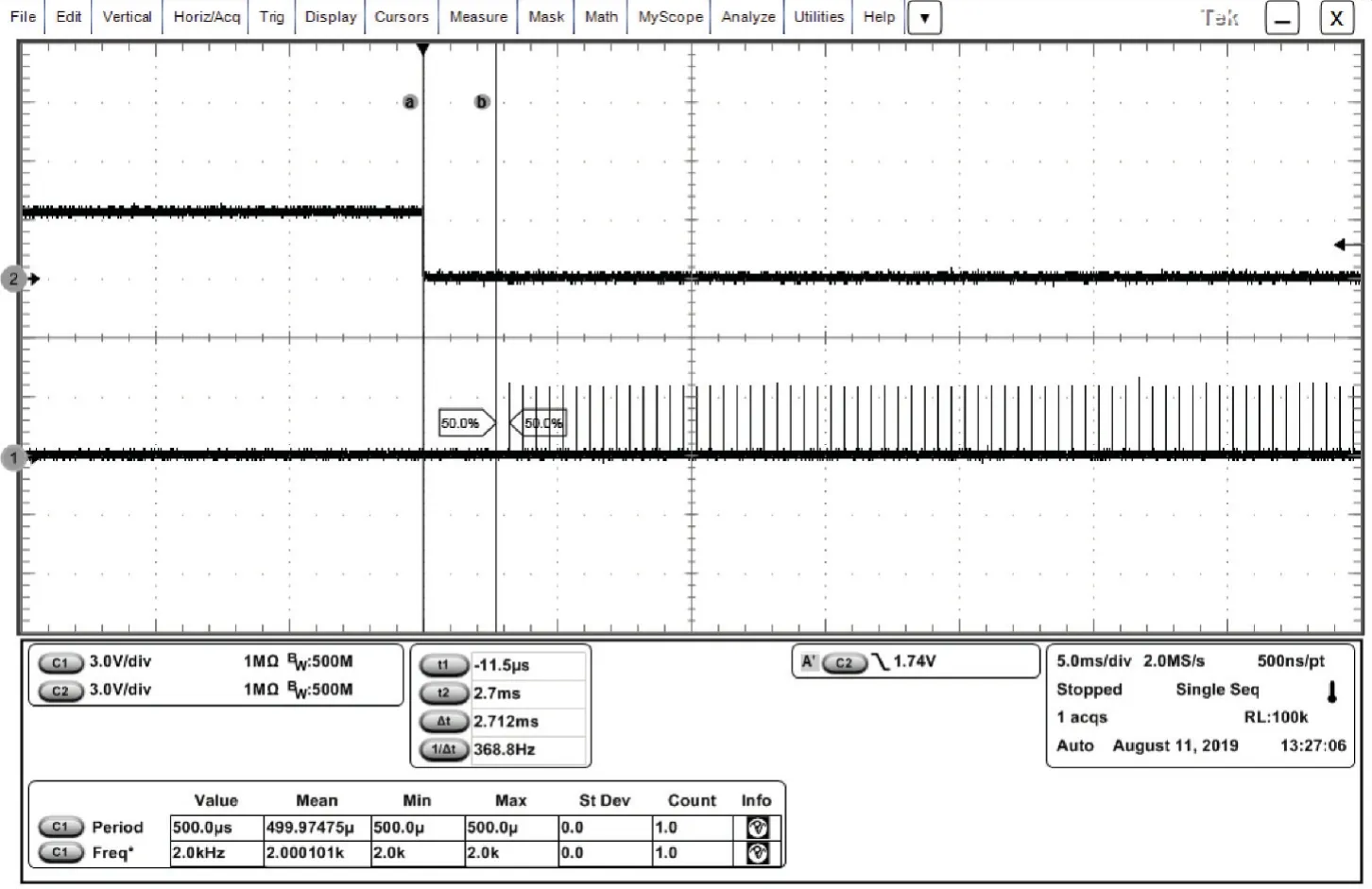

在稳像相机闭环控制成像模式下对帧频和成像时间进行测试,根据要求稳像相机在接收成像指令后需要10 ms 后进入32×32@2 000 fps 的闭环成像模式。 如图5 所示,CH2 通道为稳像相机状态信号,低电平时表示接收到成像指令开始成像;CH1通道为图像2711 接口输出状态信号,高电平有效,示波器显示其频率为2 000 Hz。 实际测试得相机在接收指令 2. 7 ms 后开始成像, 图像帧频为2 000 fps,满足要求。

图5 稳像相机32×32@2 000 fps 工作时示波器测试图Fig.5 Image stabilization camera 32×32@2 000 fps oscillograph test chart at work

2.2 成像试验

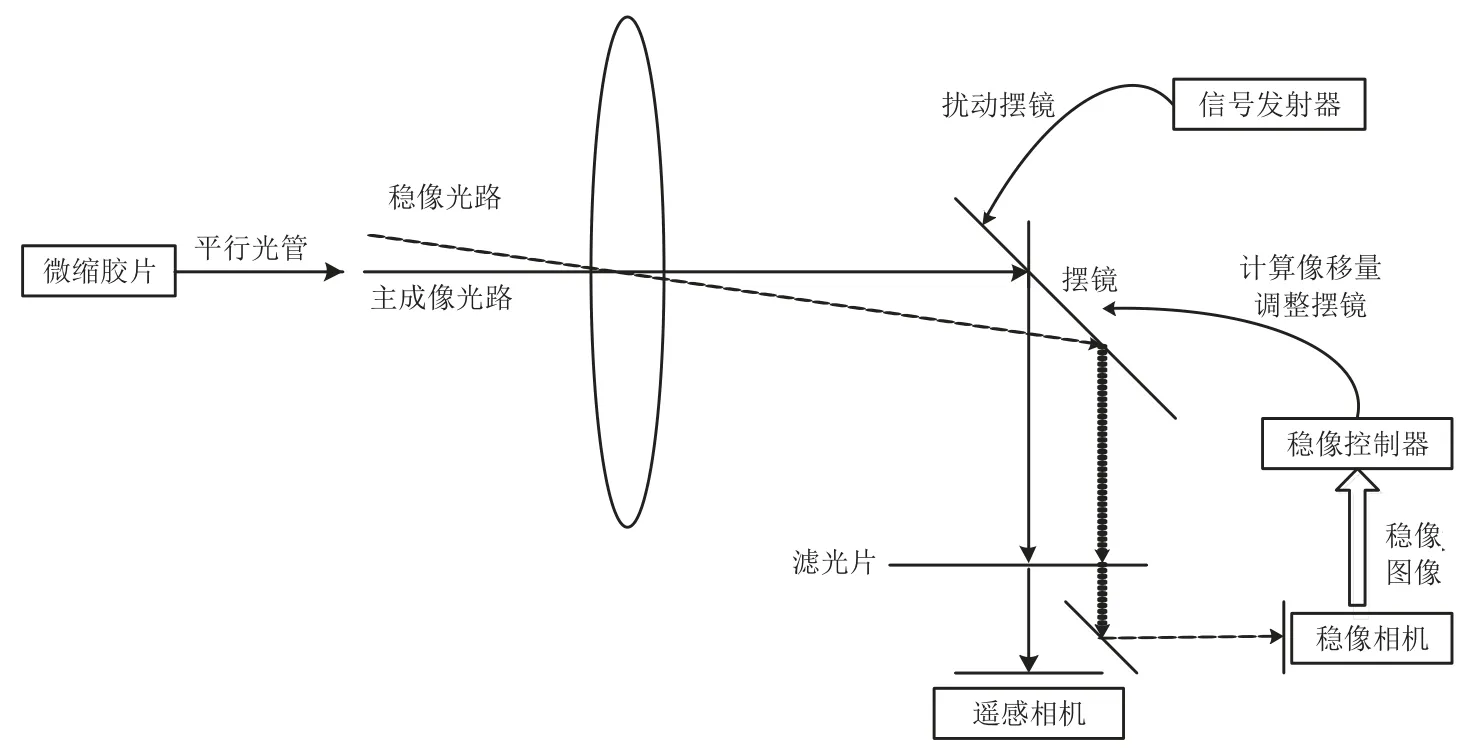

根据系统要求,搭建了系统测试平台,如图6 所示,将典型地物图像微缩底片放置在平行光管前,调节光源亮度,光束经过平行光管后由摆镜反射至稳像相机焦平面传感器;信号发生器输出任意的信号扰动摆镜,模拟光学系统主光轴抖动。 稳像相机工作时首先进入1 280×1 024@50 fps 全画幅搜索模式,当选取到合适的场景后,进入32×32@2 000 fps闭环控制模式。 进入闭环控制模式后,稳像控制器根据稳像图像计算像元的偏移量,摆镜根据偏移量进行调整,使光轴一直处于遥感相机中心,消除成像积分时间内由于光轴抖动引起的图像模糊,达到遥感相机稳像的目的。

图6 稳像系统测试环境示意图Fig.6 Schematic diagram of image stabilization system test environment

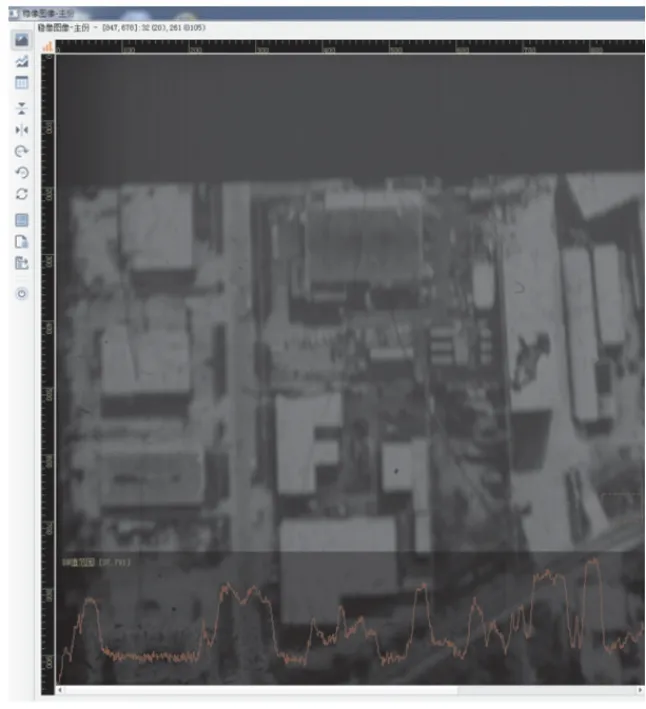

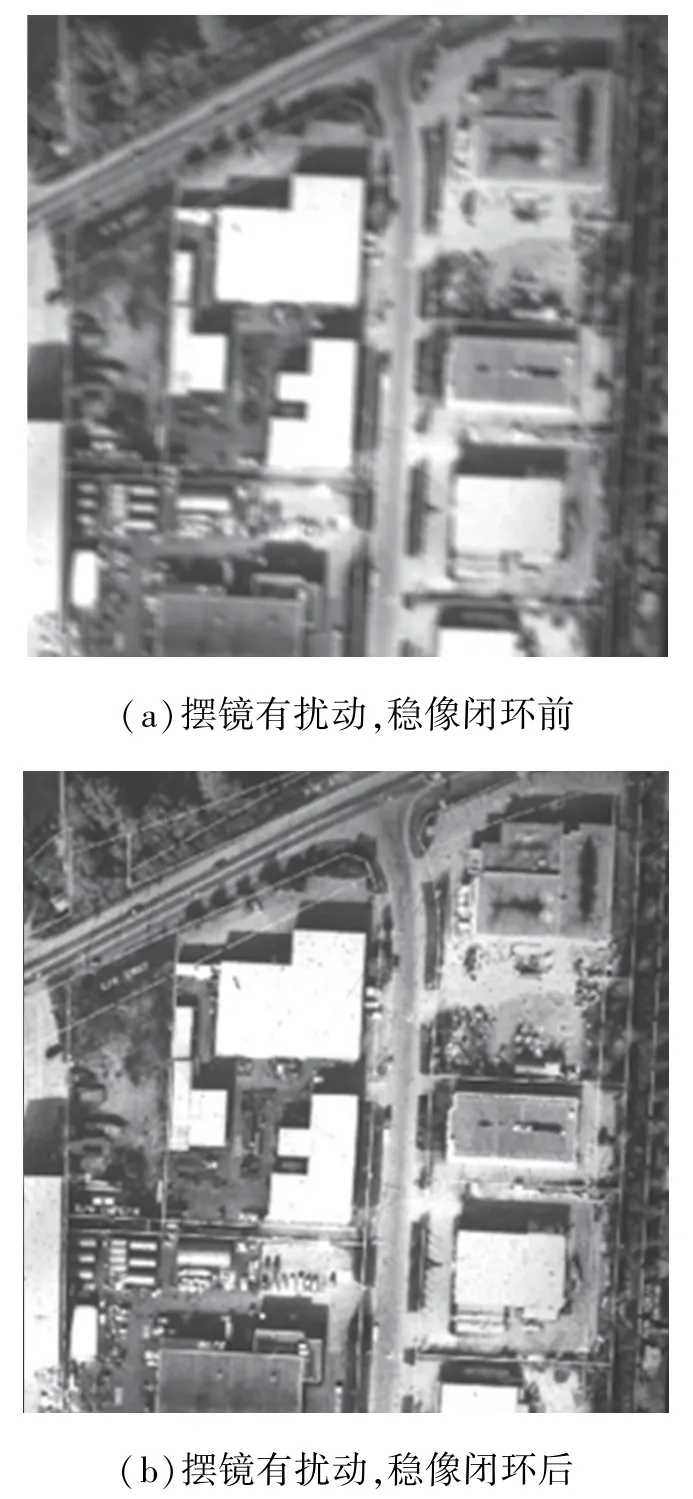

稳像相机首先进入1 280×1 024@50 fps 全画幅工作模式成像图如图7 所示,当稳像相机搜索到目标后进入闭环模式,在稳像相机工作期间,遥感相机在闭环前和闭环后成像装情况如图8 所示,遥感相机在稳像相机进入闭环模式后,成像分辨率得到大幅度提升,同时验证了稳像相机和稳像系统有效。

图7 稳像相机全帧工作拍摄图片Fig.7 Full frame working pictures of image stabilization camera

图8 遥感相机不同时刻成像图Fig.8 Image of remote sensing camera at different times

3 结论

本文介绍了遥感卫星中稳像相机电子学的设计和实现方法。 稳像相机焦平面和遥感相机焦平面共用成像光路,因此稳像相机可用电路面积较小。 本方案通过优化PCB 布局设计,将大面积的宇航级元器件合理的摆放在焦平面电路、信号处理电路和接口电路上,并将3 种电路集成在一块刚挠板上,最大限度节省电路面积。 实际测试得稳像相机最大外包落为114 mm×58 mm×69 mm、质量697 g、功耗小于6 W;为了获得较高的稳像控制带宽,要求稳像相机必须具备千赫兹量级的成像帧频,这就要求相机具备高灵敏度、低噪声的特点,并可以在极短曝光条件下获取图像信息;同时相机需要具备大面阵成像能力,以期拍摄获得足够大的地物场景,为寻找细节丰富的区域开展帧间关联提供可能。 根据稳像方案需求和传感器的特性,将稳像相机设计成具有1 280×1 024 @ 50 fps 全 画幅 搜 索 模 式 和 32 × 32@2 000 fps 闭环控制模式。 在稳像测试系统中测试得到以下结论:稳像相机在全帧频模式下成像清晰;遥感相机在稳像相机进入32×32@2 000 fps 闭环模式后,图像分辨率得到大幅度提升,满足工程应用要求。

该稳像相机的电子学设计方法可以广泛应用于遥感卫星中。 该稳像相机具有1 280×1 024@50 fps全画幅搜索模式,也可执行天基监视和对地遥感等任务。