超结高压MOSFET驱动电路及EMI设计

2021-02-10刘松曹雪刘瞻张龙

刘松 曹雪 刘瞻 张龙

摘 要:分析了超结结构功率MOSFET在开关过程中由于Coss和Crss电容更强烈的非线性产生更快开关速度的特性;给出了不同外部驱动参数对开关过程的dV/dt和di/dt的影响;列出了不同驱动电路开关波形及开关性能的变化。最后,设计了优化驱动电路,实现优化的EMI结果,并给出了相应驱动电路的EMI测试结果。

关键词:超结;驱动;EMI;非线性

0 引言

近几年,超结(Super Junction)结构高压功率MOSFET 由于具有非常低的导通电阻(RDSON)和开关损耗,在各种电源系统中获得越来越多的应用。超结结构通过降低内部晶胞单元的尺寸,采用非常高的单元密度,大幅降低了导通电阻和硅片面积,节省成本。硅片面积的降低也会导致器件的各种寄生电容降低,器件开关速度更快,开关损耗减小,进一步提高系统的效率。

但是,器件过低的寄生电容导致开关速度过快,开关过程中产生过大的dV/dt和di/dt,这会带来EMI设计的问题及栅极振荡。因此,对于超结结构高压MOSFET,需要优化系统及驱动电路,从而在效率和EMI之间达到设计的平衡,满足系统的要求。[1-4]

1 超结结构高压功率MOSFET的开关特性

在开关过程中,平面功率MOSFET的dV/dt、di/dt完全由栅极驱动控制,通过调整外部的栅极电阻就可以控制系统的dV/dt和di/dt。,但是,超结结构功率MOSFET栅极电荷、Coss和Crss的非线性特性增加,在高压下电容变得非常小,在低压时电容又变得非常大,如果使用栅极电阻值取值范围小,柵极驱动电路的栅极电阻参数不能有效控制其开关特性,如VDS电压的变化率主要受输出电容Coss和负载电流控制。

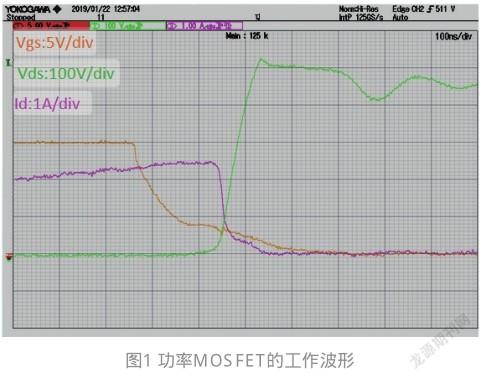

如果超结功率MOSFET想用RG控制关断的dV/dt, RG必须增加到非常大的值,这又会导致开关速度非常慢,增加开关损耗和延时开关。图1展示了功率MOSFET栅极驱动电阻值非常小的工作波形,从波形可以看到,关断的VDS和ID波形的交错区域非常小,类似于零电压开关ZVS的关断模式,因此关断损耗非常小,在硬开关电源结构中,可以提高系统的效率。

2 驱动参数的影响

驱动电路设计的关键的控制参数有:外部串联的栅极电阻RG,外部并联的栅极漏极电容Cgd,以及外部并联的漏极源极电容Cds。

超结结构功率MOSFET的栅极驱动电阻值较小时,dV/dt主要受输出电容Coss和最大负载电流的限制;随着负载电流的上升,di/dt以非常快的速度上升,在大负载电流时,主要受外部寄生电感和外部应用电路的限制。当栅极驱动电阻增加到较大值,di/dt开始部分受到驱动电路的限制,dV/dt情况也基本相同。

如果增大CGD的值,也就是G、D外加并联电容,就可以使用较小的RG,以控制关断的dV/dt,这是一个比较优化的方法。当然,也可以使用增大CDS的值,D、S外加并联电容的方法来控制关断dV/dt,其缺点是会增加开通电流尖峰和di/dt。

如果功率MOSFET流过的负载电流变化范围大,不外加元件,在关断过程中,dV/dt和di/dt也会在很大范围内变动,给系统的EMI和器件可靠性带来问题。

超结结构功率MOSFET通常需要外加一些元件和栅极电阻相配合,控制器件的开关速度,保持栅极驱动电路对器件关断过程的相关参数可控或部分可控,从而保证器件在极端条件下在可靠工作区工作,或满足EMI要求。

栅极电阻低,开关速度更快,开关损耗更低,但会增加开关过程中功率MOSFET的寄生电感和寄生电容所产生的VDS尖峰电压,加剧栅极振荡,同时增加开通和关断过程中电压和电流上升的斜率dV/dt和di/dt。反之,增加栅极电阻,会增加开关过程中的开通损耗和关断损耗,减小VDS的尖峰电压,减小栅极振荡,同时降低在开通和关断过程中电压和电流上升的斜率dV/dt和di/dt。

因此,要基于实际应用和电路特性以及设计要求选择合适的RG值。RG的最大值要保持功率MOSFET开关损耗和温升在设计范围内,RG的最小值保证VDS的尖峰电压、栅极振荡、dV/dt和di/dt在设计范围内。

图3展示了不同的外部参数对关断过程中VDS的尖峰电压、dV/dt和di/dt的影响,外部并联的栅极漏极电容Cgd以及外部并联的漏极源极电容Cds,对于VDS的尖峰电压以及dV/dt的影响和RG一样具有相同的趋势。

3 驱动电路的设计及EMI影响

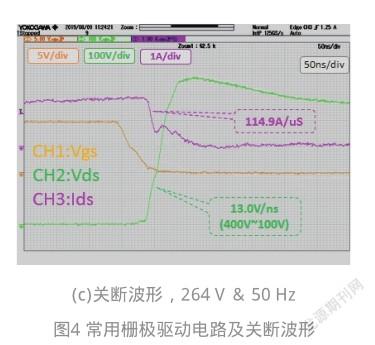

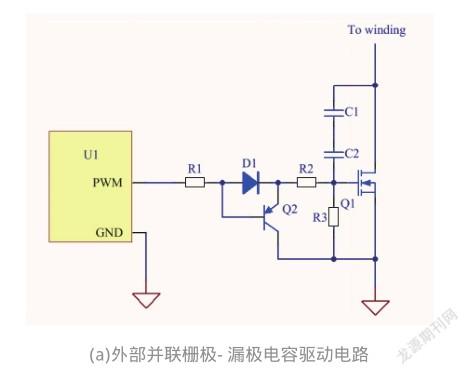

功率MOSFET通常由PWM或其他模式的控制器IC内部驱动源来驱动,为了提高关断速度,实现快速关断,降低关断损耗,提高系统效率,通常要尽可能降低栅极驱动电阻。由于控制器IC和功率MOSFET栅极通常在PCB上有一定距离,因此,在PCB上会有一段引线,这条引线越长,引线电感越大,储存的能量越大,关断过程中容易导致栅极振荡,不仅会产生EMI问题,还有可能在关断过程中关断并不完全,导致其误开通而损坏;同时,如果过高的振零尖峰大于VGS最大额定值,也可能损坏栅极。因此,在很多AC-DC电源、手机充电器以及适配器的驱动电路设计中,通常使用图4的驱动电路,使用合适的开通和关断电阻,并使用栅极下拉PNP管,以减小栅极和源极回路的引线电感。

图4的驱动电路常用于驱动平面结构高压功率MOSFET,可以在各种性能之间取得非常好的平衡。但是,由于超结结构功率MOSFET开关速度非常快,虽然使用这样的驱动电路效率更高,但是,会产生较大的dV/dt和di/dt,从而对EMI产生影响。

采用AOD600A70R,其中,R1=150 ,R2=10 , R3=10 k ,分别在输入120 V & 60 Hz、264 V & 50 Hz, 输出11 V/4 A,44 W条件下测量关断波形,如图4所示。

由于具有足够的空间,电视机的板上AC-DC电源、电脑适配器等可以在实现快开关速度的同时,通过电路系统中的各路滤波器实现EMI性能。而手机快速充电器内部空间极其有限,因此,无法通过周围滤波器保证EMI性能。这种情况就需要优化驱动电路来改善系统性能。当然,对于AC-DC电源、电脑适配器,优化驱动电路同样可以提高EMI性能。[5]

超结结构功率MOSFET的Coss和Crss强烈的非线性特性导致快速开关特性,可以通过外部栅极-漏极、漏极-源极并联电容来改善其非线性特性。在基于图5的驱动电路中,外部并联栅极-漏极电容为11 pF,然后测量关断波形。从图5的波形可以看到,外部并联栅极-漏极电容可以降低di/dt,但是对dV/dt的影响很小。从EMI的测量结果来看,无法达到系统要求。为了提高系统安全性,图中栅极-漏极电容采用2颗高压陶瓷电容串联,C1=C2=22 pF。

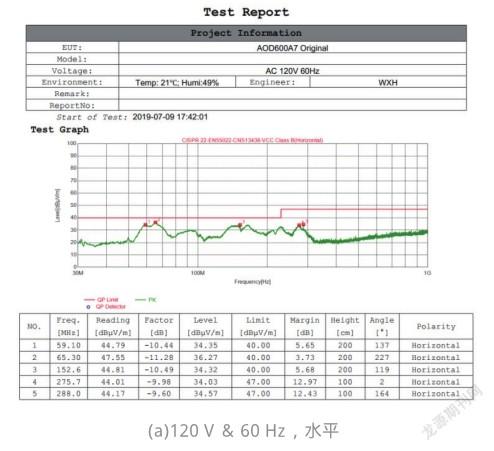

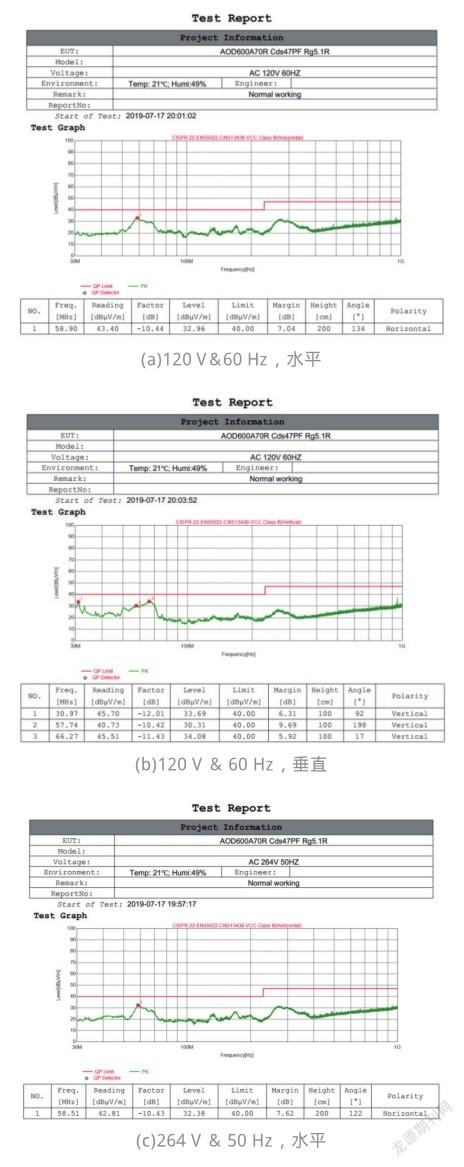

分別在输入120 V & 60 Hz、264 V & 50 Hz,输出11 V/4 A、44 W条件下,使用图4的驱动电路,测量相关辐射。测量结果如图7所示,其结果或者超标,或者达不到系统的裕量要求。

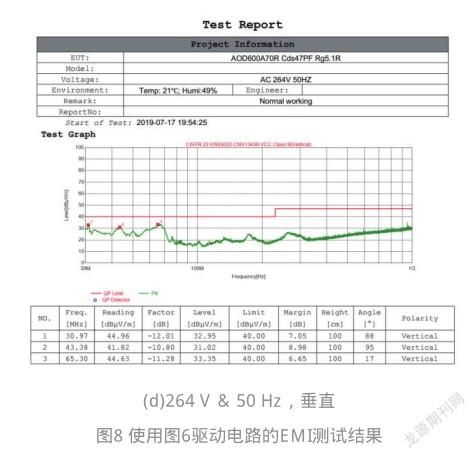

分别在输入120 V & 60 Hz、264 V & 50 Hz,输出11 V/4 A、44 W条件下,使用图6的驱动电路,测量相关的辐射,测量结果如图8所示,这些结果都达到了系统裕量的要求。

4 结束语

超结结构功率MOSFET的Coss和Crss电容更强烈的非线性导致更快的开关速度,产生EMI的设计问题。去除常用的栅极下拉快速关断三极管,增加外部电容,超结结构功率MOSFET的开关特性可以较好实现开关速度、开关损耗和EMI的平衡。

参考文献:

[1] 刘业瑞,刘松.超结结构的功率MOSFET输出电容特性[J].电子产品世界,2020(8):82-84.

[2] 刘业瑞,刘松.功率MOSFET输出电容的非线性特性[J].电子产品世界,2020(10):70-71.

[3] 刘松.再谈米勒平台和线性区:为什么传统计算公式对超结MOSFET开关损耗无效[J].今日电子,2018(5):38-40.

[4] 刘松.超结型高压功率MOSFET结构工作原理[J].今日电子, 2013(11):30-31.

[5] 刘松,孙国营.快充次级同步整流MOSFET对EMI辐射干扰的影响[J].今日电子,2017(8) :32-33.