基于FPGA的在线重构设计方法

2021-01-07王伟伟闫新峰

王伟伟,闫新峰,修 展,徐 进,张 甜

(北京航天长征飞行器研究所,北京 100076)

0 引言

随着航天技术的发展,FPGA凭借其丰富的接口和逻辑资源,逐渐取代单片机和DSP,越来越多地应用到产品设计中。它可以大大减小设计规模,提高设计效率。根据可编程技术不同,FPGA分为SRAM(static random access memory)型、反熔丝型和Flash型[1-2]。由于SRAM型FPGA采用CMOS工艺,集成度高、性能优越、资源丰富、成本低廉,其可重复编程的特性使它拥有广阔的应用,尤其是在航天器的在轨更新和维护方面,优势明显。但航天系统是一个可靠性要求的系统,空间辐射对于SRAM型FPGA影响巨大,会引起单粒子反转,如果导致关键性能失效,很有可能导致任务失败,带来巨大的损失。同时航天工程是一个复杂的工程,需要各系统协同合作才能完成。通常在研制初期,由于进度原因,细节考虑不全或因为用户需求变化,在总装后需要对产品中FPGA软件进行升级才能正常工作,这时如果产品不具备在线重构功能,则必须进行拆卸操作,由此造成了巨大的时间和成本损失,因此FPGA具备在线重构功能成为系统越来越迫切的需求[3-4]。

针对Xilinx 7系列以下FPGA、7系列FPGA和ZYNQ提出了三种提高在线重构可靠性的设计方法,分别为基于ASIC在线重构设计方法、基于MultiBoot多镜像的设计方法和基于ZYNQ的在线重构技术[5-7]。这三种方法几乎涵盖了Xilinx所有FPGA,实现了在线重构技术,提高了系统可靠性。

1 FPGA配置方法

在嵌入式领域,FPGA凭借丰富的接口和逻辑资源,越来越受到工程师的欢迎,尤其是配置方式的多样性和在线重构技术,给工程师提供了丰富的设计方法和设计空间,根据实际需求随时改变设计来实现改变或增加新的功能,提高系统的安全性和可靠性。不同厂家的FPGA配置方式有所不同但大同小异,本文主要针对Xilinx的FPGA进行研究,提出设计方法。

Xilinx FPGA支持多种配置方式,从配置时钟的来源可以分为:主模式(Master Modes)和从模式(Slave Modes);从数据读取方式可分为:并行模式(Master Modes)和串行模式(Serial Modes)。根据这两种不同进行组合,可以得到5种FPGA常用的配置方式:主串、从串、主并、从并和JATG模式。工程上最常使用的是SelectMAP(主并)和SPI模式(主从),分开使用Xilinx的配置芯片PROM和FPGA支持的SPI Flash芯片。SelectMAP和SPI模式采用主模式,FPGA在上电后加载片外Flash芯片中的配置比特流,配置所需的时钟信号(CCLK)由FPGA内部产生,且FPGA控制整个配置过程。自动将配置数据从相应的Flash芯片读入到SRAM中。以7系列FPGA为例,其配置流程大致分为8个步骤,如图1所示。

图1 FPGA配置流程

上电后,FPGA的PROGRAM_B引脚变低开始整个配置过程,可以通过控制FPGA硬件硬件PROGRAM_B引脚的变化来重新配置FPGA。上电后,使用JTAG JPROGRAM指令或IPROG命令,配置存储器将并清空。在此期间,通过使用全局三态将I/O置于高阻态,如果硬件引脚PUDC_B为低电平,则内部上拉。硬件引脚INIT_B在初始化期间内部驱动为低电平,完成后变为高电平。接着设备对外部模式配置硬件M[2:0]进行采样,开始驱动时钟CCLK,将一组32bit特殊的同步字(0xAA995566)发送到配置逻辑。同步字用来将配置数据与内部配置逻辑对齐。设备同步后,先通过设备ID检查才能加载配置数据。如果在配置期间发生ID错误,则设备会尝试重新配置,设备ID检查内置于比特流中。之后FPGA开始加载配置帧,加载配置数据时会根据数据包计算循环冗余校验(CRC),然后和比特流中存储好的CRC值进行比较,匹配通过后FPGA开始进行启动序列,启动完成后,FPGA配置完成,开始正常工作。

根据上述FPGA的配置过程,可以通过软硬件设计保证FPGA能够将配置存储器存储的配置比特流可靠地加载到FPGA中。随着FPGA技术的不断发展,不同代的FPGA产品在重构方便拥有不同的特性。Xilinx FPGA 7系列具备MultiBoot多镜像启动功能,支持在线更新系统,配置文件可以现场动态升级。7系列以前的FPGA则不具备该功能,需要外置芯片来进行重构设计。而对于ZYNQ系列,由于内置有ARM处理器,因此其配置方式更加灵活多样,方便实现在线重构设计[8-10]。

2 基于FPGA的在线重构设计

FPGA软件的一个重要特性是它具有重构性,可以远程实现配置数据的更新,更改软件,实现新的功能。该功能解决了产品在总装后无法在不拆卸的情况下更新FPGA软件的难题,缩短了时间,大大节省了人力财力,提高了效率。针对遥测系统不断变化的需求,软件更新频率很高,因此该功能逐渐变为软件设计的基本要求,增强了产品的安全性和可靠性,大大提高了设计效率。典型的在线升级系统如图2所示。

图2 典型的在线升级系统设计框图

如图2所示,一般地,目标系统和地面系统进行通信采用UART、1553B、Ethernet等接口形式中的一种或多种,实现弹地数据之间的传输。这样就可以将地面系统中更改后的新的FPGA配置文件通过上述接口传输到目标系统上的FPGA控制器,接着FPGA控制flash读写将配置文件正确写入到Flash固定位置,从而实现数据流的更新。FPGA的在线重构技术,关键是要保证在更新失败的情况下,任然可以运行旧版本或可以重新对其进行配置,否则就失去了在线重构的意义。下面针对上文提到的3种设计方法分别进行描述。

2.1 基于ASIC的FPGA在线重构技术

对于Xilinx 7系列以下的FPGA芯片,本身不具备在线重构能力,需要外置配置管理芯片进行配置,从而实现在线重构,提高可靠性和安全性。一般地,对于只存在一个FPGA芯片的设备,可以外加一个MCU或CPLD来实现对FPGA的在线重构设计。Xilinx的应用笔记中给出了基于MicroBlaze软核和CPLD的在线重构技术来实现系统的在线更新。若一个设备中有多个FPGA芯片,且配置芯片也不同,有采用SelectMAP模式的PROM芯片,也有基于SPI模式的Flash存储芯片,各个模块之间通过背板连接。为了减少成本,提高设计效率,可以使用专用ASIC芯片来统一管理各FPGA芯片,实现在线重构,实现框图如图3所示。

图3 在线升级ASIC设计原理框图

该设计可以分别通过JTAG和SPI接口实现对PROM和SPI Flash的读写操作,最大支持8路JATG和8路SPI接口,同时支持JTAG协议的菊花链设计,可以对一个板卡上的多个FPGA进行配置。上位机可以通过UART接口选择对哪个板卡上的某个FPGA进行操作,实现在线升级。同时也可以直接在设备附近使用JATG下载器对FPGA进行在线调试和升级,这样完全保证了在总装完成后也可以对产品进行调试和升级的需求,解决了软件升级需要重新拆装的难题,大大节约了成本,提高了效率。

2.2 基于MultiBoot多镜像的在线重构设计

针对Xilinx 7 系列FPGA可以使用推荐的MultiBoot方案来实现FPGA的在线重构。MultiBoot直接操作的是两个镜像,也可以是多个镜像。其中一个镜像永远不会改变,用于令一个镜像在加载失败时可以返回到该镜像上重新加载,称之为G镜像(Golden Image),后面的镜像称之为M镜像(MuliBoot Image)。当需要进行远程更新实现重构时,FPGA可以直接对Flash 芯片中M镜像存放的位置进行读写操作,G镜像的存储位置和数据永远不变。这样在M镜像出现错误时,可以退回到G镜像,保证FPGA能够正常运行,然后再对M镜像进行更新。MultiBoot实现框图如图4所示。

图4 MultiBoot 实现流程图

一般的FPGA从Flash的基地址开始存放G镜像,后面存放M镜像。根据前面介绍的FPGA配置方法中,上电后,FPGA从地址为0的地方开始加载,也就是先加载G镜像,但是在G镜像的开始位置添加了IPROG(内部编程)命令和M镜像的地址,当FPGA运行到这个位置时会直接跳到M镜像位置开始加载,IPROG是一条命令可以在G镜像中生效,也可以在设计中使用,将IPROG通过内部配置访问接口ICAP(internal configuration accesa port)接口发送,从而实现任意时刻触发重新重构。当加载M镜像过程中遇到IDCode错误、CRC错误、WatchDog超时和BPI地址越界错误时,FPAG会触发退回(FallBack)操作,同时FPGA内部寄存器会记录,发生退回操作后,会忽略IPROG指令,直接加载G镜像后面的配置文件,运行G镜像。

Xilinx 7系列FPGA通过将IRPOG指令潜入到比特流中的方式,实现了FPGA的多镜像启动,确保了FPGA配置的可靠性。IPROG指令内容如表1所示,其中WBSTAR为Warm Boot Start Address Register的缩写,即热启动地址寄存器。

表1 IPROG指令描述

在G镜像中通过加入IPROG指令实现了地址的跳转,当M镜像发生错误后,会触发FallBack操作,退回到基地址位置,FPGA将忽略该部分指令,继续执行G镜像的后面其他部分内容,实现G镜像的加载,正常运行。G镜像中设计有远程更新程序,可以操作Flash芯片,更新M镜像数据,从而实现对M镜像的在线更新,实现FPGA的远程更新和重构。

2.3 基于ZYNQ的在线重构技术

Xilinx ZYNQ与传统FPGA有着巨大的差异,是一款SoC(可编程片上系统),拥有双核ARM A9处理器和7系列FPGA逻辑资源。启动过程体现了以处理器为核心这一特点,先启动处理器(PS)再启动逻辑部分(PL),也就是PL的配置是通过ARM核来配置的,不支持从PL端直接启动配置。

ZYNQ7000的配置按先后顺序分为3个阶段:stage0、stage1、stage2,其中stage2可选。每个阶段的功能及处理过程如表2所示。

表2 ZYNQ配置过程

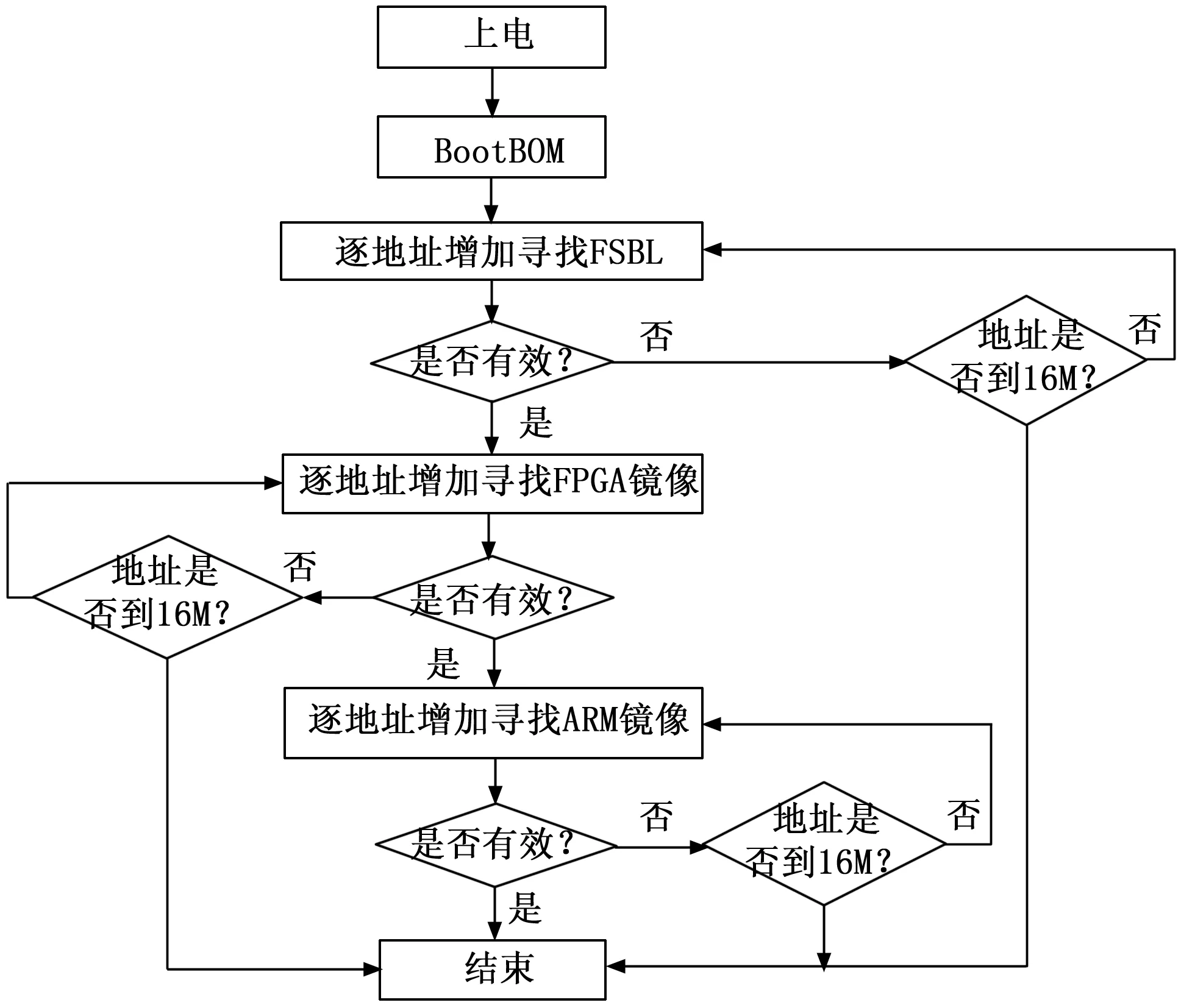

根据表2中的内容可知,ZYNQ上电后先运行BootROM,初始化外部存储设备驱动程序,然后从存储设备的0地址开始,搜索第一阶段启动程序FSBL(First Stage Boot Loader),然后根据FSBL加载PL镜像和后续的PS镜像。基于Qaud-SPI(QSPI) Flash启动方式的ZYNQ启动流程如图5所示。

图5 基于QSPI Flash的ZYNQ启动流程

如图5所示,上电后,ZYNQ运行BootROM,初始化QSPI接口,开始读取Flash中数据,由于BootROM能够访问QSPI Flash的最大地址为16 M,因此在此地址区间内必须存在完整的FSBL。找到FSBL后,根据FSBL开始加载PL和PS镜像。由此可知,如果QSPI Flash中存在多个镜像文件时,ZYNQ只执行第一个镜像,第一个镜像加载不成功才会加载后面的镜像。根据此特性,可设计在线升级方案,如图6所示。

图6 ZYNQ 多镜像在QSPI Flash中的存储位置

如图6所示,在拿到一个全新的ZYNQ硬件设计后,QSPI Flash为空,不存在任何可执行的镜像文件。这时需要用JTAG模式,将Golden镜像下载到QSPI FLash的高地址位置,该地址要大于一个ZYNQ可执行镜像的大小,保证更新时不会破坏到G镜像。在生成镜像文件时,PPGA和ARM执行文件要选择md5校验,这样可以确保镜像的正确性和唯一性。在Golden镜像中有在线升级程序,可以根据地面指令,更新MultiBoot镜像,即从0地址开始更新最新的镜像,由于G镜像和M镜像中的软件版本有区别,这样可以在线验证更新是否成功。如果为成功,版本信息显示G镜像版本;如果成功则显示M镜像版本。通过这种方式可以实现ZYNQ类器件的在线重构,简单方便,稳定可靠。

3 实验结果和分析

针对3种不同的设计方法,通过设计地面软件来实现对FPGA的在线重构。首先打开地面软件,选择待升级的二进制配置bin文件,并计算总CRC。然后再给PFGA上电,FPGA在上电后会发送准备好信号给地面软件,地面收到该信号后会发送在线升级指令给FPGA,如果一分钟内未收到在线升级指令,则FPGA退出在线升级状态,进入正常工作状态。收到在线升级指令后,FPGA开始对配置寄存器进行擦除操作,擦除完成后给地面反馈擦除结果。地面收到擦除完成指令后,开始以每64字节为一包发送有效配置数据,直到所有都完成后,再发送总CRC。FPGA对每包数据进行校验并计算CRC,所有包完成后计算得到CRC,并和地面传送来的CRC进行对比,正确则烧写成功,否则烧写失败。烧写成功后,对FPGA重新加电,通过版本号判断是否更新成功。通过多次测试,3种方式均100%烧写成功,可靠实现了在线升级功能。

4 结束语

针对FPGA类软件可以在线重构的特性,根据Xilinx三种不同类型的FPGA的不同特性,分别提出基于ASIC的FPGA在线重构技术、基于MultiBoot多镜像的在线重构设计以及基于ZYNQ的在线重构技术设计方法。Xilinx所有的FPGA,均可通过这三种技术中的一种或某种组合实现在线重构,解决了总装后无法进行软件更新的难题,同时保证了在线重构的安全性和可靠性,提高了设计效率。