一种宽带数字多波束发射技术的实现方法

2021-01-07詹银芳

肖 恒,詹银芳

(中国电子科技集团公司第三十六研究所,浙江 嘉兴 314033)

0 引 言

通信对抗是当前军事战斗的重要部分,随着通信技术的发展,越来越多的抗干扰措施(如扩频通信、自适应调零天线、自适应滤波等技术)得以应用。而最大限度提高发射机输出功率成为干扰措施中的难点,如采用波束合成技术能有效降低发射机输出功率并可灵活改变合成波束指向。因此,波束合成技术在电子对抗领域中得以广泛应用。

早期的波束合成通常运用在模拟射频端,通过移相器、放大器等射频器件完成通道幅相加权处理,这种实现方法硬件电路复杂,无法形成多波束,灵活性差[1]。随着数字信号处理技术的发展和处理芯片性能的提高,数字波束合成技术在工程中得以实现。

1 技术原理

宽带数字多波束发射技术作为数字波束合成技术的一种,是宽带数字波束形成(DBF)发射中的关键技术。运用该技术可以补偿天线阵内相位差和通道时延差,解决通道带内群时延一致性的问题。因而,数字多波束发射技术为波束合成提供理论支持和实现方法。

本文着重论述一种宽带数字多波束发射技术的实现方法,即在数字电路基础上,利用数字信号处理(DSP)、现场可编程门阵列(FPGA)灵活的可编程性,通过软件编程解决宽带多波束(同频或者异频)快速合成的技术难题。图1为宽带数字多波束发射技术的组成框图。

图1 宽带数字多波束发射技术组成框图

首先由DSP根据发射波束的方位指向和数字多波束合成算法计算需要补偿的各个通道的时间参量和相位参量;其次运用并行信号数字产生技术产生所需的数字或者模拟调制信号;再由DSP把相位和幅度参量发送给幅相加权网络进行补偿,并把时间参量转变为数字滤波器的系数发送给并行分数时延滤波器;经并行分数时延滤波后的信号再通过高速串行总线发送给高速DAC阵列,完成多通道信号输出;最后经功率放大器组和天线阵把多通道放大信号辐射出去,最终在指定空域实现空间波束合成。

2 实现方法

2.1 数字多波束合成算法

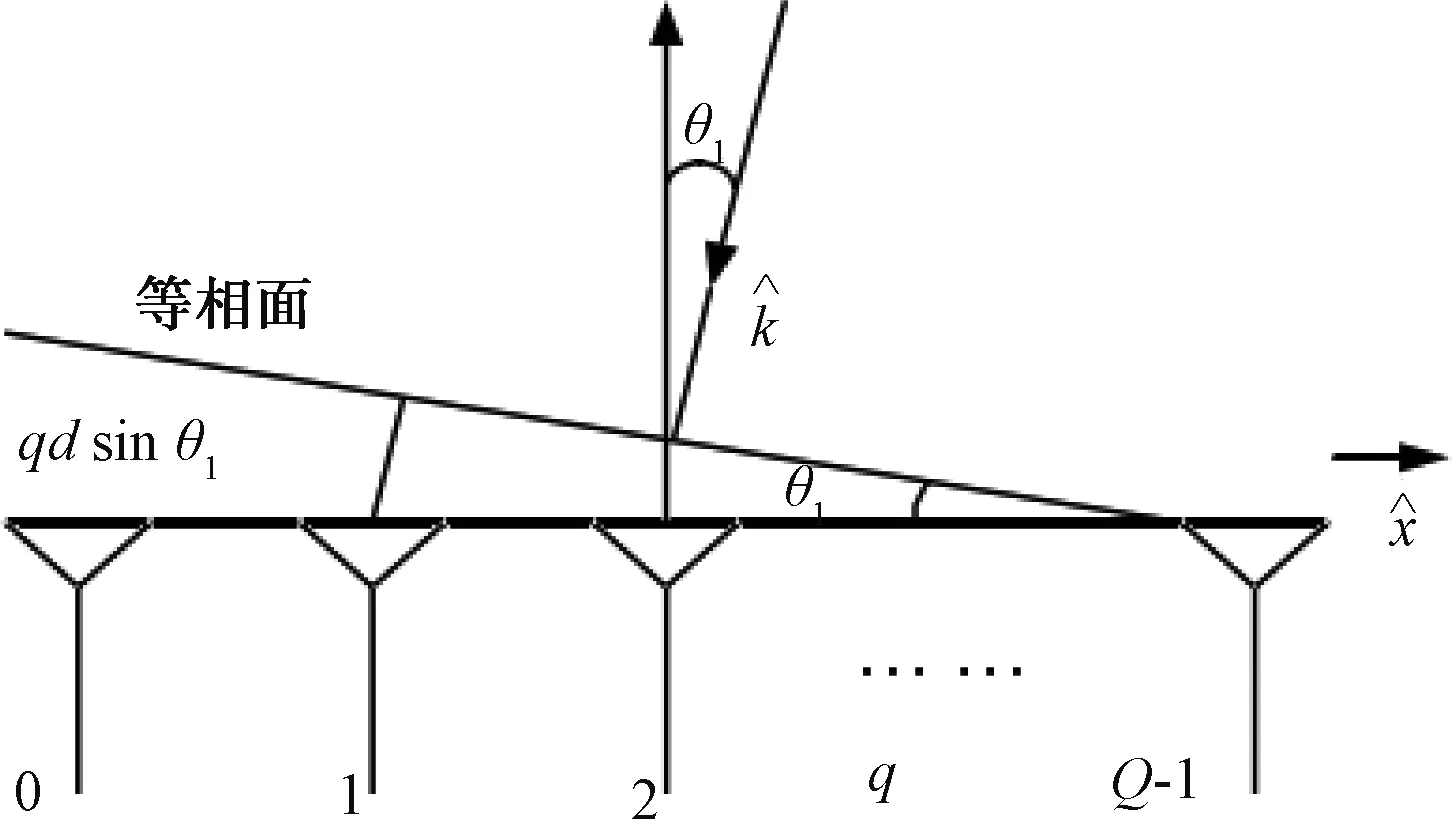

如图2所示,一个沿X方向从q=0,1,…,q-1的q个阵元的线性天线阵列,这个阵列中的阵元天线均匀分布,间距为d[2]。如果输出信号是正弦波,那么第q个阵元输出为:

x(q,t)=Acos[2πf1(t-τq-tq)-Φ)]=

Acos[2πf1t-2πf1(τq+tq)-Φ)]

(1)

式中:A为输出信号的幅度;f1为频率;tq为第q个通道和第1个通道(q=0)的通道时延差,由硬件系统决定,是个定值;Φ为第q个通道和第1个通道(q=0)的本振相位差,也是个定值;τq为第q个阵元与第1个阵元(q=0)的相位延迟时间,即空间相位差。

若天线阵元之间的距离为d,则这个延时为:

(2)

式中:θ1为图2中所示的波束指向和法线的夹角,实际应用范围为-π/4到π/4之间;c为光速;实际应用中距离d是固定的;q相对于每个阵元来说也是固定的。

多波束合成在不需要进行波束赋性的情况下只需把式(1)中的数字信号进行叠加。

图2 线性阵列和平面波

2.2 并行数字信号产生

图3为并行数字信号产生原理框图,FPGA内软件功能模块包括调制码元生成、锁相环(PLL)时钟电路、内插滤波器、多相滤波器和数字控制振荡器(NCO)正交混频器。首先低数据速率的调制码元信号分IQ两路,再经内插滤波后提高到高速率的基带信号,然后经多相滤波与NCO电路产生的载波信号进行正交混频,最终实现并行数字信号输出。

图3 并行数字信号产生

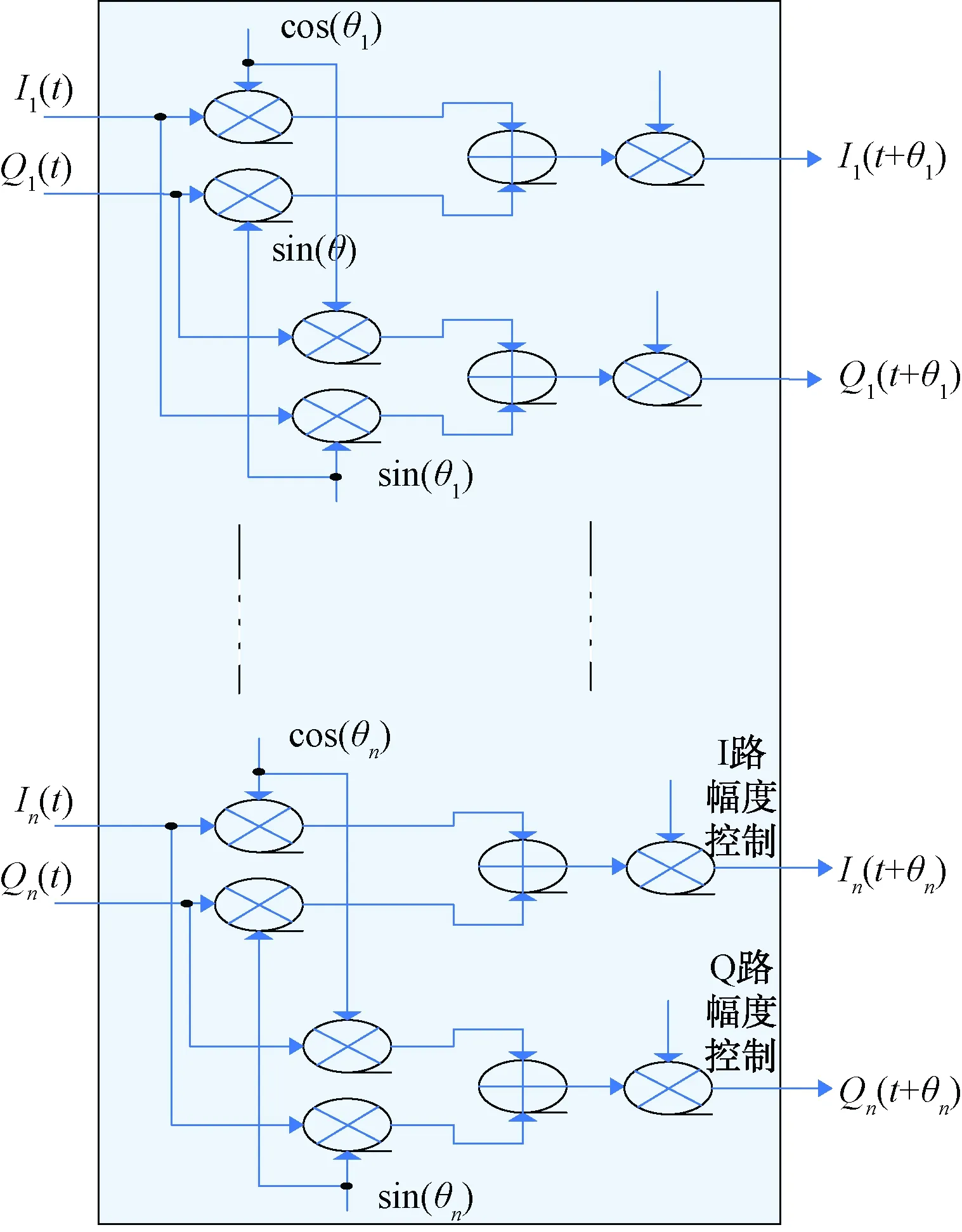

2.3 幅相加权网络

幅相加权网络原理框图如图4所示,主要用于补偿本振相位差或者多片DAC之间的采样时钟相位偏差和多路射频信号之间的幅度偏差。幅相加权网络采用数字正交体制,采用16位量化,相位精度优于0.1°,移相范围0°~360°。I路和Q路的幅度控制采用16位量化,幅度控制范围为0~96 dB,幅度控制步进可精确到0.1 dB。

图4 幅相加权网络

2.4 并行分数时延滤波器

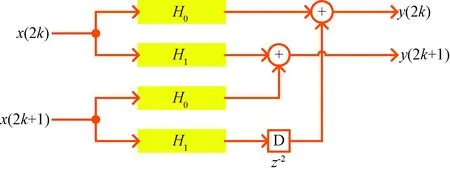

并行分数时延滤波器用于补偿天线阵内相位差和通道时延差,该滤波器设计为通过时延补偿时延差的方式奠定了基础。并行分数时延滤波器实现构架如图5所示。

图5 并行分数时延滤波器实现构架

并行分数时延滤波器的时延精度是判决滤波器是否能满足设计需求的最重要指标。并行分数时延滤波器的时延精度取决于2个因素: (1)滤波器工作时钟。这是时延精度的主要因素,29阶的滤波器的群时延特性如图6所示,时延精度为1/500的采样时钟,如400 Mbps的采样速率,时延精度可以达到5 ps,这个数量级能满足6 GHz以下所有频段的波束合成的指标需求。(2)滤波器的阶数。这是时延精度的次要因素,当滤波器阶数提高,在一定程度上可以提高时延精度。

图6 29阶系数量化之后的分数时延滤波器群时延

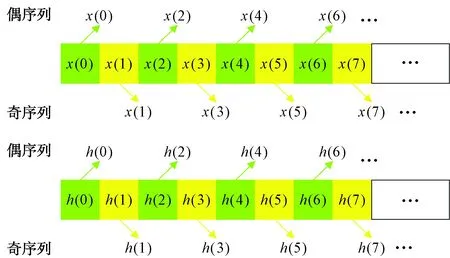

并行分数时延滤波器结构是将“待卷积”的2个序列x(n)和h(n)按交叉数据分配的原则分为“相同数量的”若干个子序列[3],二相分解公式表达如下:

在频域,可表示为:

X(z)=X0(z2)+z-1X1(z2)

(3)

同理,有:

H(z)=H0(z2)+z-1H1(z2)

(4)

其中,当N为偶数时,有:

(5)

若N为奇数,只需修正式(5)的求和上标即可,二相分解过程如图7所示。

滤波结果的频域可表示为:

图7 二相分解过程

Y(z)=X(z)H(z)=(X0(z2)+z-1X1(z2))(H0(z2)+z-1H1(z2))=

X0(z2)H0(z2)+z-1X0(z2)H1(z2)+z-1X1(z2)H0(z2)+z-2X1(z2)H1(z2)=

(X0(z2)H0(z2)+z-2X1(z2)H1(z2))+z-1(X0(z2)H1(z2)+X1(z2)H0(z2))

(6)

2.5 高速DAC阵列

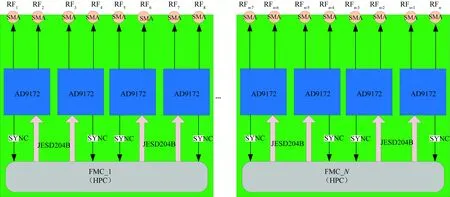

高速DAC阵列实现框图如图8所示,数模转换板卡我们采用AD9172芯片,该芯片是一款高性能双通道16 bit DAC,支持最高12.6 Gsps采样率,其输出频率最高可达到6 GHz。图8中1块数模转换板卡可同时产生8路信号,若增加板级同步信号可扩展射频通道路数。因此,高速DAC阵列技术的应用大大降低了宽带数字多波束合成对于射频电路规模的需求,更解决了模拟器件无法在宽带频段内做到较好一致性的问题。

图8 高速DAC阵列组成图

3 结束语

采用基于数字多波束合成算法、并行数字信号产生、幅相加权网络、并行分数时延滤波、高速DAC阵列的宽带数字多波束发射技术产生的信号频率范围广、信号带宽宽(仅受制于DAC的采样速率),很好地解决了宽频段多波束合成时天线阵内相位差和通道时延差问题,合成效率高且硬件规模小,实现过程简单。工程应用中仅通过软件编程即可产生高码速率的宽带调制信号、宽窄带多波束电扫等复杂信号,具有广阔的应用前景。