一种X波段锁相环频率合成器的设计与实现

2020-12-25郝延刚

郝延刚,祁 全,吴 梅

(1. 海军装备部驻南京地区第二军事代表室,南京 211153;2.中国船舶集团有限公司第八研究院,南京 211153)

0 引 言

作为雷达和通信系统的重要组成部分,频率合成器在工作时产生高准确度和稳定度的本振基准信号,供雷达及通信收发模块对载波信号进行调制解调及相参处理。[1-3]本振信号频谱质量的优劣直接关系到雷达及通信收发系统的信号处理能力。高质量的频率合成器可有效提高雷达接收机的灵敏度及目标检测能力,降低通信系统解调信号的误码率,实现更加安全准确的无线通信。

频率合成器的主要技术指标有相噪、杂散、跳频时间等,其中相噪是衡量频率合成器输出信号质量最关键的技术指标。在雷达系统中,本振信号的边带相噪直接决定接收机的灵敏度和选择性,影响雷达检测目标的能力。杂散是偏离载波离散频率上的干扰信号。它会与其他信号混频产生不期望的噪声产物,恶化接收机系统的噪声系数和动态范围。跳频时间影响雷达系统处理数据的速度,足够迅速的跳频能保证雷达系统单位时间内实现频率快速捷变,提高雷达对抗能力。

基于锁相环(PLL)技术的频率合成器具有较宽的频率输出范围、高杂散抑制和较好的相噪性能,成为现代电子信息系统中应用最广泛的频率合成器件。本文以PLL频率合成方法进行频率合成仿真与电路设计,并对其输出的点频信号展开研究。

1 结构与理论分析

1.1 PLL结构

PLL是一个闭环相位负反馈系统,其基本结构包括鉴相器(PD)、环路滤波器(LP)、压控振荡器(VCO)。[2]历经数十年成熟的理论研究和实践应用,以及数字技术的进步,现今基于PLL的频率合成技术还增加了参考分频器(R)、环路分频器(N)、电荷泵(CP),称为数字锁相环技术。

本文基于数字锁相环技术的PLL频率合成器结构如图1所示。

图1中,锁相环路中所用的PLL芯片和VCO芯片采用美国HITTITE公司的HMC704和HMC509,其主要技术参数如下:

PLL芯片HMC704:

▶ 频率范围:DC~8 GHz,fPFD:115 MHz;

▶ 基底相噪:-233 dBc/Hz。

VCO芯片HMC509:

▶ 输出频率:7.8~8.8 GHz,内置二分频;

▶ 开环相噪:-115 dBc/Hz@100 kHz;

▶ 输出功率:10~15 dBm。

1.2 相噪理论分析

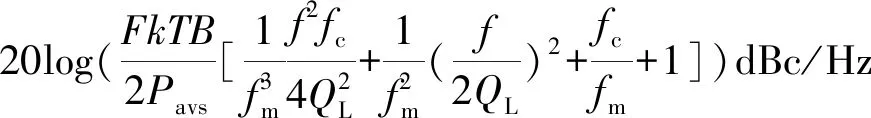

相噪是衡量PLL性能最重要的指标。通过理论分析,对相噪性能进行合理评估,可为实际设计和测试提供理论参考。振荡器的相噪模型依据leeson相噪方程[4],如式(1)所示。

(1)

由式(1)可知,相噪的组成成分包含1/fn(n=0~3),近端相噪主要受闪烁噪声(又称1/f噪声)主导。考虑到leeson相噪方程结构复杂,工程应用中难以做到准确分析。

出于简化理论分析需要,工程师在实际应用中更多采用式(2)[4-5]对PLL的带内相噪性能进行粗略评估。

PN=PN1Hz+10logfPFD+20logN

(2)

式中,PN1Hz是PLL芯片的基底相噪。根据式(2),带内相噪主要依赖于环路分频系数N,其数值将以20logN恶化。分频系数越大,相噪性能越差,因此通过降低分频系数可有效改善带内相噪性能。由于本文所设计的PLL频率合成器产生点频信号,无需考虑频率步进,在保证环路工作稳定的前提下应尽可能设置大的鉴频鉴相频率fPFD,从而降低分频系数,改善带内相噪性能。

2 设计与实现

根据要求,所设计的PLL频率合成器产生8.4 GHz的点频信号。PLL芯片HMC704整数模式下fPFD高达115 MHz,此处设置fPFD=100 MHz,以获得较好的相噪指标。首先对PLL的相噪性能进行必要的仿真分析,初步评估系统性能,进而优化相关设计。

2.1 环路滤波器设计与相噪仿真

环路带宽的设置是PLL频率合成器调试最重要的工作之一。若设置的环路带宽较宽,则锁定时间变短,但因滤波不充分将产生较大杂散信号,反之锁定时间变长。若无特别要求,出于折中考虑,通常设置环路带宽值为PLL芯片和VCO芯片相噪值相等处的频率,这样可最大限度地兼顾锁定时间和杂散指标。

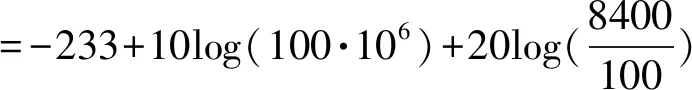

根据式(2)可得,PLL带内相噪理论值为

=-114.5 dBc/Hz

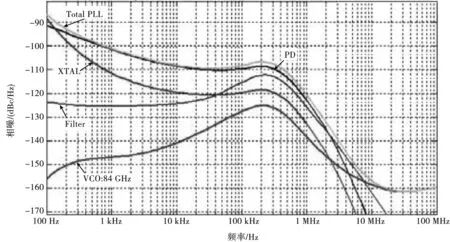

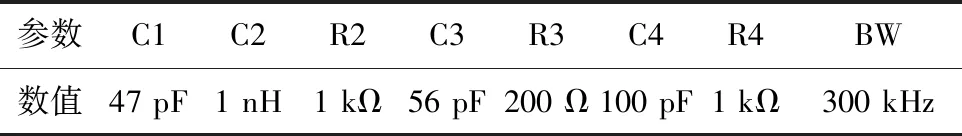

参考VCO芯片的相噪测试图[5],两者在频偏100 kHz处相近,因此在仿真初期可设置环路带宽值为100 kHz左右。仿真过程中,当设置环路带宽100 kHz时,在环路的“肩膀”处出现了较大的过冲现象。此处的相噪甚至高达-90 dBc/Hz,而且整体近端相噪也有所抬升,无法满足实际应用。因此,需要适当增大环路带宽。经过反复仿真,最终设置带宽300 kHz。图2是设置带宽300 kHz的相噪仿真曲线。从图中可以看出,从1~100 kHz的近端相噪均优于-100 dBc/Hz。考虑到PLL的电荷泵电压无法满足VCO的高调谐电压,环路滤波器采用有源四阶结构[6],如图3所示。表1给出环路滤波器的元件参数。

2.2 版图实现与测试

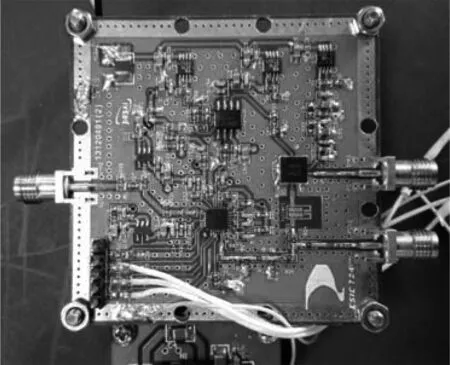

PCB测试版图如图4所示。采用外部连接100 MHz恒温晶振OCXO和89C2051单片机控制,版面尺寸60 mm·60 mm。若合理布局,并采用更小封装的基础元器件,可进一步缩小尺寸。为了获得较纯净的反馈信号频谱,抑制谐波分量或杂散信号对PLL的调制,在VCO输出反馈端设计了一个低通滤波器。

图2 相噪仿真曲线

表1 环路滤波器参数

图4 测试版图示意

图5是Span分别设置为1 GHz和10 MHz时的输出频谱图。从图中可以看出,宽扫频和窄扫频下的频谱均非常纯净,频率准确锁定在8.4 GHz处。

利用信号源分析仪E5052B测试得到的相噪曲线和频率稳定度如图6所示。图2与之比较可发现,两者相噪曲线吻合较好,验证了仿真结果的可靠性。从图6得到,相噪曲线上无明显参考杂散干扰和工频谐波信号,1 kHz频偏处的相噪优于-100 dBc/Hz,10和100 kHz频偏处的相噪接近-110 dBc/Hz,1 MHz频偏处的相噪优于-120 dBc/Hz。频率抖动达到亚皮秒级,在100 Hz~100 kHz带宽内,抖动低于160 fs。输出功率约4.9 dBm,注意到测试所用线缆在8.4 GHz处的损耗约5 dB,SMA转接头和走线损耗约2 dB,故实际输出功率可达12 dBm,与VCO芯片所给指标是一致的,能够满足一般收发系统对功率的指标要求。

图6 相噪和频率稳定度测试结果

3 测试数据分析

理论研究表明,PLL的近端相噪主要由参考源和PLL的相噪特性决定,而远端相噪由VCO的相噪特性决定。从仿真曲线可以看出,OCXO只在非常靠近输出频率(频偏100 Hz以内)时才对相噪起决定作用,而环路滤波器截止频率附近的相噪性能又同时受到多个器件影响,无法准确分析各器件对相噪的贡献。考虑到雷达系统对载波信号的近端相噪有较高要求,因此主要分析频偏1 ~100 kHz范围内的相噪性能。

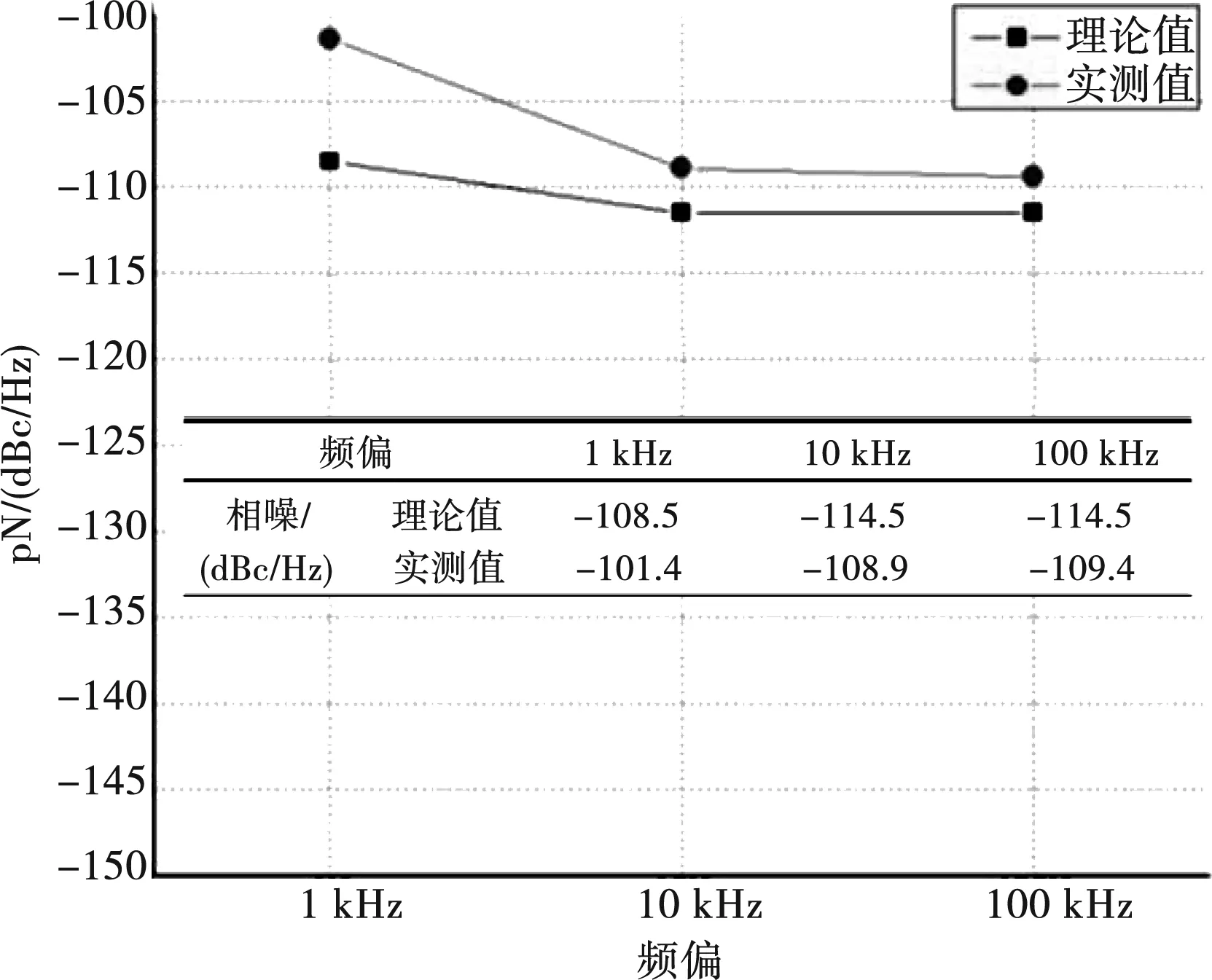

根据1.2节的分析,评估PLL带内相噪性能时忽略了闪烁噪声对近端相噪(频偏100 Hz~1 kHz以内)的影响。假设闪烁噪声与基底噪声对PLL近端相噪的贡献是相同的,则相较仅受基底噪声的贡献,理论相噪在此频率范围内将会恶化3 dB。参考芯片数据手册、理论分析和实测数据,汇总得到图7。

根据图7所示,实测曲线与理论曲线具有一致的变化趋势。实测值与理论值最大相差7.1 dB@1 kHz,最小相差5.1 dB@100 kHz。一方面,简化理论分析后削弱了闪烁噪声对近端相噪的决定影响,从而导致1 kHz处的差值最大;另一方面,PLL受到电源纹波和工频等干扰对带内相噪的调制,且未采取有效的电磁屏蔽措施,恶化了EMC特性。

图7 近端相噪理论值与实测值比较图

综上所述,所实现的PLL频率合成器采用大鉴频鉴相频率,输出点频信号具有优异的相噪和杂散特性,达到了设计要求。通过充分的电源去耦和电磁屏蔽,近端相噪性能仍有提升的空间。通过进一步合理设置环路滤波器带宽和相位裕度,有望改善过冲效应和远端相噪性能。

4 结束语

本文设计了一个X波段的PLL频率合成器。测试结果显示,输出信号频率为8.4 GHz,频谱质量纯净,无明显杂散干扰,1 kHz频偏处的相噪优于-100 dBc/Hz,可为雷达收发系统提供优质的本振信号。