一种原子钟伺服电路的控制及测试方法*

2020-12-23赵广东闵康磊李思衡郑荣磊

赵广东,赵 阳,闵康磊,李思衡,郑荣磊

(1.上海航天电子技术研究所,上海 201100;2.中科院上海天文台,上海 200030)

0 引言

原子钟是时间频率的源头,直接决定了时间频率的准确性和稳定性。原子钟研制难度大,涉及量子力学和电子学等多个领域,其中就包括氢脉泽、铯原子钟、粒子囚禁、激光冷却、光学频率梳等相关发明出现。原子钟种类繁多,应用领域各不相同,技术指标各有所长。其中氢原子钟就具有非常好的中短期稳定度,可长期连续运行,主要用于守时。近年来,随着我国“北斗”卫星导航系统的建设,星载原子钟的研制和应用取得了长足进步。本文主要探讨的是一种被动型氢原子钟伺服控制电路的测试方法。

1 伺服控制电路实现方案

1.1 硬件设计实现

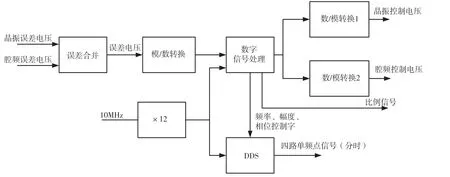

被动型氢原子钟的伺服控制电路是氢原子钟锁定控制的核心部件。其通过数字量化控制的方式,实现对微波谐振腔探测信号时序的控制、原子跃迁信号的采集及其误差增量式PID 计算,得到微波谐振腔及晶振双环路的反馈输出。

伺服控制电路由误差合并、误差信号处理和DDS 频率合成电路三个主要功能模块组成。其中误差信号处理模块包含两个环路的误差信号采集处理,一个环路用来将恒温晶振的10MHz 输出信号锁定在氢原子的跃迁频率上,另一个环路将微波腔谐振频率锁定在恒温晶振的10MHz 输出信号上。DDS 频率合成模块产生共用一个通道的两组分时探测信号,经过上变频后作为探测信号分时馈入物理微波谐振腔进行激励,两路误差信号时间上相互分离,互不干扰,物理部分的输出经过变频、检波进入伺服模块后,分时进行PID 运算,产生恒温晶振压控电压和控制微波腔中心频率的变容二极管的控制电压。

1.2 信号工作流程

被动型星载氢原子钟伺服控制电路的信号工作流程是由FPGA 产生时序控制信号,将晶振和微波谐振腔两路分时的误差信号按固定的时序关系合成一路,通过数模转换器DA 后进行信号采集,在FPGA 内部完成PID 运算,得到晶振和变容二极管的电压控制量,并通过数模转换器得到模拟电压量。这个过程是周期进行的。FPGA 生成DDS 模块的频率控制字、相位控制字,在时序控制信号的控制下,DDS 环路产生系统需要四个单频点的跳频信号。数字伺服控制电路中,FPGA 和DDS 的系统时钟均为120MHz,是通过锁相环路相位锁定到隔离放大电路后级的10MHz 高稳信号实现的。伺服控制电路信号框图如图1 所示。

图1 伺服控制电路组成框图

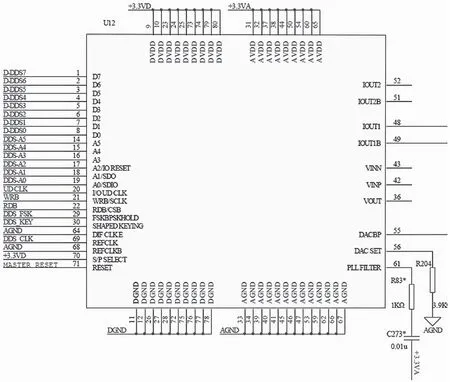

1.3 DDS 频率综合电路

DDS 频率综合电路采用了国产化DDS 专用芯片GMD9852A,是一款抗辐射数字频率合成器,工作频率最高可达300MHz。内部集成两路高速、高性能的12 比特DAC,输出正交的正余弦波形。芯片内部包括一个48 比特宽的相位累加器,一个48 比特宽的频率累加器,一个14 比特宽的相位调整加法器,一个12 比特宽的幅度调整乘法器,能够提供高精度的频率合成、相位调整以及幅度调整。GMD9852A 的工作模式包括单频点模式(single_tone)、幅度键控模式(Amplitude Shift Keying)、频率键控模式(Frequency Shift Keying)、相位键控模式(Binary Phase Shift Keying) 以及用户可定义的线性或非线性频率扫描模式(RAMP/CHIRP )。芯片集成并口和串口配置方式,串口配置速度最高可达50MHz,并口配置速度最高可达150MHz,可实现高速的、灵活的配置方式。伺服控制电路的频点时序要求输出两组频率F1、F2 和F3、F4,输出频点为F1=f0+12.5Hz、F2=f0-12.5Hz(f0 频率范围20.4MHz~20.5MHz)、F3=f1+50KHz 以及F4=f1-50KHz(f1 频率范围20.3MHz~20.6MHz);伺服控制电路的时序要求如图2 所示。

如图2所示,t1=t2=t3=t4=40ms,T1=4.04s,T2=400ms。DDS 系统时钟为时钟驱动器提供的120MHz 差分正弦波信号,差分信号峰峰值约400mV,应用FPGA实现控制工作,S/P 设置为高电平,采用并口配置方式,单频点工作模式,内部PLL 锁相环未应用。GMD9852A 输出连接比例减法运算电路,实现跳频信号输出功率要求。

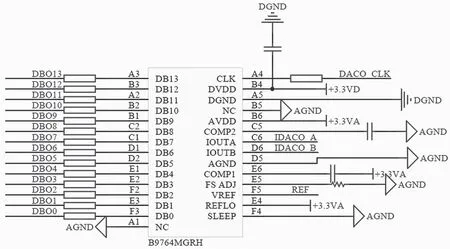

DDS 专用芯片GMD9852A 的原理图设置如图3所示。

图2 输出频率点时序图

图3 GMD9852A 设置原理图

DDS 输出频率由式(1)计算得出,f0表示输出波形的频率,fs表示系统时钟频率120MHz,FTW表示48 比特频率字,通过串口地址0X02 可配置,通过改变频率字即可输出四个频点F1,F2,F3,F4。输出频率须小于奈奎斯特频率,即1/2fs。F1,F2,F3,F4时序控制通过设置FPGA 软件对系统时钟分频后的计数器来实现。

输出的相位由式(2)控制,Phase 表示输出波形的相位,单位为度,POW 表示14 比特相位字,通过控制该相位字的值来控制输出波形的相位。

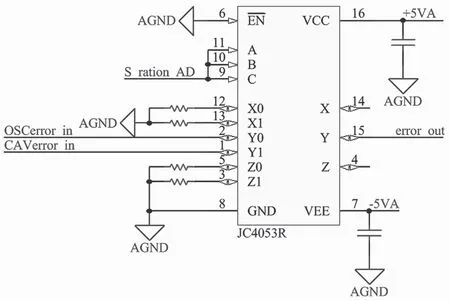

1.4 误差合并电路

被动型星载氢原子钟共有微波谐振腔腔频误差CAVerror 及晶振环路误差OSCerror 两路需要处理的误差信号。其输出的时序关系与图2 是一致的。F1 及F2 输出时间对应晶振环路误差OSCerror,F3及F4 输出时间对应微波谐振腔误差CAVerror。故需要将包络检波后提取出的上述误差信号通过模拟开关JC4053R 合并电路合为一路的分时误差信号error_out,其时序关系与探测信号时序关系一致,实现电路如图4 所示,s_ration 控制Y 通道输出的开关时序,在相应的周期内将Y0 或者Y1 对应的信号切换至error_out。

合并后的误差信号error_out 经过电压变换后送入误差信号处理电路处理。

1.5 误差信号处理电路

完成了1.4 节的误差信号合并后,经过模数转换AD 电路将两路分时误差信号数字量化后的数据送入FPGA 电路进行处理,经过计算的结果分别送入晶振通道数模转换器DA1 电路以及微波谐振腔通道数模转换器DA2 电路。误差信号是低速信号,故误差信号处理电路可以用较低的时钟处理。AD及DA 的处理时钟通过FPGA 内部DCM 单元分频处理后输出。

图4 误差合并原理图

误差信号处理电路对DA1 和DA2 输出的两路反馈控制电压的噪声有着较高的要求,其不能对恒温压控晶振有额外的低频噪声干扰,噪声会导致原子钟的短期稳定度恶化,故两通道的输出噪声需要进行强化测试。

2 伺服控制电路性能测试

伺服控制电路的性能测试决定电路是否能够满足原子钟的使用要求,主要对AD 量化噪声、DDS频率综合电路以及两路数模转换DA 输出通道噪声抑制水平进行测试。

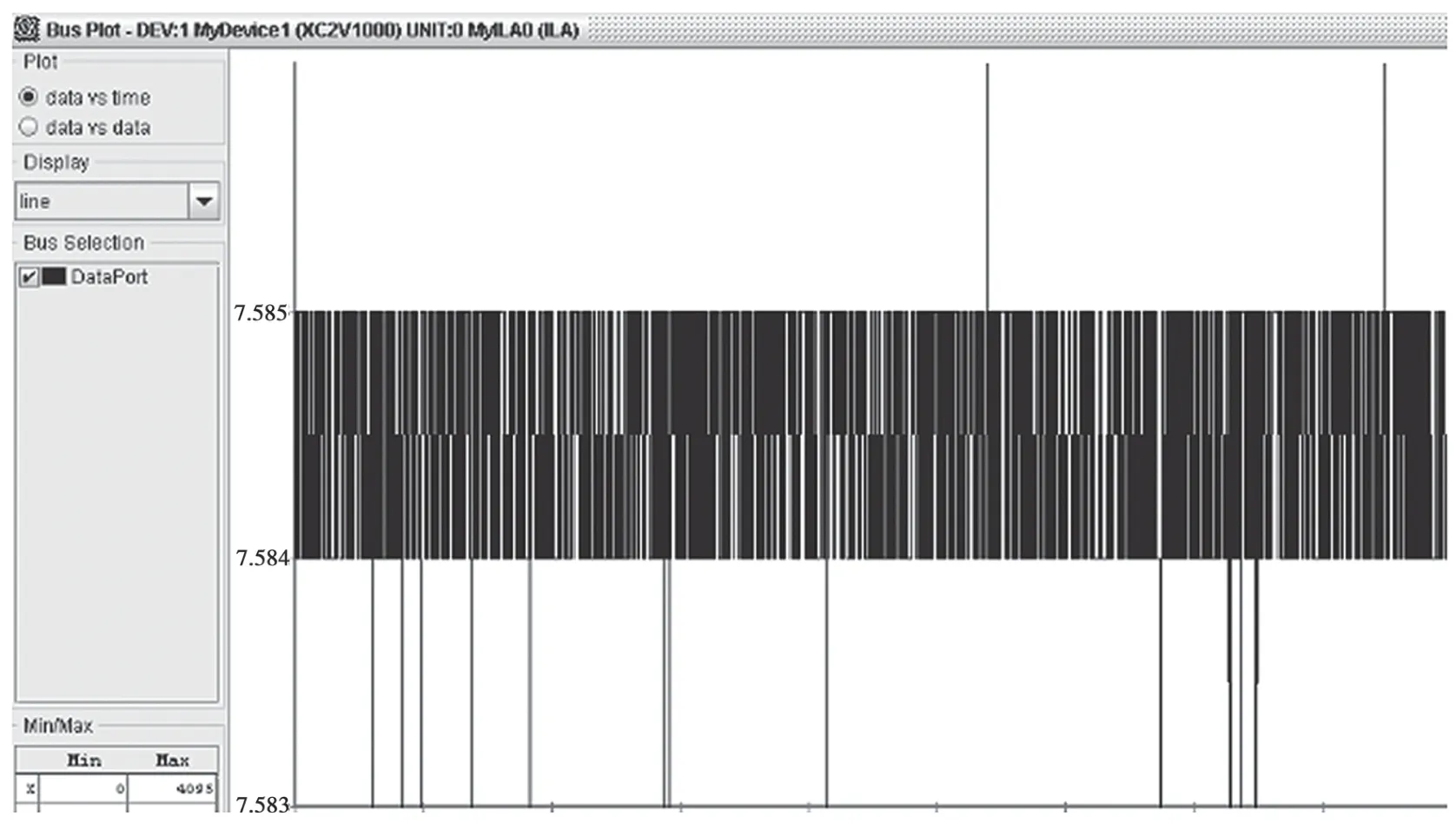

2.1 AD 量化噪声测试

伺服控制平台采用的是14bit 低速率的模数转换器B9243,芯片采样频率3MHz,输入噪声0.36LSB,SFDR 达到91dB。工作时其采集如图4 所示的误差合并电路输出信号error_out。而误差信号采集电路的数字量化噪声性能水平与原子钟的最终输出指标有着直接的关联。

测试AD 电路量化底部噪声性能,将error_out端口接至50Ω 负载,保持FPGA 的gtag 口处于正常连通状态,通过chipscope 功能模块采集AD 量化底部噪声,实际采集结果如图5 所示,结果显示,AD 量化噪声水平能够控制在4LSB 以内。

图5 AD 量化噪声采样图

2.2 DDS 频率综合电路的测试

DDS 频率综合电路通过FPGA 结合verilog HDL硬件描述语言对DDS 专用芯片频率寄存器以及相位寄存器进行配置,监测电路输出是否能够满足功能。根据图2 所示的时序图,DDS 频率合成电路输出信号的最小周期为2×40ms=80ms,fmin=12.5Hz。写时钟信号WRB 为FPGA 提供的120MHz。

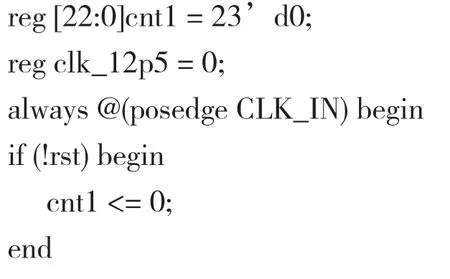

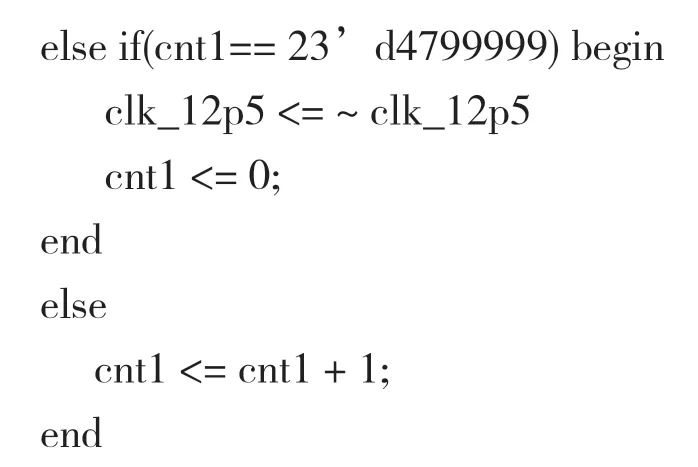

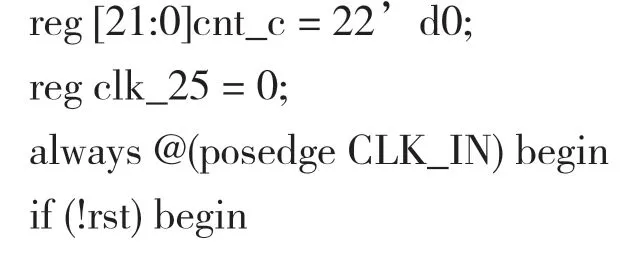

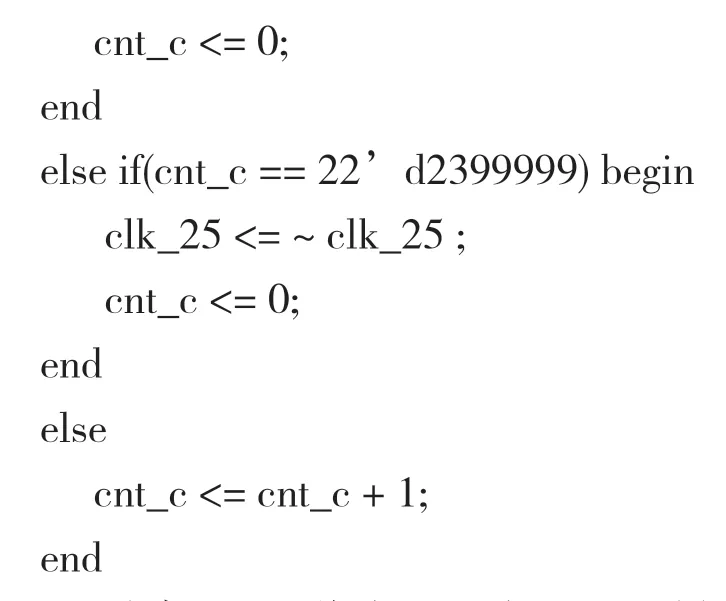

对系统时钟CLK_IN 进行分频处理,将120MHz信号分频至12.5Hz,实现最小80ms 的周期时钟clk_12p5,具体实现如下所示。

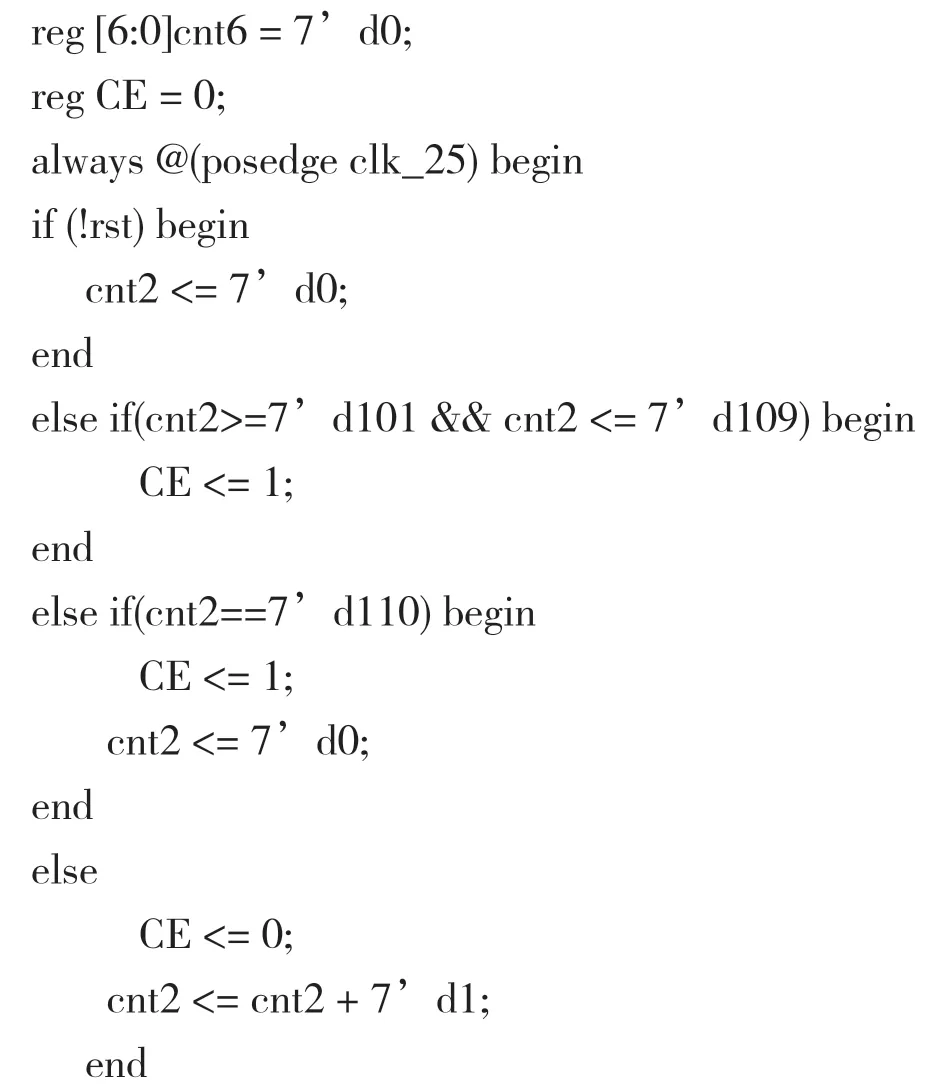

同时将系统时钟120MHz 分频至25Hz 作为下个使能产生时钟,即用来计算一个周期内40ms 宽度的个数,也作为t1、t2 及t3、t4 的配置时钟,具体实现如下所示。

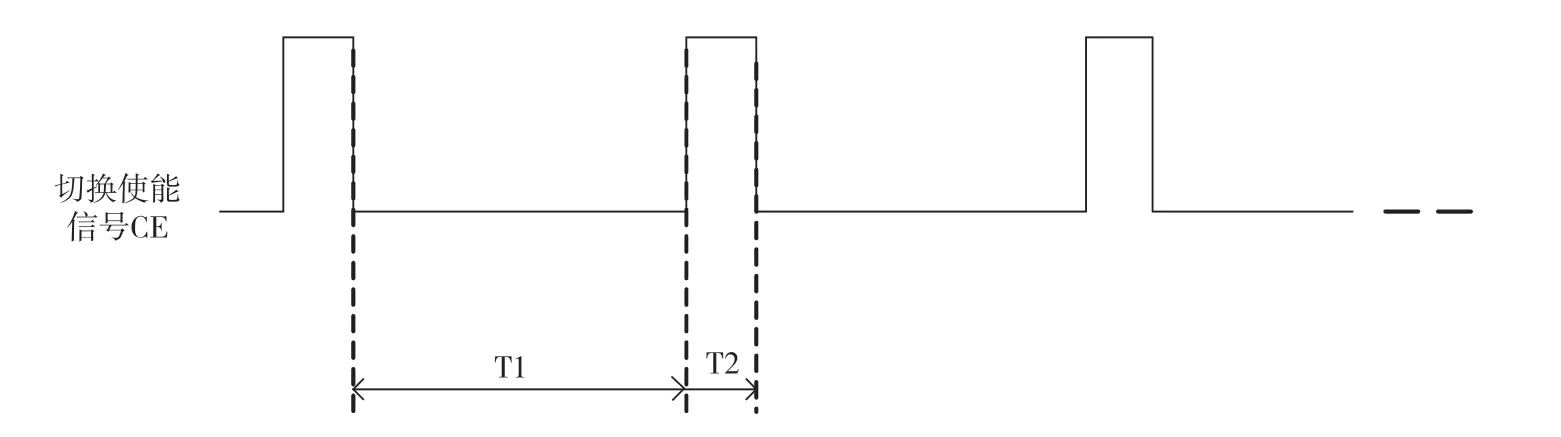

T1 时序4.04s 共有101 个40ms 时间间隔,T2时序400ms 共有10 个40ms 时间间隔,一个完整的探测周期共有111 个40ms 时间宽度,即111 个CLK_25 时钟周期。定义T1 和T2 的切换使能CE,CE 为低电平时输出T1 时序信号,CE 为高电平时,输出T2 时序信号,关系如图6 所示。

图6 切换使能信号CE 时序控制图

具体实现如下所示。

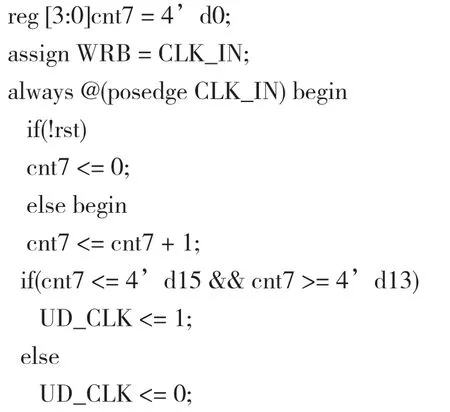

DDS 芯片GMD9852A 更新时钟端口IO_UPDATE 用于同步外部串口或并口配置,是外部串口或并口时钟与内部系统时钟的握手信号。每次通过串口或并口配置完成后,为了使配置的寄存器生效,需要一个io_update 上升沿,更新时钟有两种方式,一种是内部更新,另一种是外部更新。本方法采用的是外部更新,是通过IO_UPDATE 管脚输入更新时钟,更新时钟高电平需大于两个系统时钟周期,配置方法实现如下。

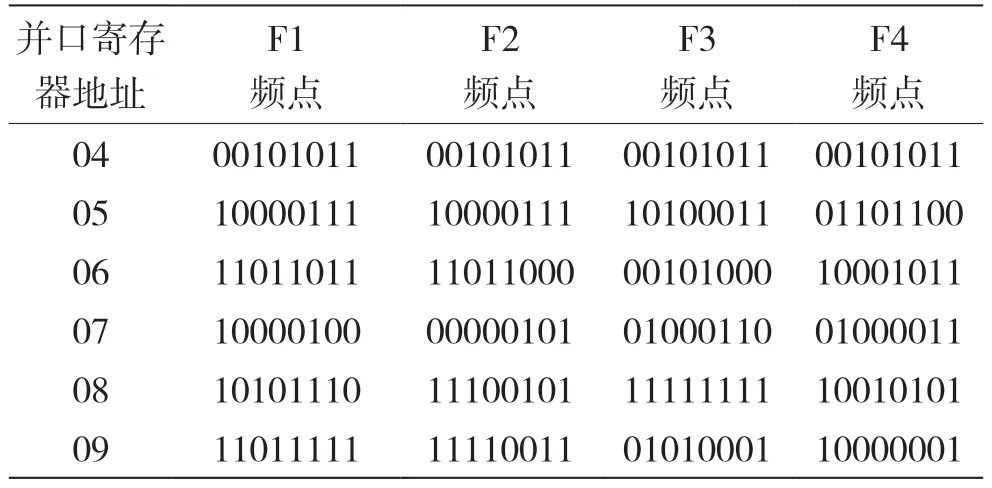

在T1 及T2 的t1,t2,t3,t4 时序段,对相应的GMD9852A 的并口地址寄存器进行配置,实现F1,F2,F3,F4 频点的输出。分别对04(Frequency Tuning Word 1<47:40>),05(Frequency Tuning Word 1<39:32>),06(Frequency Tuning Word 1 <31:24 >),07(Frequency Tuning Word1<23:16>),08(Frequency Tuning Word 1<15:8>),09(Frequency Tuning Word 1<7:0>)并口寄存器进行配置DDS_DATA。不同时序下的配置关系如表1 所示。

表1 并口寄存器配置表

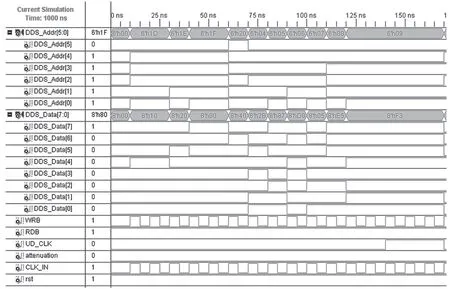

通过对test 文件的编译仿真,结果如图7 所示,与预期结果相符。

2.3 DA 输出通道噪声测试

伺服控制电路的DA 输出通道包括微波腔控制支路以及晶振支路两路电路,均由数模转换电路以及比例运放电路构成。其中晶振支路的噪声水平对原子钟有着更加重要的影响。B9764 是一种14 位电流输出型、CMOS D/A 转换器,最大刷新率可达120MSPS(Million Samples per Second),满量程输出电流可调整范围为2mA~20mA。

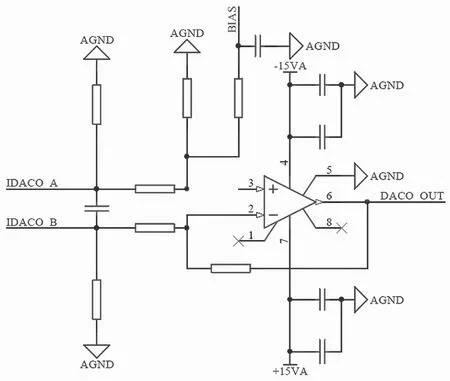

如图8 所示,B9764 输出采用差分输出的方式,通过IOUTA 以及IOUTB 端口输出,此输出方式可以有效抑制最终输出DACO_OUT的共模噪声分量。

图7 DDS 模块配置仿真图

图8 数模转换原理图

图9 运放比例放大原理图

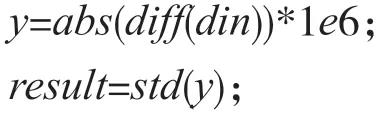

如图9 所示,DACO_OUT 输出电压最大范围为0~5V,在此范围内,以1V 为最小步进调整最终输出电压,高精度万用表1s 为间隔分别采集该电压500 点数据,通过MATLAB 计算出该组数据的标准方差,前后电压数据的标准偏差需要控制在合理的范围内,即大部分落在平均值附近。MATLAB 计算方法中,din为采集数据数组,result为计算得出的标准偏差。

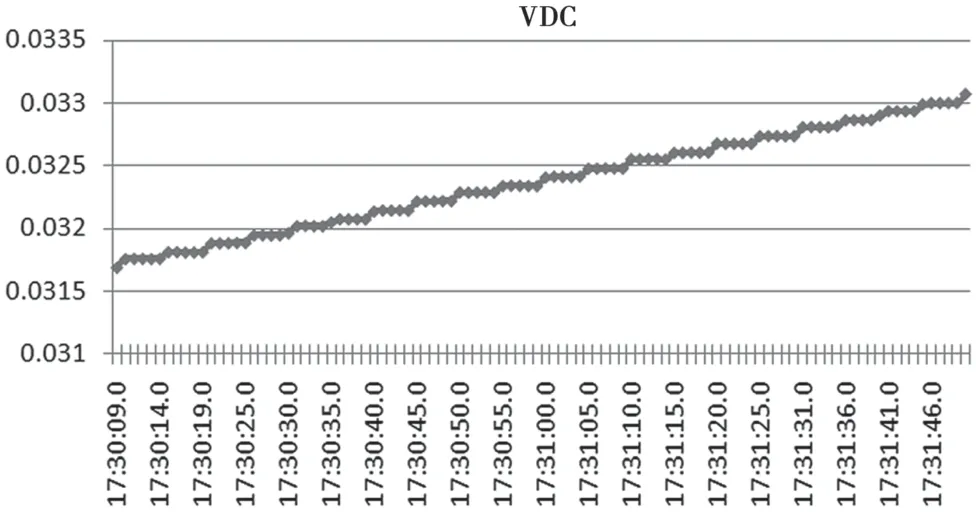

除了上述对标准偏差的测试,另外对14bit 的数模转换器比例运放电路输出进行台阶电压均匀度测试。从全零开始,每隔5 秒钟DA 输出加1 个LSB,从全0 至全1 结束。通过高精度电压采集设备采集输出端口电压DACO_OUT,截取其中30000点数据,判断台阶电压是否变化均匀且控制在合理区间范围内。

设置DA 翻转后的台阶高度的上下阈值分别为sum_min 及sum_max,落在此阈值范围中间的为sum_ave,高于sum_max 的台阶数量设为cnt_mid,低于sum_min 的台阶数量设为cnt_min,中间值的台阶数量为cnt_ave。上述台阶高度的平均值分别为ave_max,ave_min 以及ave_mid,变量计算公式如下所示。设置ave_mid的1.5 倍值为判断准则,与ave_max-ave_min 作比较,上述差值应该小于台阶平均高度的1.5 倍,DA 输出全0 至全1 整个范围内不应该有明显的上下异常突跳。计算均可在MATLAB 中完成。

对DACO_OUT 的台阶电平测试截取了一小段测试示意图,如图10 所示。待一轮台阶测试完成后,将截取的30000 个数据的数组送入MATLAB 进行计算,将ave_max-ave_min 与1.5 倍的ave_mid的结果进行比较,判断DA 输出电路的台阶均匀度水平。

图10 DA 台阶电压采集示意图

3 结语

本文介绍了一种原子钟用的伺服控制电路的控制及测试方法,主要通过软硬件结合的方式,对电路的功能以及噪声性能进行摸底测试,测试数据用来判断是否满足原子钟的使用要求。该测试方法不仅适用于原子钟类产品,同样适用于类似的低噪声控制系统。