脉冲信号占空比测量电路的设计与Proteus仿真

2020-12-22杨丰亮

杨丰亮

(1.闽南师范大学物理与信息工程学院,福建漳州363000;2.电子信息工程专业实验教学中心,福建漳州363000)

国际工程教育专业认证体系强调培养学生的工程实践能力和创新能力[1-5],电子技术的设计实践是非常有效的培养方式.电子电路设计是电子、电气、通信等专业重要的综合实践教学环节,实践内容丰富.经历了查阅资料、方案设计、电路设计、安装调试、指标测试、撰写报告、交流答辩的整个实践环节后,学生巩固和加深了对理论知识的理解,初步掌握了电路设计方法、体验了电路设计项目的工程实现过程,提高了专业兴趣和创新能力,为以后从事电子设计、产品研发奠定了基础.

近年来,应用现代辅助工程设计工具,如Proteus、Multisim 等EDA 软件,结合电子技术、单片机原理、嵌入式系统等进行电路设计,可有效降低设计难度、提高设计效率、减少设计工作量、减少元器件损耗,是电子、电气等相关专业实践教学改革的主流[6-10].

脉冲占空比是脉冲电路的重要参数,快速准确地测得脉冲占空比是电子测量中一项重要的工作,也是电子技术设计的一个重要选题.本文基于Proteus仿真平台,以脉冲占空比测量及显示系统设计为例,介绍数字电子技术设计实践案例,在工程教育专业认证背景下探索电子信息类专业课程设计的实践教学改革.

1 Proteus仿真在电子电路设计中的应用

仿真软件Proteus 是业内最完善、最优秀的EDA 工具软件之一.其性能卓越、功能强大,集原理图设计、仿真及印刷电路板设计等多项功能于一身,不仅能对模拟电路、数字电路进行设计、分析,还能对各种嵌入式处理器如51单片机、AVR单片机、ARM、DSP等进行设计和仿真,成为了电子系统综合设计不可或缺的基本工具.Proteus软件能够提高电子产品的开发效率、降低开发成本,有友好的交互式工作介面、丰富的虚拟仪器和逼真的运行效果,因而在产品研发、工程教育等方面被广泛应用.

以项目为导向,将Proteus仿真应用到数字电路设计中非常必要,以下3点特别突出.

1)提高设计效率,节约设计时间.传统的数字电子技术课程设计方式,直接采用实物方式构建电路,进行设计验证,电路布线繁复、工作量大,容易出错,学生很难在有限的教学时间里完成设计任务.Proteus仿真软件功能非常强大,可以快速绘制电路原理图、选择元器件参数,使用丰富的虚拟仪器、探针对电路进行功能测试,修改电路或调整参数,直至达到设计指标.完成电路的理论设计与虚拟验证后,再做实物电路验证设计方案,极大提升设计效率.

2)实验场所、器材、设备等资源得到有效充分利用.借助Proteus软件平台,电路的理论设计与虚拟验证可以在实验室之外的任何学习场所完成,通过仿真得到虚拟验证的设计方案才到实验室进行实证,极大地提高实证工作效率,减少器件损耗,提高设备、场所使用率.

3)可有效地提升学生的自信心和工程创新能力.Proteus仿真软件的应用,提高了电路设计的效率和成功率,可充分调动学生的热情和自觉性.完成预定的电路设计任务后,优秀的学生可继续在仿真平台上进行设计方案优化,对不同设计方案的比较研究,增加电子电路设计的趣味性,利于培养学生的探究意识和工程创新能力.

2 基于Proteus仿真的数字电路设计案例——脉冲占空比测量

2.1 设计任务和要求

采用通用数字集成电路设计的脉冲占空比测量显示电路,具体要求如下:

1)被测信号为矩形脉冲,脉冲电压幅值:3~5 V,频率范围:10~5 000 Hz,占空比范围:1%~99%.

2)占空比测量电路的量程为1%~99%,显示分辨率1%,测量绝对误差不大于1%.

3)测量值用数码管显示,显示更新率合适,不能出现数码快速跳动,影响读数.

2.2 设计方案

2.2.1 设计方案对比

文献[11]针对PWM电路调节输出电压占空比的脉冲电源设计了一种简单实用的占空比测量电路,脉冲占空比测量值由外置数字电压表显示.文献[12]设计了一种利用可调频率振荡电路校准,基于电子计数的数显脉冲信号占空比的测量电路,适用于测量精度不高的场合.文献[13-14]分别以单片机和DSP 芯片为核心,使用高速A/D 转换器将预处理后的待测信号转换为数字信号,再由算法求出信号频率和占空比,该方法对单片机(或DSP)和转换器性能要求较高,且要软硬件配合,成本较高.文献[15]运用FPGA 的锁相环倍频功能,将信号频率提升至很高的倍率,从而达到能够精确测量脉冲信号参数的目的.文献[13-15]的占空比测量方法超出了数字电子技术课程教学范围,不适合作为数字电路课程设计课题.本设计采用锁相环倍频技术,应用通用CMOS 锁相环集成芯片74HCT4046,用少量的数字集成电路实现脉冲信号占空比的测量与数字显示,精度较高且成本较低,适合低频脉冲信号的测量,是综合性能较高的实现方案,适合作为数字电路课程设计课题.

本案例是在仿真软件Proteus的平台上,采用锁相和倍频相结合的技术,运用数字集成电路,设计出的脉冲占空比测量电路,仿真结果如图1所示,电路工作原理如下.

2.2.2 设计思路

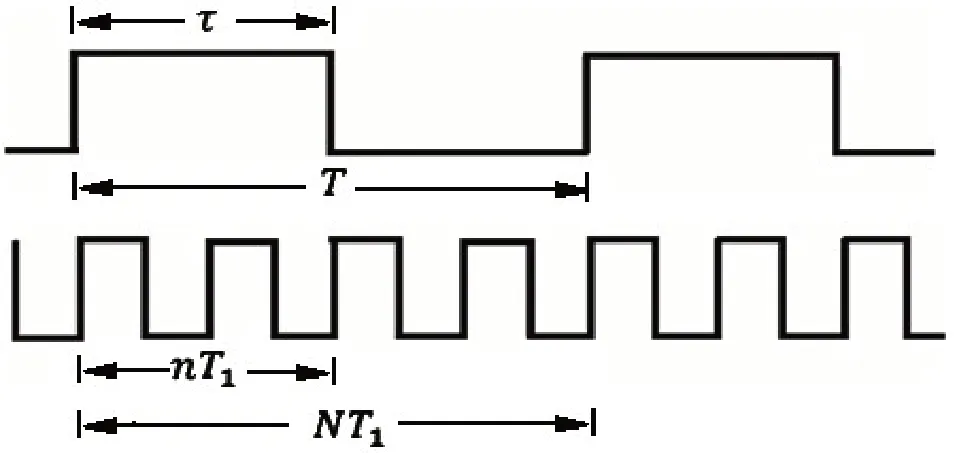

脉冲占空比D定义为脉冲宽度τ与脉冲周期T的百分比,即D/%=τ/T.如图2所示,若在输入信号的一个周期T内把信号进行N等分(N倍频),即T=NT1,脉冲宽度τ=nT1, 则占空比可表示为当N= 100 时(即输入信号100倍频),待测脉冲信号的占空比即为n%.

图2 脉冲占空比测量原理Fig.2 Measurement principle of pulse duty cycle

2.2.3 系统框图

系统构成原理图如图3所示,电路由锁相环、100 进制加法计数器、定时触发电路、锁存器、译码驱动和数码显示等电路组成.

图3 系统构成原理图Fig.3 Schematic diagram of system composition

锁相环和100分频器组成锁相倍频电路,实现对待测信号的100倍频.在待测信号的低电平期间,脉冲计数器复位;在待测信号的高电平期间,脉冲计数器对100倍频信号进行计数;在待测信号下降沿时,定时触发电路输出锁存脉冲,脉冲上升沿时将计数器的计数值锁存,再经译码驱动将该锁存值由数码管显示.

2.3 模块电路基本原理

脉冲占空比测量电路由四个功能模块构成,运用模块式设计,便于仿真与功能测试.

2.3.1 锁相倍频电路

能够对两个电信号进行相位同步的闭环控制系统称为锁相环.锁相倍频电路原理如图4所示,当锁相环实现相位锁定时,在某一频率范围内压控振荡器输出信号的100分频信号会锁定输入信号频率,并自动跟随输入信号的变化,因此压控振荡器输出信号频率就是输入信号的100 倍频,且跟随输入频率变化,二者严格保持一致.

图4 锁相倍频电路原理图Fig.4 Principle of phase-locked frequency circuit

74HCT4046是通用CMOS锁相环集成电路,与74LS系列电平兼容,74HCT4046构成的锁相倍频电路如图5所示,4脚输出为100倍频信号.

74LS90是二-五-十进制计数器,用于构成100分频电路.使能端功能如下:

1)当R0(1)=R0(2)= 1,R9(1)或R9(2)= 0时,计数器清零,电路状态与CK无关.

2)当R9(1)=R9(2)= 1时,计数器置9.

3)当R0(1)或R0(2)= 0时,计数器计数,CK下降沿有效.

由74LS90 构成的100 分频电路如图5左部分电路所示,IC1与IC2级联,IC1的Q3 输出信号构成IC2的CKA 输入信号.74LS90 的Q0 为CKA 输入信号的二分频,Q3 为CKB 的5 分频,如图把Q0 与CKB 连结,即IC1的Q3 输出信号为本级CKA 输入信号的10 分频.同理,IC2的Q3 输出信号为本级CKA 输入信号的10分频,故IC2的Q3输出信号为IC1的CKA输入信号的100分频.

图5 74LS90构成的100分频电路与74HCT4046构成的锁相倍频电路Fig.5 100 Frequency divider circuit and phase-locked frequency doubling circuit

2.3.2 脉冲计数电路

脉冲计数电路由两片74LS90 级联,构成一个BCD 码格式的一百进制加法计数器,输出为BCD 码00~99.电路如图6所示.

图6 74LS90构成100进制计数器电路Fig.6 100 decimal counter circuit(constituted by 74LS90)

计数器在输入信号vin(t)上升沿到来时,开始对锁相倍频输出的100 倍频脉冲信号进行计数.当输入信号vin(t)的下降沿到来时停止计数.由于74LS90 芯片在R0(1)、R0(2)均为低电平时计数,R0(1)、R0(2)为高电平时计数清零.因此,将输入信号vin(t)经反相后作为两片74LS90的R0(1)、R0(2)控制信号.

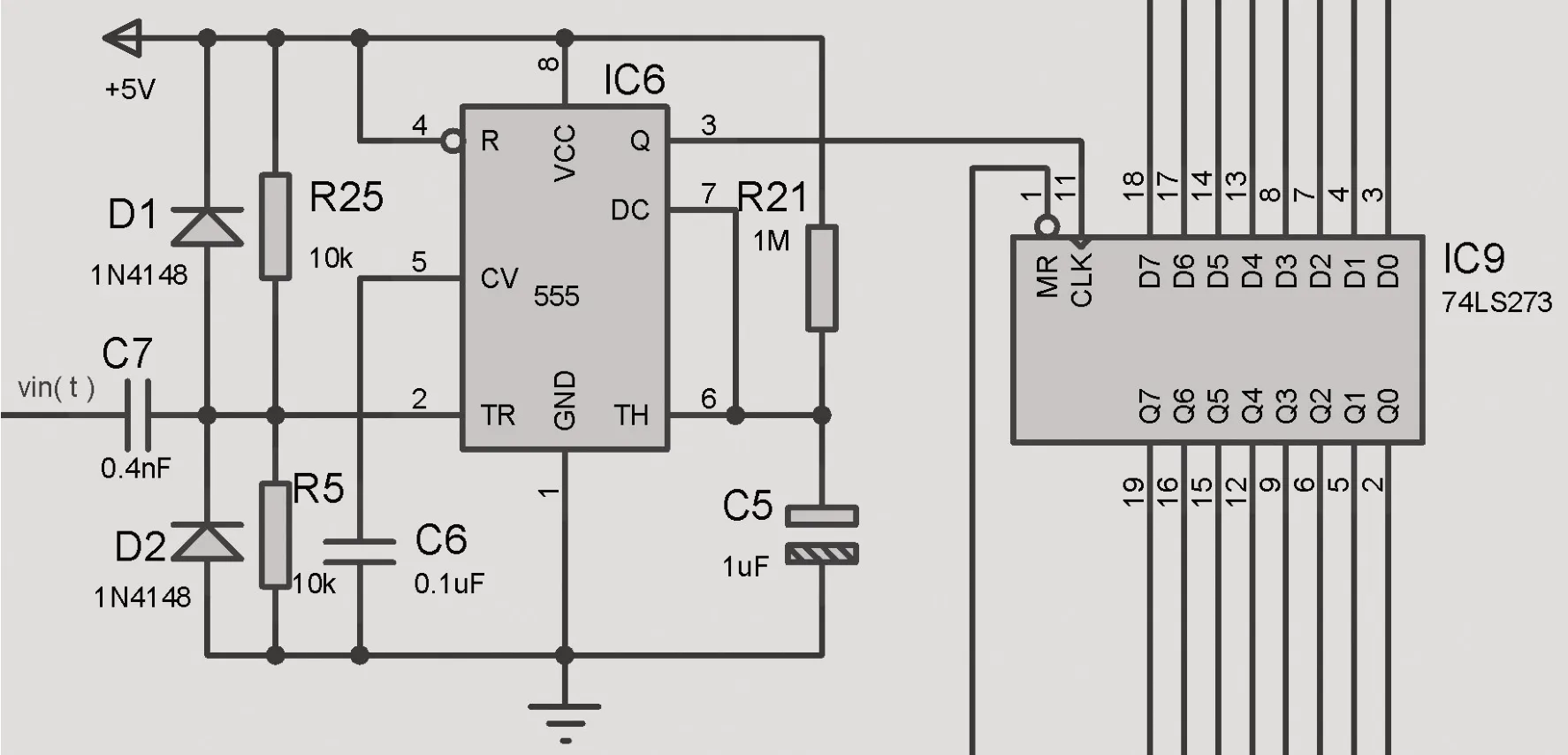

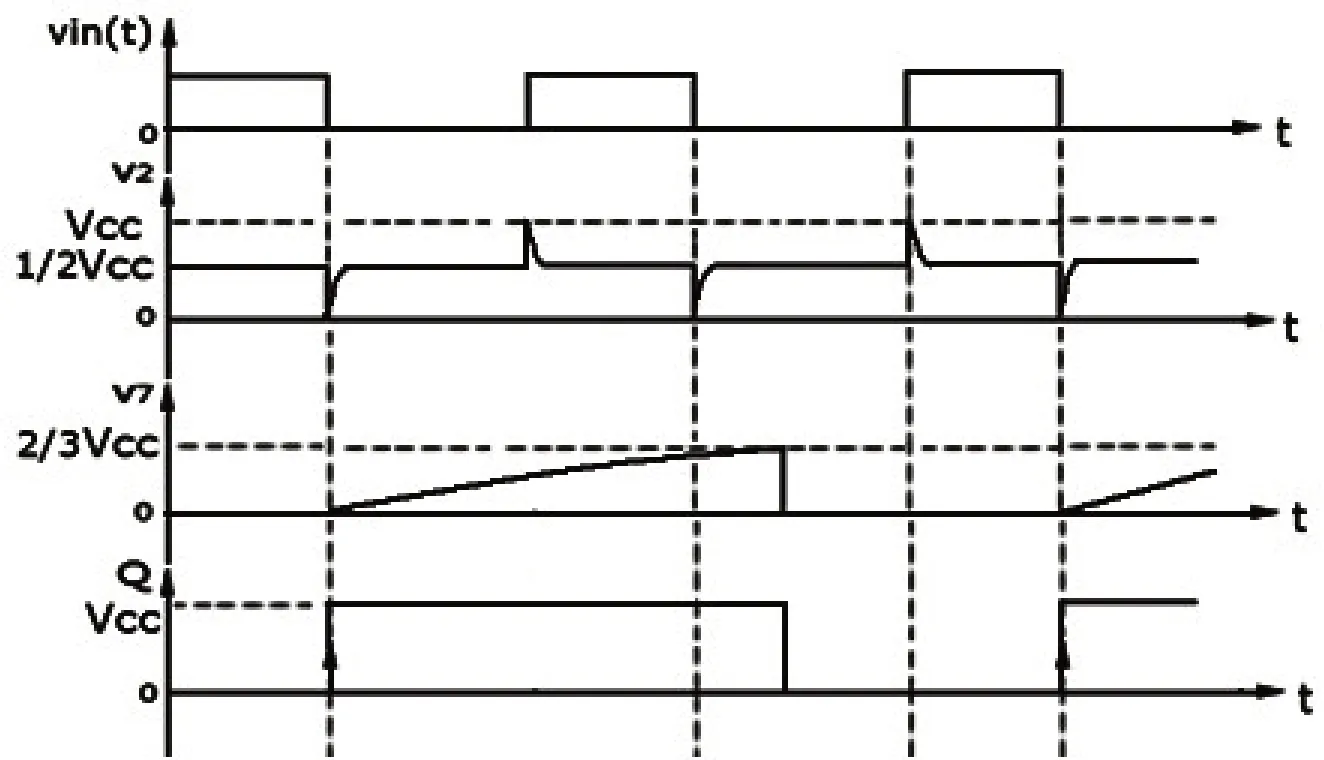

2.3.3 定时触发、锁存电路

定时触发、锁存电路如图7所示.由555时基芯片组成单稳态电路,无触发信号时工作在稳态,输出低电平,电容C5放电.当vin(t)下降沿时,电路被触发,跳转至暂稳态,输出高电平,电容C5充电,当其电压升至2VCC/3时,暂稳态结束,回到稳态,直至vin(t)下一个下降沿.555时基芯片的输出Q连接74LS273锁存器CLK端,当vin(t)下降沿(锁存器CLK上升沿)时,锁存器锁存计数器的计数值,并送译码显示.为保证数码管显示的数值不出现抖动现象,数码显示刷新时间可大约设为1 s,而555 时基芯片的暂态时间为TP=(ln 3)R21C5≈1.1R21C5,所以取R21= 1 MΩ,C5= 1 μF.定时触发、锁存工作波形如图8所示.

图7 定时触发、锁存电路Fig.7 Timing triggering and latching circuit

图8 555单稳态电路工作波形Fig.8 Working waveform of 555 timer monostable circuit

2.3.4 译码、驱动、显示电路

译码、驱动显示电路如图9所示,译码器可以选用74LS248 或CD4511.译码器将输入信号vin(t)下降沿锁存的脉冲计数值译码后由数码管显示,该显示值即为输入信号vin(t)的占空比.

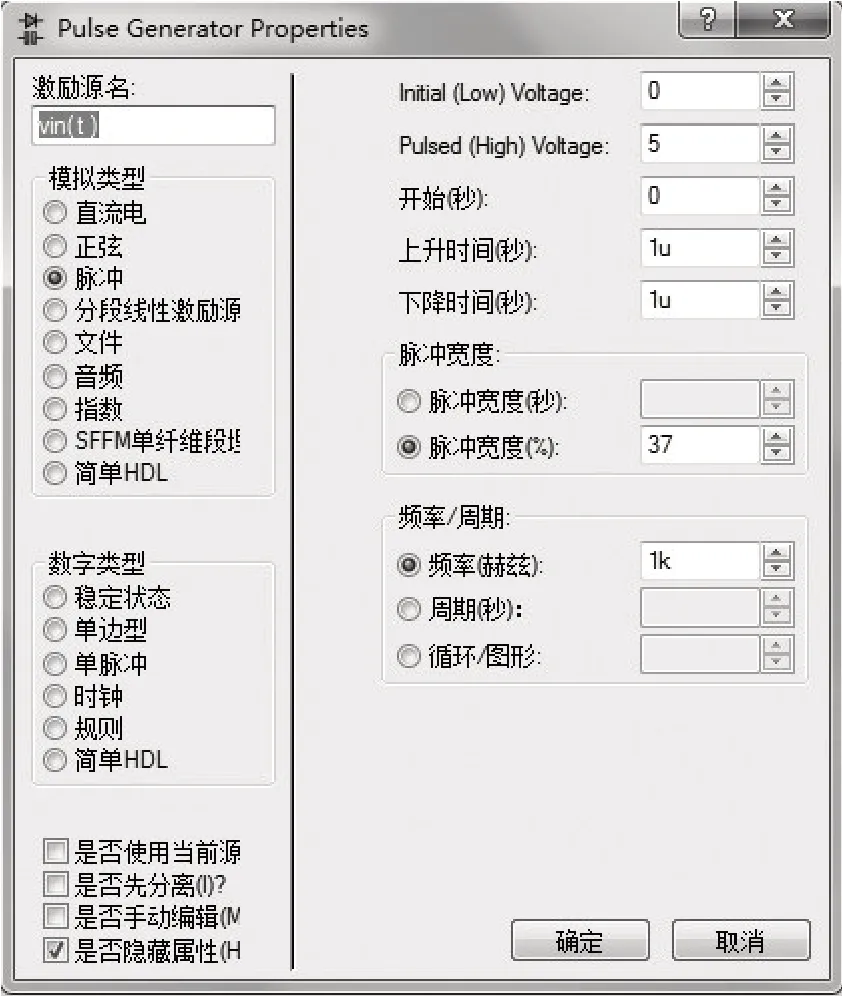

2.4 脉冲占空比测量的Proteus仿真示例

脉冲占空比测量的设计电路及仿真结果如图1所示,输入信号的参数设置如图10所示.设定输入信号频率为1 K、占空比为37%的脉冲信号vin()t进行检验,仿真结果准确.如图10改变输入脉冲频率和占空比参数,测试的结果为:脉冲占空比的测量设计电路对频率范围为10~6 300 Hz 的脉冲信号测量的绝对误差在1%以内,且占空比的测量量程符合1%~99%的要求.

图9 译码、驱动、显示电路Fig.9 Decoding,driving and displaying circuits

图10 脉冲信号参数设置Fig.10 Pulse signal parameter setting

2.5 设计方案的实物电路验证

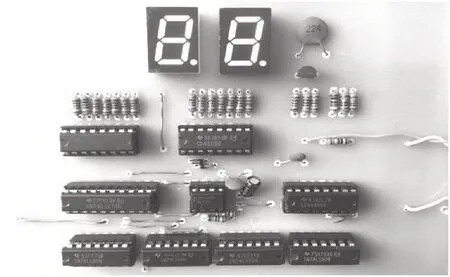

图1所示电路为Proteus仿真成功的脉冲信号占空比测量电路设计方案,以该原理图制作实物电路如图11所示,实际测量结果符合预期要求,设计方案得到实证.

图11 脉冲占空比测量电路Fig.11 Pulse duty cycle measurement circuit

3 总结

国际工程教育专业认证体系要求提高学生综合创新能力和工程设计能力,因此,电子、电气等相关专业的学生必须加强综合性设计实践.本脉冲占空比测量电路的设计方案契合数字电子技术的实践特点,各个功能模块原理清晰,在设计过程中应用了Proteus仿真技术,取得了优秀的设计实践成果.学生应用仿真软件在电子电路设计上不断地成功实践,综合设计能力显著提高,这是在工程教育专业认证背景下教学改革的良好实践.Proteus软件在设计实践中有非常优秀的表现,在网络学习上也是强有力的仿真辅助工具,掌握了仿真软件,对学生今后的专业学习和专业设计都有很大的助益.