一种提高FPGA片间通信稳定性的校验协议研究

2020-12-14池林辉钱芸生籍宇豪

池林辉,钱芸生,籍宇豪

一种提高FPGA片间通信稳定性的校验协议研究

池林辉,钱芸生,籍宇豪

(南京理工大学,江苏 南京 210094)

随着FPGA(Field Programmable Gate Array)在大型系统中得到越来越广泛的应用,单片FPGA往往难以胜任全部工作,多片FPGA之间进行高速稳定通信成为了该领域的一个研究热点。为此设计了一种基于低压差分信号(low voltage differential signal,LVDS)可用于FPGA片间高速稳定通信的校验协议,该协议在常规LVDS通信的基础上进行多轮多路校验,以提高传输可靠性。基于该协议,搭建了一套由两片Xilinx 7系列FPGA构成的9通道LVDS通信测试系统。其中1个通道用于同步时钟,另外8通道用于校验和通信。经过长时间高低温测试,在保证单路传输速率达1.2Gb/s的情况下,相对于常规LVDS通信,误码率大大降低。

FPGA;LVDS;通信测试;校验协议;高速稳定;误码率

0 引言

对于一些复杂的系统,由于功能或机构的限制,单片FPGA难以实现全部功能[1]。在多片FPGA协同工作情况下,如何提高FPGA片间高速通信的稳定性逐渐成为这一领域的研究热点。传统的并行总线因占用资源多,噪声高等缺点,在高速数据传输领域已逐渐被淘汰。目前对于Xilinx 7系列FPGA而言,片间高速通信主要有两种方案。一种是通过GT系列串行高速收发器来实现,根据FPGA种类不同分为GTP、GTX、GTH、GTZ。其中线速率最低的GTP可以支持6.6Gb/s。虽然此方案传输速率高,但由于每片FPGA的串行高速收发器数量有限,且高速传输对于PCB布局布线提出了很高的要求,因此存在一定的局限性。另一种方案是通过LVDS技术来实现[2]。该技术具有线速率高、抑制共模噪声、低功耗、抗干扰能力强等优点[3]。且通过配置BANK电压,可使FPGA提供大量支持LVDS标准的接口,吞吐率可达Gb/s级,因此该方案具有更加广阔的应用前景[4]。

本文提出了一种提高LVDS通信稳定性的校验协议,基于两片Xilinx FPGA平台搭建多路LVDS通信测试系统,并在不同温度条件下测试系统的误码率[5]。

1 FPGA片间通信系统搭建

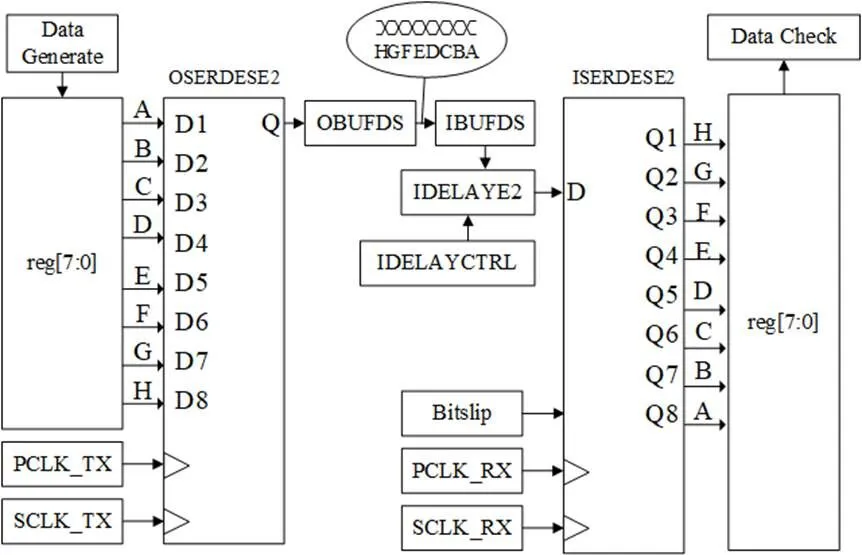

本文分别利用两片Xilinx公司的Kintex-7和Artix-7 FPGA作为数据处理中心,通过9对LVDS信号线进行片间通信,如图1所示。

图1 片间通信测试系统组成框图

程序测试主要分3步。第一步通过图1中的Clock Channel进行同步时钟,其中涉及到差分信号和单端信号的转换以及时钟分频倍频;第二步通过Data Channel进行双向数据校验,其中涉及到串并转换、bit位对齐、Byte位对齐、通道对齐。因为每个通道经过串并转换都可以收发8bit数据,共有8个数据通道,所以Data Channel是64bit;最后进行单向数据传输,测试系统误码率。

系统硬件包括3部分,分别是K7 FPGA核心板、通信底板、A7 FPGA核心板。硬件测试平台实物如图2所示。为了保证片间通信的稳定性,在绘制PCB时,布线方面要保证9组数据通道等长,且使用圆弧走线;在布局方面,要避开电源等强电磁干扰,且保证对应IO口间距尽量短。

2 数据校验协议设计与试验

2.1 同步时钟

两片FPGA的主时钟属于非同源时钟,存在一定的相位差,因此在数据校验和通信之前,必须先进行同步时钟。

同步时钟包括发送和接受两部分。首先要通过K7的MMCM(mixed-mod clock manager)IP核分频生成20MHz的同步时钟,然后经过OBUFDS转换成差分时钟输出[6]。同步时钟的作用只是对齐两片FPGA时钟的相位,因此频率无需过高,这有利于提高片间传输的稳定性。

图2 硬件测试平台

如图3所示,LVDS信号电平标准为2.5V,周期为50ns[7]。因此在硬件方面,需要在试验开始前更改FPGA对应BANK的供电电压,以改变FPGA IO口的电平标准;在程序方面,需要通过XDC文件配置输出IO口模式为LVDS_25模式。

图3 差分信号波形图

该差分信号需经过电磁环境复杂的底板传输后才能到达A7,如果时钟频率过高,PCB的布局布线不能满足高速信号的严格要求,就会导致误码。这也说明了采用多路LVDS信号传输比少量GT高速串行收发器传输的可靠性和适应性更好。

A7 FPGA接收到差分时钟后,首先利用IBUFDS对输入信号进行输入缓冲和差分转单端处理,以去除共模噪声的影响[8]。该时钟将作为接收端的系统主时钟使用,因此还需进入BUFG进行全局缓冲。然后利用MMCM对20MHz的同步时钟进行倍频,得到600MHz的串行时钟SCLK和150MHz的并行时钟PCLK,完成同步时钟。这里需要注意的是FPGA接收时钟信号时,必须将引脚分配到MRCC(区域时钟的BUFIO,能驱动相邻BANK/时钟域的IO)或SRCC(区域时钟的BUFIO,能驱动所属BANK/时钟域的IO)的I/O口上才可以作为接收端主时钟使用[9]。

2.2 数据校验

2.2.1 通信原理

两片FPGA之间通信是双向的,各通道数据收发原理相同,如图4所示。

图4 通信原理框图

首先由发送端生成8bit测试数据,然后经过DDR(Double Data Rate)模式的OSERDESE2(并串转换器)把并行数据转成串行数据,最后用OBUFDS把单端信号转成差分信号输出[10]。这里需要给OSERDESE2提供并行时钟PCLK_TX和串行时钟SCLK_TX,这两个时钟分别接CLKDIV和CLK端口[11]。

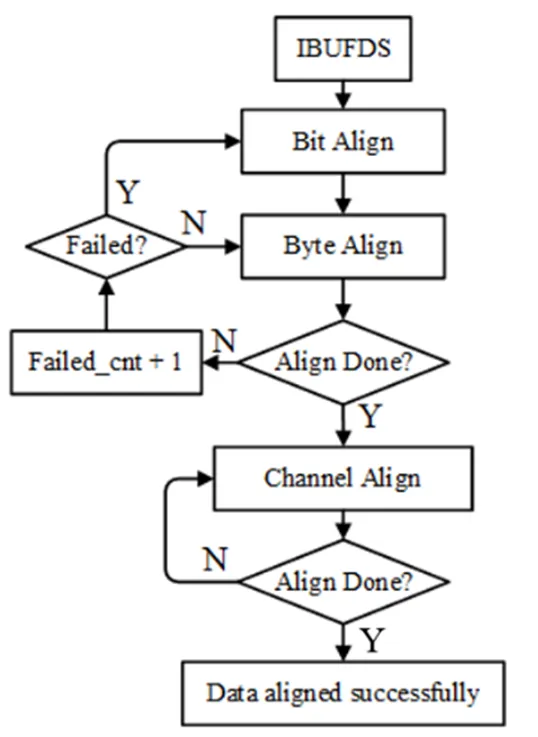

差分信号经过底板传输后,由另一片FPGA的IBUFDS接收,并把差分信号转成单端信号。数据经过转换后需要进行三步对齐,如图5所示。

图5 数据对齐流程图

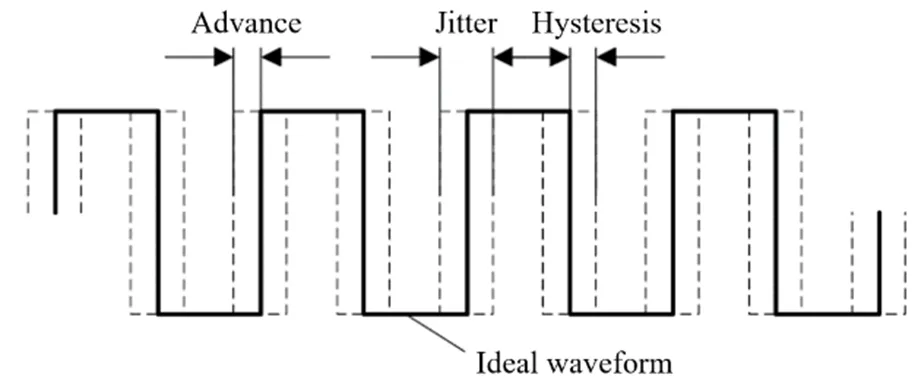

首先通过IDELAYE2进行bit位对齐,然后通过ISERDESE2进行串并转换和Byte位对齐,最后进行通道对齐,直至还原出各通道的8bit测试数据。在LVDS信号传输过程中,虽然可以消除共模噪声,但数字信号的抖动无法避免,如图6所示。

从频域的角度分析,抖动频谱的中心就是信号的工作频率,其符合高斯分布。不是中心频率的信号,被称为相位噪声。抖动和相位噪声本质相同,分别是时域和频域分析的结果。

图6 信号在时间域抖动特性

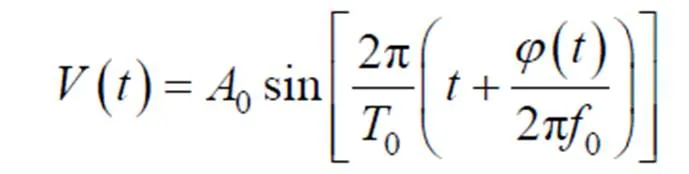

正弦波输出信号可以用如下公式表示:

()=[0+()]sin[2p0+()] (1)

式中:0为电压最大值;()为振幅噪声;0为工作频率;()为相位噪声。在理想情况下,()和()均为0。但振荡器并不理想,相位噪声不能忽略。因此得到下面公式:

当=2p,则sin()=0,此时公式(2)可以表示为:

所以抖动与周期的关系可以通过如下公式表示:

因此频率越高,抖动越大。当利用时钟信号采集串行数据时,就可能出现亚稳态。所以对串行数据进行相位调节是必要的。

另外在PCB布线时会出现数据线之间不等长的情况,或受外界温度变化的影响,从而在接收端产生相位差。因此无法准确地根据接收端的时钟沿采集到正确的串行数据。

本文采用IDELAYE2对串行数据进行相位调节,实现bit位对齐,以防止亚稳态的发生,保证采集到正确的bit,如图7所示。

图7 Bit位对齐时序图

图7中DDR Clock为接收端倍频后的串行时钟。因为采用DDR模式,因此串行时钟的每个跳边沿都应该和一个串行数据对齐。IDELAYE2可以不断调整串行数据的相位,最终使时钟跳变沿刚好对齐数据中心。

调整过程主要包括两个环节。首先向右不断调整IDELAYE2的tap值,使其出现tap1的情况。一旦出现此情况,则说明发生了亚稳态,这将导致后续Byte位对齐失败,记录此时的延迟值tap1;然后向左对数据通道不断调整,直至出现tap5的情况,此时再次出现Byte位对齐失败,记录此时的延时值tap5。最后取tap1和tap5的中值,即tap3作为该数据通道的最理想延时值,进而完成bit位对齐。时钟沿和数据通道中心对齐将会保证采集到最稳定的数据。

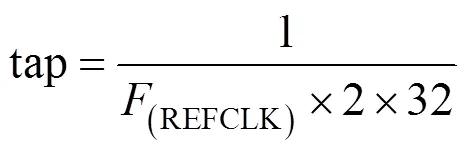

此处注意IDELAYE2需要IDELAYCTRL提供延时分辨率[12]。因为给IDELAYCTRL的参考时钟REFCLK是200MHz,根据如下公式可得IDELAYE2的延时分辨率为78.125ps:

式中:(REFCLK)为参考时钟的频率;tap为调节延迟分辨率。其中参考时钟需要由同步时钟倍频而来,以保证时钟同源。一共有32个调节梯度可以选择,所以通过IDELAYE2最多可以将bit位延迟2.5ns。另外,IDELAYE2一旦使用,将引入固定的基础延迟0.6ns。

上述方法是通过调节数据通道的相位关系来解决信号抖动问题的。但在实际应用中,在保证硬件各信号通道严格等长的情况下,各数据通道相位相差不大,此时可调节串行时钟相位。因为发送端的时钟和数据相位关系如图7中的tap1,而在接收端需要调节成tap3。那么此时只需要将接收端的串行时钟通过MMCM延迟90°,使跳边沿能采集到正确稳定的数据,避免亚稳态的产生。

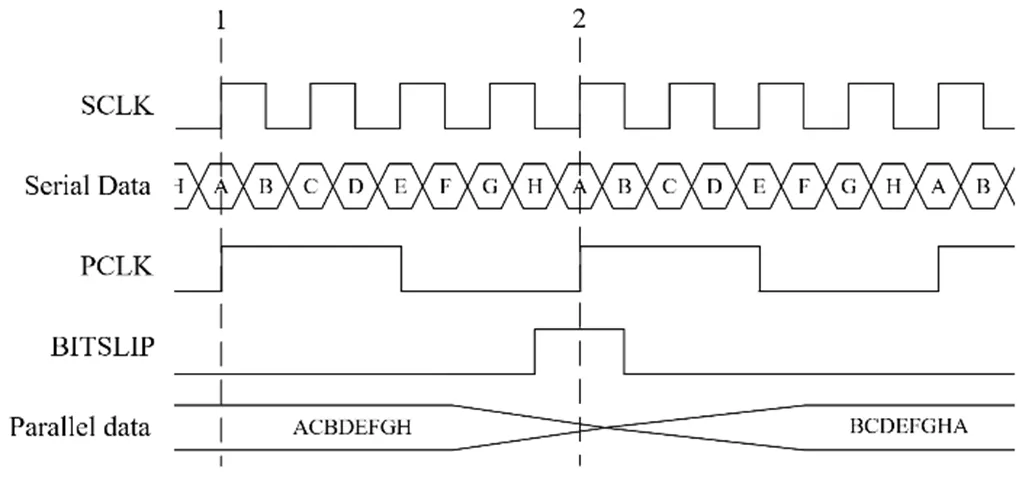

进行Byte位对齐,首先需通过ISERDESE2(专用解串器)把串行信号转成并行信号,重新组成 8bit的并行数据。

图8为DDR模式下的Byte位对齐过程。只要采集到的并行数据和测试数据不同,则继续拉高Bitslip,并进行对齐失败计数。每次Bitslip拉高,都会对并行数据的bit顺序进行调整[13]。如果连续7次对齐失败,则说明bit位对齐失败,返回IDELAYE2。基于此原理,需经过多次调整,最终完成字节对齐。另外还需要为ISERDESE2提供并行时钟PCLK_RX和串行时钟SCLK_RX。

待各通道Byte位均对齐成功后,将得到4路并行数据。最后进行通道对齐,不断调整4路8bit的数据顺序,将其拼接成32bit的并行数据。如果此数据和测试数据相同,则说明数据对齐成功。

图8 Byte位对齐时序图

2.2.2 校验协议

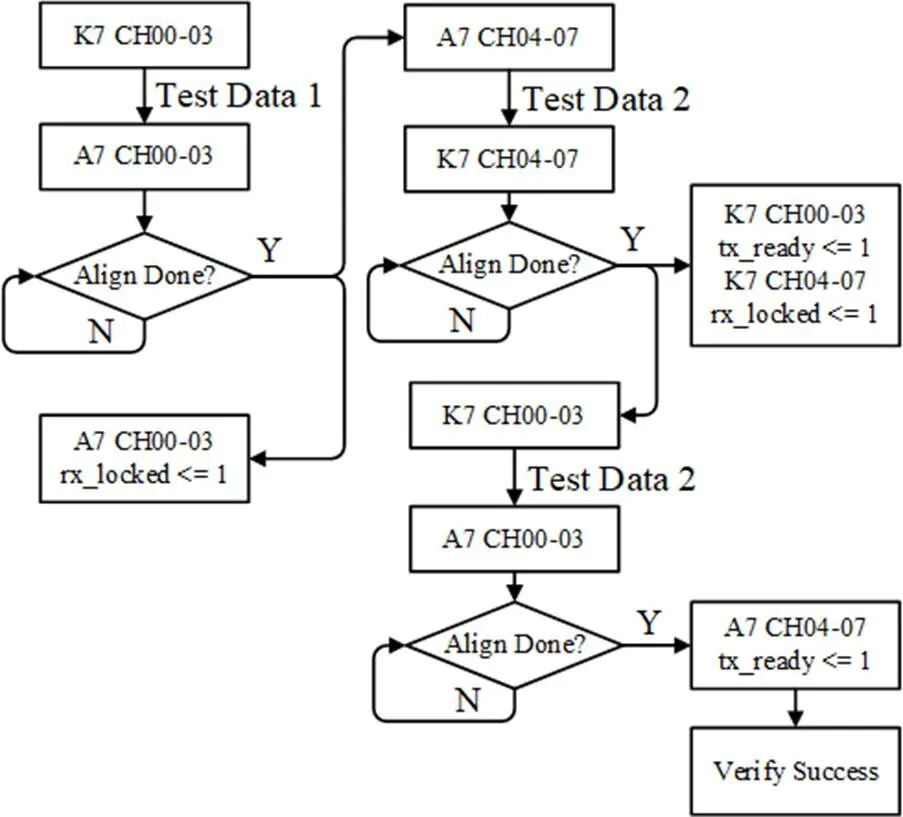

基于上述原理,在常规的LVDS通信之前,需进行片间双向校验。校验流程如图9所示。

图9 双向校验示意图

同步时钟后,两片FPGA的8个数据通道进行数据对齐。首先K7 FPGA的前4路会发送32bit的Test Data 1,A7 FPGA的前4路接收并进行对齐。如果对齐失败,将继续进行数据对齐;如果对齐成功,则说明A7前4路接收数据正常,将前4路的rx_locked拉高。然后通过后4路发送Test Data 2,K7的后4路接收并对齐。

如果K7的后4路对齐失败,将继续进行数据对齐;如果对齐成功,则说明K7的前4路发送正常,后4路接收正常,将前4路的tx_ready和后4路的rx_locked拉高。然后通过前4路发送Test Data 2,A7的前4路接收并对齐。

此时可直接使用第一轮校验的对齐策略来对齐Test Data 2。A7接收到Test Data 2后,则说明其后4路发送正常,将其后4路的tx_ready拉高。校验完成。

通过上述3轮数据对齐,完成一轮闭环校验,如图10所示。该校验协议保证了K7端前4路发送正常,后4路接收正常,A7端前4路接收正常,后4路发送正常。从而保证两个终端之间双向8路通信正常。进而确保后续稳定的数据通信,以达到降低误码率的目的。

图10 闭环校验示意图

2.3 数据通信测试误码率

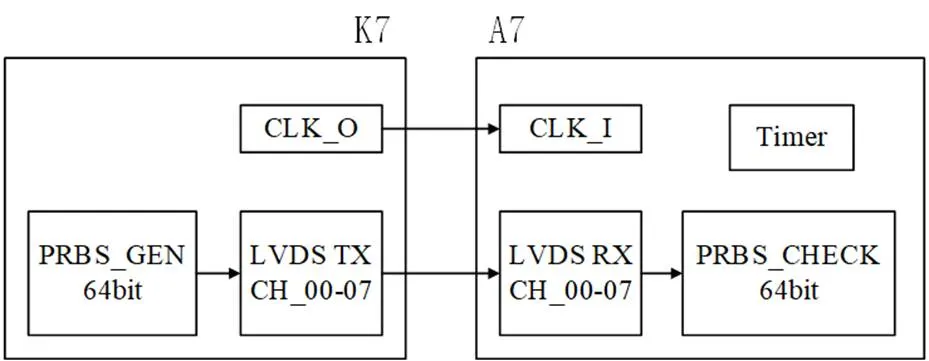

经过校验后,K7和A7两片FPGA的tx_ready和rx_locked都会拉高。随后进入数据通信阶段,8路数据通道开始传输数据,误码率测试方案如图11所示。

图11 通信测试数据传输方案

PRBS(Pseudorandom binary sequence)被称作伪随机码,常用于高速串行通信的误码率测试。其码型由多项式确定,周期性重复。本文将借助伪随机码来测试误码率。

设计使用K7产生64bit的伪随机码,然后分成8路通过LVDS的方式发送出去。由A7的8个数据通道接收并拼接数据,把拼接后的64bit数据输入PRBS检测模块,该模块将输出误码累计个数。为了方便实验统计,还在A7端还加入了计时模块Timer。

因为温度的变化会影响数据传输的稳定性,导致出现亚稳态,使Byte位对齐失败。所以基于此方案,对测试系统进行高低温试验,以检测温度变化对片间通信误码率的影响。

3 试验结果

本试验基于Vivado平台完成。串行时钟为600MHz,并行时钟为150MHz,板间同步时钟为20MHz[14]。

为了直观地统计测试结果,在A7端利用ChipScope对error_cnt进行实时观察。图12给出了系统在20℃环境下持续1h的测试截图。

图12中rx_locked和tx_ready均已拉高,说明系统已经过校验。prbs_data_r是A7端8个通道拼接而成的64bit数据,把该数据输入到PRBS校验模块PRBS_CHECK,此模块输出的误码个数为error_cnt_r。hour_r、min_r、sec_r分别为小时、分钟、秒。为利用ChipScope触发hour_r为1的时刻。实验持续测试1h,在20℃环境下未出现误码。

本试验在-30℃~50℃之间每隔10℃进行一组测试,最终得到9组测试结果,如表1所示。结果表明,在各温度下测试该通信系统,均未出现误码。

因为并行时钟是150MHz,每检测一个并行数据需要6.7ns,所以1h测试期间共检测5.4×1011个数据。如果出现1个误码,经计算得出误码率为1.9×10-12。因此可以推断,在不同温度条件下,经过校验的FPGA片间通信误码率低于1.9×10-12。

图12 A7端ChipScope在线测试图

表1 不同温度下FPGA片间通信误码率测试结果

4 结语

本文基于LVDS技术,设计了一种FPGA片间通信校验协议。在常规的LVDS通信之前,经过多通道多轮校验,完成多通道数据对齐,补偿由于PCB布线和其他外界因素所带来的各路间的延迟。该校验协议有效防止了亚稳态的产生和数据丢失,从而保证后续双向通信稳定进行。试验结果证明,本校验协议可以有效降低误码率,提高通信的稳定性。下一步可以完善校验协议,对影响片间通信稳定性的其他外界因素进行试验,进一步降低误码率。

[1] FANG J, DAI S. Design of multi-channel intelligent transmitter based on HART protocol[J]., 2011, 30(20): 23-25.

[2] HOU Q L, XU K J, FANG M, et al. A DSP-based signal processing methd and system for CMF[J]., 2013, 46(7): 2184-2192.

[3] 易敏, 苏淑靖. 基于LVDS的高可靠性数据传输设计[J]. 微电子学与计算机, 2014(9): 131-134.

YI Min, SU Shujing. High Reliability of Data Transmission Design Based on LVDS[J]., 2014(9): 131-134.

[4] 冯晓东, 杨可. 一种基于LVDS接口的高速并行数据传输系统设计与实现[J]. 数字技术与应用, 2013(6): 64-65.

FENG Xiaodong, YANG Ke. The Design and implementation of one high speed parallel data transfer system based on LVDS[J]., 2013(6): 64-65.

[5] Alkafi A, Imran R, Islam M. Development of FSM based Running Disparity Controlled 8b/10b Encoder/Decoder with Fast Error Detection Mechanism[J]., 2013(2): 2321-1814.

[6] Tseng S.H, Liao Y L. Monolithic power splitter for differential signal[P]. [2011-4-29]. U.S. Patent 13,097,072.

[7] 袁文燕, 郑玥, 宋宇飞, 等. FPGA片间万兆可靠通信的设计与实现[J]. 电视技术, 2014(1): 43-46.

YUAN Wenyan, ZHENG Yue, SONG Yufei, et al. Design and Implementation of 10- Gbit/s Reliable Intra- FPGA Communication[J]., 2014(1): 43-46.

[8] Xilinx. 7 Series FPGAs Select lO Resources User Guide[Z]. America: Xilinx Inc, 2018.

[9] WONG A C, Borrelli C J, Jones L, et al. Transceiver for providing a clock signal[P]. [2013-8-8]. U.S. Patent 13,962,468.

[10] 王建东.基于FPGA的高速串行数据采集及恢复技术研究[D].成都: 电子科技大学, 2017.

WANG Jiandong. Research On High Speed Serial Data Acuisition And Recovery Technology Based On FPGA[D]. Chengdu: School of Microelectronics & Solid State Electronics, 2017.

[11] Xilinx. 7 Series FPGAs GTX/GTH Transceivers User Guide [Z]. America: Xilinx Inc, 2018.

[12] Wirthlin MJ, Takai H. Harding. A soft error rate estimations of the Kintex-7 FPGA within the ATLAS Liquid Argon (LAr) Calorimeter [J]., 2014, 9(1): 1-8.

[13] Herrera-Alzu I,Lopez-Vallejo M. Design Techniques for Xilinx Virtex FPGA Configuration Memory Scrubbers[J]., 2013, 60(1): 376-385.

[14] Xilinx. Vivado Design Suite 7 Series FPGA and Zynq-7000 All Programmable SoC Libraries Guide [Z]. America: Xilinx Inc, 2017.

Verification Protocol for Improving Communication Stability Between FPGAs

CHI Linhui,QIAN Yunsheng,JI Yuhao

(Nanjing University of Science and Technology School of Electronic and Optical Engineering, Nanjing 210094, China)

As field-programmable gate arrays(FPGAs) become increasingly used in large-scale systems, it is often difficult for a single-chip FPGA to perform all the tasks required. High-speed and stable communication between multiple FPGAs has become a focus of research in this field. For this purpose, a verification protocol based on low-voltage differential signaling (LVDS) that can be used for high-speed and stable communication between FPGA chips was designed. This protocol performs multiple rounds of multipath verification based on conventional LVDS communication to improve transmission reliability. Based on this protocol, a nine-channel LVDS communication test system consisting of two Xilinx 7 series FPGAs was built. One channel was used to synchronize the clock, and the other eight channels were used for checksum communication. After a long period of high- and low-temperature tests, the bit error rate was greatly reduced compared with conventional LVDS communications while ensuring a single transmission rate of 1.2Gb/s.

FPGA, LVDS, communication test, verification protocol, high speed and stability, bit error rate

TN223

A

1001-8891(2020)11-1022-02

2020-07-03;

2020-11-02.

池林辉(1996-),男,硕士研究生,主要从事光电成像科研工作。E-mail:chilinhui6@163.com。

钱芸生(1968-),男,教授,博士生导师。主要从事光电测试、图像处理和仿真等工作。E-mail:yshqian@mail.njust.edu.cn。

省部级基金项目(61424120504162412001)。