支持多优先级多输出通道的数据队列调度方法和硬件实现

2020-11-05徐金波常俊胜

徐金波,常俊胜,李 琰

(国防科技大学计算机学院,湖南 长沙 410073)

1 引言

随着高性能计算机系统HPC(High Performance Computer)计算速度从千万亿次级(P级,Petascale)向百亿亿次级(E级,Exascale)的不断提升[1 - 3],微处理器芯片和互连网络芯片所需处理的数据量呈指数级上升。通常每个ASIC(Application Specific Integrated Circuit)芯片需要使用多个处理部件对多个输入数据源进行处理,这涉及到多个数据队列的调度问题。

数据队列调度的类型和调度方法有多种分类方式[4 - 6]。按照输出队列数量来分类,有多输入单输出调度、多输入多输出调度;按照服务质量来分类,有优先级队列PQ(Priority Queueing)、公平队列FQ(Fair Queueing)[7]、加权公平队列WFQ(Weighted Fair Queueing)[8 - 10]、加权循环调度WRR(Weighted Round Robin)[11]、差额加权循环调度DWRR(Deficit Weighted Round Robin)[12]、可变加权循环调度VWRR(Variably Weighted Round Robin)[13]、通用循环调度URR(Uniform Round Robin)[14]等。对于ASIC芯片片内的多输入多输出调度问题,已有的调度方法存在一定的限制或不足。有的方法仅能完成单输出的调度;有的方法不能保证所有输入数据都能够得到合理的资源,甚至会饿死;有的方法无法使高优先级的输入队列得到优先调度;有的方法由于算法较复杂而不适合于ASIC芯片逻辑实现。

本文针对高性能计算领域的芯片内数据传输问题,提出一种支持多优先级多输出通道的数据队列调度方法,用于将多个输入数据源的数据流根据多个输出队列的资源占用情况进行科学调度,实现公平高效和支持多种服务等级的任务分发。本文方法的主要优势如下:

(1)适用范围广。通过调整配置参数,该方法既可以实现完全公平均衡的随机分发模式,也可以实现多种优先级的区分服务质量的模式。

(2)对于随机模式,随机分发模式下处于空闲状态的多个输出通道将会轮流接收输入源的输入数据。

(3)对于区分服务质量模式,所有输入源、输出通道被划分为不同优先级,使某组输出通道只接收对应优先级的输入源的数据。

(4)硬件实现简单,代价小。将所有输出通道的资源状态信息整合在同一个仲裁器中,从而使得所有输入数据源只使用一个仲裁器即可实现向所有输出通道的任务调度,适用于ASIC芯片逻辑实现。

2 支持多优先级多输出通道的数据队列调度方法

通过将所有输出通道的资源状态信息整合在同一个仲裁器中,从而使得所有输入数据源只使用一个仲裁器即可实现向所有输出通道的任务调度。该仲裁器在对多个请求进行仲裁的时候,需要以输出通道的资源状态信息为指导,以决定应该将仲裁应答返回给哪一个请求,以及该得到应答的输入数据应该分发到哪一个输出通道。对于随机分发模式,所有输出通道的资源状态信息将对所有的输入源有指导意义,处于空闲状态的输出通道将会轮流接收输入数据;对于区分服务质量的模式,不同的输出通道具有不同的优先级,某一优先级的输出通道的资源状态信息只对对应优先级的输入源有效,这一输出通道只接收对应优先级的输入源的数据。

记输入数据源的数量为n,n个输入源依次为{I0,I1,I2,…,In-1};输出通道的数量为m,m个输出通道依次为{O0,O1,O2,…,Om-1}。根据控制参数mode_sel选择采用随机分发模式或区分服务质量模式进行调度。控制参数mode_sel为0时,指示当前工作模式为随机通道模式(Random模式),即处于空闲状态的输出通道将会轮流接收输入数据;控制参数mode_sel为1时,指示当前工作模式为区分服务质量QoS(Quality of Service)模式,即所有输出通道被划分为多组具有不同优先级的通道,每组通道的优先级相同,不同组的通道的优先级不同,某组输出通道将只接收对应优先级的输入源的数据。记共有d个不同的优先级,配置参数priority_vector0用于配置每个输入数据源的优先级,依次为{p0,p1,p2,…,pn-1}(其中pi= 0,1,2,…,d-1;i=0,1,2,…,n-1);配置参数priority_vector1用于配置每个输出通道的优先级,依次为{q0,q1,q2,…,qm-1};qi= 0,1,2,…,d-1(其中i=0,1,2,…,m-1)。

2.1 Random模式

将mode_sel控制参数配置为0,使得所有的输入数据源可以公平地使用所有的输出通道。记n个输入源的请求向量为{r0,r1,r2,…,rn-1},ri为0或1(i=0,1,2,…,n-1),ri为0时表示第i个输入源不存在数据请求,ri为1时表示第i个输入源存在数据请求,所有存在数据请求的输入源将向一个轮转仲裁器请求使用输出通道。记m个输出通道的忙闲状态向量为{v0,v1,v2,…,vm-1},vi为0或1(i=0,1,2,…,m-1),vi为0时表示第i个输出通道处于忙碌状态,当前无法接收新的数据处理请求,vi为1时表示第i个输出通道处于空闲状态,此时可以接收新的数据处理请求。

轮转仲裁器的仲裁令牌轮转规则如下:仲裁令牌在完成一次仲裁应答后将会传递给当前得到令牌的输入源的下一个输入源,即假设Ii得到了仲裁应答,令牌将会传递给I(i+1) mod n。

仲裁应答的执行规则如下:如果所有vi均为0,表示所有输出通道均未空闲,这时所有输入源都无法得到仲裁应答;当存在至少一个vi为1时,表示至少有一个输出通道可以接收数据处理请求,假设此时仲裁令牌在Ii位置,如果ri为1,表示Ii存在数据请求,那么Ii将得到仲裁应答;如果ri为0,表示Ii不存在数据请求,那么依次向后查看Ii+1,Ii+2,Ii+3,…,In-1,I0,I1,Ii-1,Ii之后的第一个存在数据请求的输入源将得到仲裁应答。

输出通道的选择规则如下:使用一个输出通道选择令牌实现输出通道的轮转,初始状态下,通道选择令牌在O0上,第一个得到仲裁应答的输入源将数据输出到O0;然后通道选择令牌会轮转到O1上,以此类推;当通道选择令牌轮转到Oi上时,若vi为1,表示Oi处于空闲状态,则当前得到仲裁应答的输入源将选择Oi作为输出通道;若vi为0,表示Oi未处于空闲状态,则当前得到仲裁应答的输入源将选择Oi之后的第一个空闲的输出通道(如Oi+1空闲,则选择Oi+1),同时,通道选择令牌轮转到下一个输出通道。

2.2 QoS模式

将mode_sel控制参数配置为1,使得某一优先级的输出通道的资源状态信息只对对应优先级的输入源有效,这一输出通道将只接收对应优先级的输入源的数据。另外,按照应用需求对priority_vector0参数进行配置,同时对priority_vector1参数进行配置,目的是使得优先级较高的任务可以得到更多的输出通道。所有的输入源仍然仅使用一个仲裁器进行数据调度,但不同优先级的输入源将根据不同的priority_vector0/1参数进行区分。

轮转仲裁器的仲裁令牌轮转规则与Random模式相同,具体如下:仲裁令牌在完成一次仲裁应答后将会传递给当前得到令牌的输入源的下一个输入源,即假设Ii得到了仲裁应答,令牌将会传递给I(i+1) mod n。

仲裁应答的执行规则如下:如果所有vi均为0,表示所有输出通道均未空闲,这时所有输入源都无法得到仲裁应答;当存在至少一个vi为1时,表示至少有一个输出通道可以接收数据处理请求,假设此时仲裁令牌在Ii位置,如果ri为1且所有与pi相同的qj对应的输出通道Oj中存在一个空闲通道,即vj=1,这表示Ii存在数据请求且支持当前优先级的输出通道中存在一个空闲通道,那么Ii将得到仲裁应答;如果ri为0,表示Ii不存在数据请求,那么依次向后查看Ii+1,Ii+2,Ii+3,…,In-1,I0,I1,Ii-1,直到找到一个Ik符合如下条件:rk为1且所有与pk相同的qk对应的输出通道Ok中存在一个空闲通道,即vk=1,则Ik将得到应答。

输出通道的选择规则如下:每组具有相同优先级的输出通道使用各自的输出通道选择令牌实现本组内输出通道的轮转;初始状态下,每组具有相同优先级的输出通道的通道选择令牌在该组通道的第一个通道上;当该组的某个数据源得到仲裁应答后,若该组优先级的通道选择令牌所在的输出通道的vi为1,表示输出通道Oi处于空闲状态,则当前得到仲裁应答的输入源将选择Oi作为输出通道;若vi为0,表示Oi未处于空闲状态,则当前得到仲裁应答的输入源将选择Oi之后的本组内的第一个空闲的输出通道(如Oi+1空闲,则选择Oi+1),同时,通道选择令牌轮转到本组内的下一个输出通道。

3 硬件结构设计与实现

本文所提出的方法可以应用于ASIC芯片内的数据队列调度,满足ASIC芯片内多组输入数据对多个输出通道资源进行请求的需求。其硬件结构主要由输入数据队列、输出数据队列、仲裁器、输出队列资源感知逻辑和输出通道选择逻辑组成。

对于输入数据队列,通常为每个输入通道分配一个输入数据队列,用于缓存待仲裁的数据。

同样地,对于输出数据队列,通常为每个输出通道分配一个输出数据队列,用于缓存由仲裁器选出的待处理的数据。

所有输入数据源只使用一个轮转仲裁器来实现向所有输出通道的任务调度。该仲裁器在对多个请求进行仲裁的时候,需要以输出通道的资源状态信息为指导,以决定应该将仲裁应答返回给哪一个请求,以及该得到应答的输入数据应该分发到哪一个输出通道。输出通道的资源状态信息通过输出队列资源感知逻辑获取,而得到应答的输入数据应该分发到哪一个输出通道则是由输出通道选择逻辑控制。

输出队列资源感知逻辑实时对每个输出队列的资源使用情况进行计算,并判断每个输出队列是否有足够的空间来容纳得到仲裁的数据。当数据进入某个输出队列时,该队列的资源信用递减;当数据从该输出队列提取出来进行处理时,该队列的资源信用递加。每个队列的资源信用值作为判断该队列是否可用的依据,当前信用值大于待放入的数据大小时,即可认为数据可以放入该队列。

输出通道选择逻辑在Random模式与QoS模式下有所不同。在Random模式下,将轮转选择空闲的输出通道作为最终输出通道;在QoS模式下,不同优先级的数据通道各自独立进行选择,每个优先级对各自空闲的输出通道进行轮转选择。

图1给出了在Random模式下进行数据调度的示意图。

Figure 1 Illustration of data scheduling in Random mode图1 Random模式下数据调度示意图

以10输入5输出(即n=10,m=5)的数据调度为例,对Random模式下的数据队列调度方法进行说明。如图1所示,初始状态下,ri=0(i=0,1,2,…,9),vj=1(j=0,1,2,3,4),仲裁器令牌在I0上,通道选择令牌在O0上,将mode_sel控制参数配置为0进入Random模式。

(1)T0时刻(仲裁器令牌位于无数据请求的输入源上的情形),r1,r2,r4变为1,由于令牌在I0上,但r0为0,因此I1获得仲裁应答,r1在得到应答后将变为0;由于通道选择令牌在O0上,且v0为1,因此获得应答的I1将选择O0输出,v0将变为0;同时,仲裁器令牌轮转到I2上,通道选择令牌轮转到O1上。

(2)T1时刻(仲裁器令牌位于有数据请求的输入源上的情形),r2,r4仍在等待轮转仲裁器应答,因此r2,r4仍为1,另外,r1由于出现了新的数据请求而再次变为1,r6也因为有数据请求而变为1;由于仲裁器令牌在I2上,且r2为1,因此I2获得仲裁应答,r2在得到应答后将变为0;由于通道选择令牌在O1上,且v1为1,因此获得应答的I2将选择O1输出,v1将变为0;同时,仲裁器令牌轮转到I3上,通道选择令牌轮转到O2上。

(3)T2时刻(通道选择令牌位于非空闲的输出通道上的情形),经过一段时间后,部分输出通道可能变为非空闲状态,假设此时只有v0,v2为1,另外,r0,r3,r4,r6为1,仲裁器令牌在I7上,通道选择令牌在O3上;由于r7为0,仲裁器令牌在I7上,因此I0获得仲裁应答,r0在得到应答后将变为0;由于通道选择令牌在O3上,但v3为0,因此获得应答的I0将选择下一个空闲的O0输出,v0将变为0;同时,仲裁器令牌轮转到I1上,通道选择令牌轮转到O1上。

以此类推,轮转仲裁器持续进行调度作业。

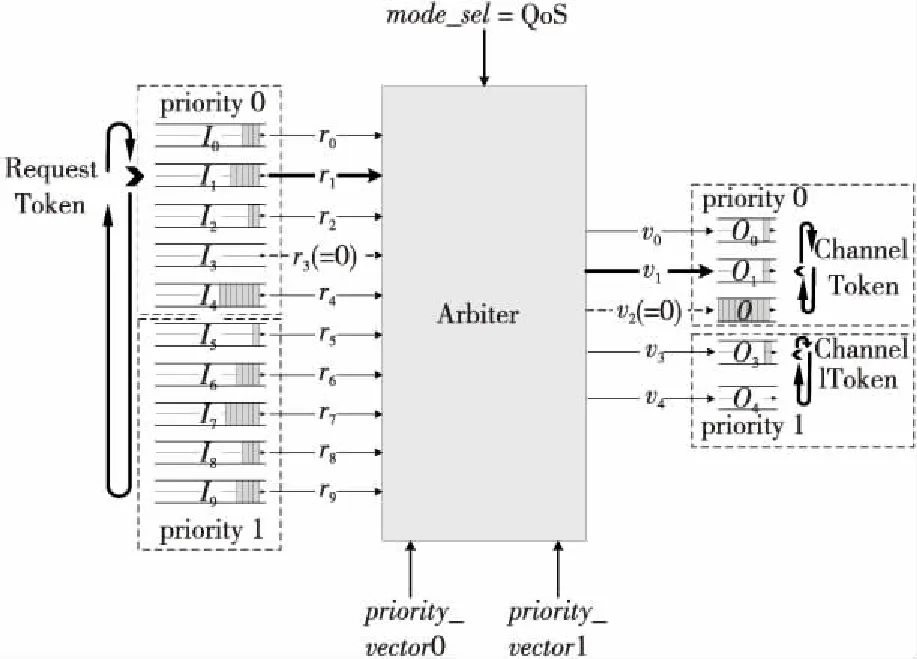

图2给出了在QoS模式下进行数据调度的示意图。

Figure 2 Illustration of data scheduling in QoS mode图2 QoS模式下数据调度示意图

如图2所示,初始状态下,ri=0(i=0,1,2,…,9),vj=1(j=0,1,2,3,4),仲裁器令牌在I0上,通道选择令牌在O0上。首先将mode_sel控制参数配置为1以进入QoS模式;其次将priority_vector0配置为{0,0,0,0,0,1,1,1,1,1},即I0,I1,I2,I3,I4的优先级为0,I5,I6,I7,I8,I9的优先级为1(假设共支持2种优先级);然后将priority_vector1配置为{0,0,0,1,1},即O0,O1,O2可接收优先级为0的输入数据,O3,O4可接收优先级为1的输入数据。

(1)T0时刻(仲裁器令牌位于无数据请求的输入源上的情形),r1,r2,r4变为1,由于令牌在I0上,但r0为0,因此I1获得仲裁应答,r1在得到应答后将变为0;由于I1的优先级为0,而优先级为0的通道选择令牌在O0上,且v0为1,因此获得应答的I1将选择O0输出,v0将变为0;同时,仲裁器令牌轮转到I2上,优先级0的通道选择令牌轮转到O1上,优先级1的通道选择令牌仍位于O3上。

(2)T1时刻(仲裁器令牌位于有数据请求的输入源上的情形),r2,r4仍在等待轮转仲裁器应答,因此r2,r4仍为1,另外,r1由于出现了新的数据请求而再次变为1,r6也因为有数据请求而变为1;由于仲裁器令牌在I2上,且r2为1,因此I2获得仲裁应答,r2在得到应答后将变为0;由于I2的优先级为0,而优先级为0的通道选择令牌在O1上,且v1为1,因此获得应答的I2将选择O1输出,v1将变为0;同时,仲裁器令牌轮转到I3上,优先级0的通道选择令牌轮转到O2上,优先级1的通道选择令牌仍位于O3上。

(3)T2时刻(轮转仲裁器应答从优先级0切换到优先级1的情形),若r1,r4,r6为1,由于仲裁器令牌在I3上,但r3为0,因此I4获得仲裁应答,r4在得到应答后将变为0;由于I4的优先级为1,而优先级为1的通道选择令牌在O3上,且v3为1,因此获得应答的I4将选择O3输出,v3将变为0;同时,仲裁器令牌轮转到I5上,优先级0的通道选择令牌仍保持在O2上,由于优先级1的输出通道只有O3,因此优先级1的通道选择令牌仍位于O3上。

(4)T3时刻(优先级1无通道空闲的情形),若r1,r6为1,由于仲裁器令牌在I5上,I5的优先级为1,而可以接收优先级1的输入请求的输出通道只有O3,且未处于空闲状态,因此r6为1的I6也无法获得仲裁应答,进而,优先级为0的I1得到了仲裁应答,r1在得到应答后将变为0;由于I1的优先级为0,而优先级为0的通道选择令牌在O2上,且v2为1,因此获得应答的I1将选择O2输出,v2将变为0;同时,仲裁器令牌轮转到I2上,优先级0的通道选择令牌轮转到O0上,优先级1的通道选择令牌仍位于O3上。

以此类推,轮转仲裁器持续进行调度作业。

4 实验结果

基于该数据队列调度方法,本文在天河超级计算机系统的网络接口芯片中对软硬件接口数据队列的调度进行了优化,并在软模拟环境、硬件仿真环境以及FPGA验证环境中进行了测试。

4.1 实验场景

在天河超级计算机系统的网络接口芯片中,软件将作业编译为大量描述符指令发送给芯片进行处理。多个线程之间的描述符指令需要通过合理的任务调度以达到公平性或实现QoS需求。为了实现更高的吞吐率,网络接口芯片提供2套描述符处理部件对描述符进行处理。当系统不存在QoS需求时,2套处理部件以负载均衡的方式同时工作,可以达到提高系统吞吐率的目的;当系统存在QoS需求时,2套部件配置不同的优先级,分别接收不同优先级的线程的描述符指令,从而为不同的线程提供不同的服务质量。

为了满足上述需求,将本文提出的支持多优先级多输出通道的数据队列调度方法应用于网络接口芯片中。该芯片最大可支持64个线程,即存在64个输入数据队列,每个数据队列保存对应线程的描述符指令;数据队列调度部件与2套数据处理部件之间分别使用1个输出数据队列进行数据缓存,因此共有2个输出数据队列。仲裁器实现64输入2输出的数据仲裁。通过寄存器控制接口实现对调度器工作模式(Random模式或QoS模式)以及优先级参数的配置。数据处理逻辑工作频率为1 GHz。

4.2 多输出通道与单输出通道对调度时间与处理时间的影响

为了评价多输出通道对描述符事务处理速度的优化效果,本节分别测试了使用多输出通道与单输出通道时的数据调度时间与描述符处理时间,并进行比较。实验将数据调度部件配置为Random模式。

本文所提出的调度器硬件设计方案可以支持对输出通道的开关配置,通过寄存器控制接口可以关闭其中一个输出通道,将所有数据调度到一套处理部件上进行处理。这种方式可以保证多输出通道与单输出通道的处理时间的比较结果是在同样的实验环境中获取的,以保证数据客观有效。

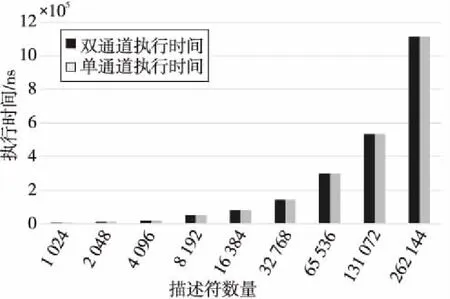

首先,为了比较多输出通道与单输出通道的数据调度时间,需要构建一种测试场景使软件输入数据的速度为系统的性能瓶颈,这时,处理部件的处理速度足够快,以至于输出通道总是处于可用状态,从而可以充分反映出多输出通道与单输出通道的调度时间的比较结果。本文将所有描述符配置为短消息类型,处理部件在收到这种描述符后不需要执行DMA(Direct Memory Access)内存操作,可以立刻产生数据报文并发送,因此处理速度足够快,使数据调度部件与处理部件之间的输出队列始终可以接收调度部件输出的数据。图3给出了64个线程发送并处理短消息描述符所需的时间与描述符数量之间的对应关系。执行时间从描述符进入数据调度部件的输入队列开始计算,到数据报文从数据处理部件输出接口发出为止。可以看出,当系统受限于软件输入描述符数据的速度时,双输出通道与单输出通道的执行时间非常接近。例如,1 024个描述符的单通道和双通道执行时间分别为6 749 ns和6 881 ns,差距为2%;8 192个描述符的单通道和双通道执行时间分别为51 034 ns和51 621 ns,差距为1.2%;262 144个描述符的单通道和双通道执行时间分别为1 114 538 ns和1 117 892 ns,差距为3‰。此时,处理部件处理描述符的时间代价为固定的,且输出通道始终空闲,可以随时接收仲裁器的输出数据,这表明双输出通道的调度时间与单输出通道的调度时间是基本接近的。该实验结果说明,本文提出的多输出队列的调度过程产生的额外时间代价非常小。

Figure 3 Comparison of scheduling time between dual-output-channel and single-output-channel图3 双输出通道与单输出通道的调度时间比较

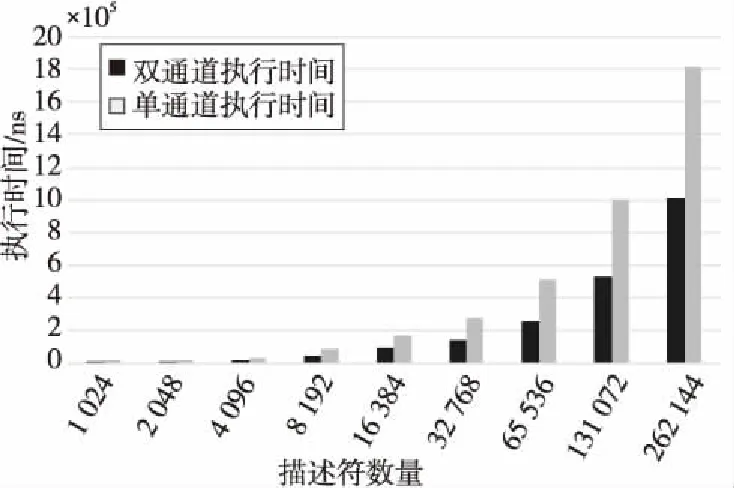

然后,为了验证多输出通道在DMA内存操作事务处理方面相对于单输出通道的提升,进行如下实验:每个描述符指令对应一个DMA内存读取事务,每个DMA事务执行的内存读取的数据量在64 B~819 200 B随机变化。在该场景下,处理部件需要更多时间来处理每个描述符。通过使用多输出通道,可以配置多套处理部件对描述符进行处理,从而提高并行性。图4给出了64个线程发送并处理DMA类型描述符所需的时间与描述符数量之间的对应关系。执行时间从描述符进入数据调度部件的输入队列开始计算,到所有数据报文从数据处理部件输出接口发出为止。可以看出,通过使用双输出通道及对应的处理部件,DMA事务的执行时间相对于单输出通道大大减少。例如,1 024个描述符的单通道和双通道执行时间分别为15 943 ns和8 523 ns,比值为1.87;16 384个描述符的单通道和双通道执行时间分别为170 966 ns和90 782 ns,比值为1.88;131 072个描述符的单通道和双通道执行时间分别为1 064 224 ns和534 928 ns,比值为1.99。原因在于双输出通道的数据调度部件可以满足双处理部件实现并行处理的数据调度需求。该实验结果说明,本文提出的多输出队列调度方案对于提升芯片处理事务的速度具有显著作用。

Figure 4 Performance improvement for DMA transactions with dual-output-channel图4 双输出通道对DMA内存事务的性能优化

4.3 多优先级对服务质量的影响

为了评价本文工作中的多优先级调度方式对服务质量的影响,进行如下实验:将64个线程分为2组,16个线程配置为较高的优先级0,另外48个线程配置为较低的优先级1。优先级0的线程使用0号输出通道,优先级1的线程使用1号输出通道。每个线程发送并处理相同数量的DMA内存读取描述符,每个描述符所处理的DMA内存数据大小固定为1 024 B。实验时,数据调度部件配置为QoS模式。

图5给出了0号通道与1号通道的执行时间比较结果。执行时间从描述符进入数据调度部件的输入队列开始计算,到所有数据报文从数据处理部件输出接口发出为止。可以看出,16个高优先级的线程使用单独的输出通道与处理部件,执行时间远低于另外48个低优先级使用另一组输出通道的执行时间。例如,1 024个描述符(每个线程发送16个描述符)的0号高优先级通道和1号低优先级通道的执行时间分别为1 583 ns和4 601 ns,比值为1∶2.9;32 768个描述符的0号高优先级通道和1号低优先级通道的执行时间分别为35 796 ns和100 426 ns,比值为1∶2.8;262 144个描述符的0号高优先级通道和1号低优先级通道的执行时间分别为275 670 ns和745 172 ns,比值为1∶2.7。该实验结果说明,本文提出的多优先级多输出队列调度方案可以实现对不同线程的服务质量的区分。

Figure 5 Comparison of execution time between different priority groups in dual-output-channel QoS mode图5 QoS模式下双输出通道的执行时间对比

4.4 资源使用情况

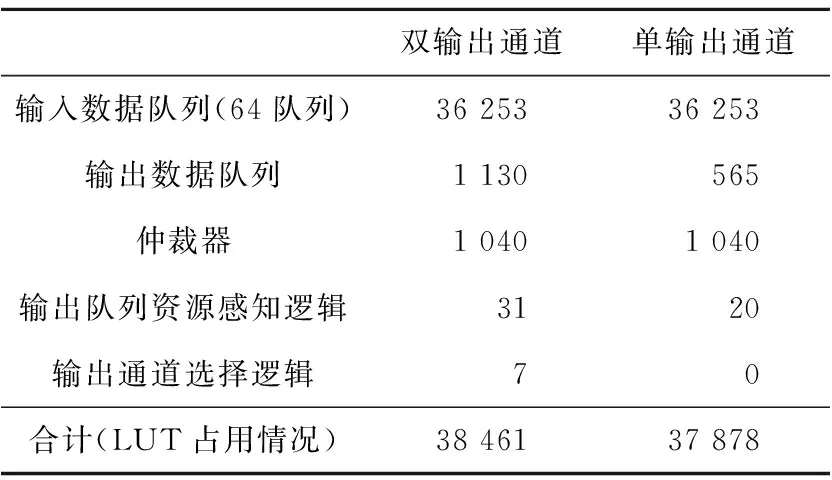

为了评价本文的多优先级多输出通道调度器的硬件实现代价,本节将其与单输出通道的调度器进行了硬件资源情况比较。资源比较工作在自主开发的FPGA验证平台上进行,FPGA采用Xilinx Virtex UltraScale VU440芯片。

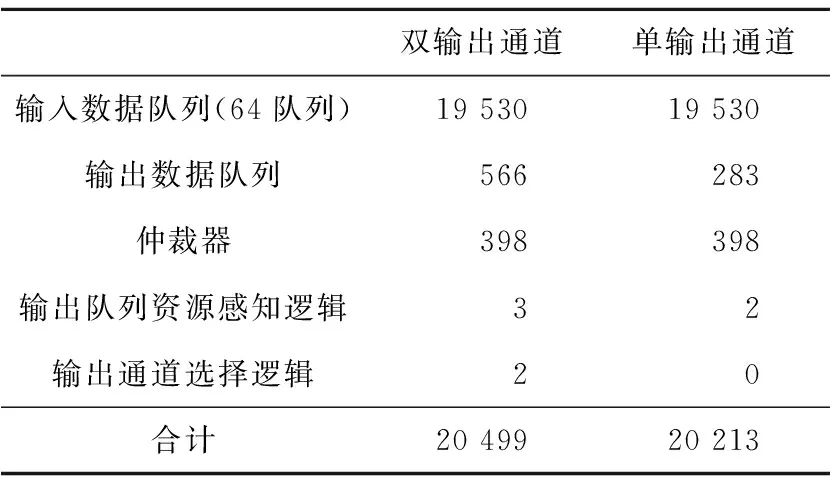

表1给出了64输入2输出调度器与64输入1输出调度器的逻辑资源(FPGA芯片的查找表LUT使用情况)统计对比情况;表2给出了64输入2输出调度器与64输入1输出调度器的寄存器资源统计对比情况。所统计的硬件资源主要包括输入数据队列、输出数据队列、仲裁器、输出队列资源感知逻辑、输出通道选择逻辑等部分,处理部件不包含在统计范围内。结果表明,增加输出通道需要增加的硬件资源主要包括输出数据队列所增加的寄存器资源、输出队列资源感知逻辑与输出通道选择逻辑所需要的逻辑资源,而仲裁器本身并不需要增加新的资源。所增加的寄存器资源和逻辑资源仅占整个调度器逻辑的一小部分,双输出通道与单输出通道相比所增加的逻辑资源为583,只比单输出通道的总逻辑资源多1.5%;双输出通道与单输出通道相比所增加的寄存器逻辑资源为286,只比单输出通道的总逻辑资源多1.4%。

Table 1 Comparison of logic resources between dual-output-channel and single-output-channel表1 双输出通道与单输出通道调度器的逻辑资源(LUT占用情况)对比

Table 2 Comparison of register resources between dual-output-channel and single-output-channel表2 双输出通道与单输出通道调度器的寄存器资源对比

5 结束语

本文针对高性能计算领域的芯片内数据传输问题,提出了一种支持多优先级多输出通道的数据队列调度方法,用于将多个输入数据源的数据流根据多个输出队列的资源占用情况进行科学调度,实现公平高效和支持多种服务等级的任务分发。所提出的方法适用范围广,可以通过调整配置参数,使之工作在Random模式或QoS模式下,将该方法应用于ASIC芯片设计时具有硬件实现代价低的优势。基于该数据队列调度方法,在天河超级计算机系统的网络接口芯片中对软硬件接口数据队列的调度进行了优化,并进行了实际测试。实验结果表明,所实现的多输出队列调度器与传统的单输出队列调度器相比并未产生额外的时间代价;多输出队列调度方案对于提升芯片处理事务的速度具有显著作用;同时,配置为QoS模式时可以实现对不同线程的服务质量的区分,且为灵活可配置的;另外,多优先级多输出通道的仲裁器硬件实现与单输出通道的仲裁器实现相比,并未增加明显的硬件实现代价。