基于ADRV9009频谱监测接收机设计与实现

2020-11-04吴伙土

吴伙土

(厦门市合佳兴电子有限公司,福建 厦门 361015)

0 引言

随着无线通信的飞速发展,对非法使用无线电进行频谱有效监测势在必行。传统的宽频带频谱监测方案主要有两种方式实现:一种是多片高速ADC设置不同接收频点组成宽频带监测方案,另外一种是超高速ADC实现快速扫频进行频谱监测方案。

多片高速ADC组成宽频带监测方案在宽带频谱监测的场景下,必须严格每片ADC的输入参考时钟同相位、等幅度、等倾斜率;还要确保各片ADC的前端射频链路完全一致性以及ADC的输出数字信号到FPGA接口要完全等长。即使在各片ADC的参考输入时钟和ADC前后端链路完全一样情况下,各片ADC芯片内部的锁相环也会产生随机抖动。因此,监测回来的频谱信号就会含有杂散和谐波等,无法观测到实际的真实频谱信号。而且该方案系统硬件设计指标要求非常高,体积也会明显大得多。

另外一种快速扫频监测方案,需要用到超高速的ADC芯片,来进行快速切换频点来回扫描监测。当被监测的信号跳变速度超过这种高速ADC的切换速度,就监测不到信号。因此该方案监测频谱信号受限,再者这种高端ADC都是禁运。

基于上述两种方案的缺陷,本文采用ADI的最新业界带宽最宽、最高性能的集成式收发器ADRV9009芯片来实现宽频带频谱监测。ADRV9009内部集成两路16bit的ADC,具有两个独立接收通道,每个接收通道具有宽动态范围的独立宽带200MHz;两路14bit的DAC,发射最大带宽是450MHz;两路观测通道ORX,ADC位数16bit,接收最大带宽450MHz。ADRV9009可调谐输入输出范围75MHz-6000MHz,并且快速调频时间在100ms内完成一次跳频。数据接口采用业界主流的高速串行JESD204B数据传输接口与FPGA对接。本文主要讨论基于ADRV9009频谱监测接收机硬件设计系统实现、数据高速通信接口JESD204B的介绍、以及最后系统整体性能测试验证。

1 系统总体架构设计

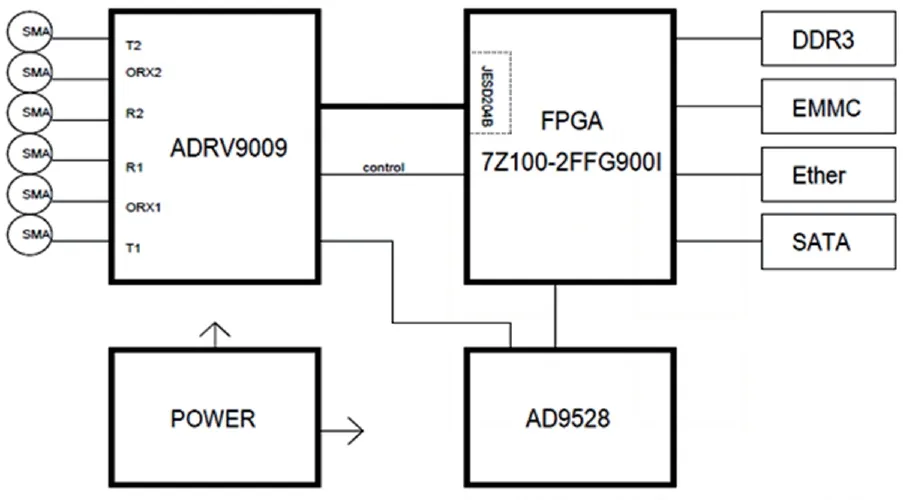

由上述讨论分析,该宽带频谱监测接收机方案采用ADI的最宽捷变收发器ADRV9009作为主要前端无线电监测监测接收通道。数字信号的核心处理芯片采用Xilinx的FPGA 7Z100-2FFG900I该FPGA型 号 属 于Xilinx Zynq SOC系列;内嵌双A9的ARM处理器,方便直接对外围设备进行配置和用户接口控制。FPGA内部GTX Transceivers接口具有12.5Gb/s最大数据数率,满足ADRV9009的数据接口JESD204B最大速率。系统总体框图如图1。

图1 频谱监测接收机系统实现框图

图1中,FPGA是整个系统的核心数字信号处理和控制芯片。FPGA对ADRV9009进行配置,使其工作在所需的频点和最大带宽模式,或者设定ADRV9009跳频状态,使接收机工作在全频段扫频模式。ADRV9009采集回来的数据,通过JESD204B高速接口传输给FPGA;FPGA对所采集回来的数字信号进行频谱功率检测和包络分析等。或者不做任何分析,把采集的原始信号记录在系统自带的EMMC存储芯片,或SATA外挂硬盘;也可以通过系统的千兆网口传输到上位机做进一步数据分析等。FPGA PL端的DDR3作为系统的数字信号处理缓存,FPGA的PS端的DDR作为ARM9的运行内存。

整个系统各部分电路所需时钟由AD9528时钟芯片产生提供。该时钟芯片是一款集成内部双级PLL、JESD204B SYSREF发生器,专门配套高速ADC、DAC带有JESD204B接口协议使用的时钟芯片,并且可用于多器件同步。FPGA的PS端对时钟芯片AD9528进行初始化配置,AD9528输出提供给ADRV9009和FPGA运行所需对应的Device clock和SYSREF时钟频率。ADRV9009的供电和FPGA的GTX bank供电、时钟芯片等这个三个子模块的供电,必须全部用高稳的LDO供电;避免电源引入的谐波干扰,产生杂散信号,影响ADC的采样精度,以及减少高速GTX的数据接口误码率。

2 数据高速传输通道JESD204B接口

JEDEC Standard No.204B(JESD204B)是一个高速ADC和DAC数字转换器与FPGA或ASIC逻辑器件的标准串行接口。具有比CMOS和LVDS接口在速度、尺寸、功耗、成本上更有优势。JEDS204B具有占用芯片引脚数量少,可以使芯片芯片封装尺寸做得更小,在同样功率一定时提供更大的吞吐量。并且数据接口数量少,在PCB设计布线走线数量也变得更少,电路板layout走线占用空间大大减少,PCB设计就更容易设计,系统的整体硬件成本会变得更低。当然对高速差对的走线要注意路径完整性、差分阻抗要控制好的在100Ω。

JESD204B接口协议规范定义了三个子类:子类0(Subclass 0),子类1(Subclass 1),子类2(Subclass 2)。

子类0(Subclass 0):不支持确定性延迟;建链所需的信号有Device clock(设备时钟)、Lanes(204B的通道数量)、SYNC~(同步时钟)。

子类1(Subclass 1):使用SYSREF(系统参考时钟)的确定性延迟; 建链所需的信号有Device clock(设备时钟)、Lanes(204B的通道数量)、SYNC~(同步时钟)、SYSREF(系统参考时钟)。

子类2(Subclass 2):使用SYNC~(同步时钟)的确定性延迟。建链所需的信号有Device clock(设备时钟)、Lanes(204B的通道数量)、SYNC~(同步时钟)。

子类1(Subclass 1)主要用在针对工作在500MPS及其以上的转换器,子类2(Subclass 2)主要是用在500MPS以下的转换器。JESD204B支持的通道数据数率最大到12.5Gb/s,并把设备分为三个速度等级,所有等级的源阻抗和负载阻抗都是100Ω±10%。

速度等级一:与JESD204和JESD204A标准的通道速率一样,最高速率都是3.125Gb/s。

速度等级二:最高速率为6.375Gb/s,并且信号的最低差分电平从速度等级一的Vpp500mV降为400mV峰峰值。

速度等级三:最高速率为12.5Gb/s,该等级把信号最低差分电平峰峰值进一步降为Vpp360mV。

随着204B通道数据数率上升,通过降低芯片接口驱动器的压摆率,最低差分电平峰峰值也随之降低,从而使物理实现更容易;信号的峰峰值越低,器件的接口功耗也会随之减少。

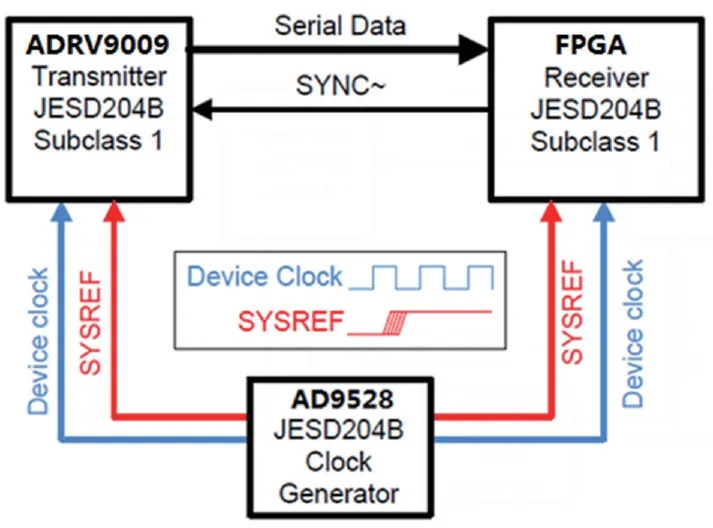

本设计方案采用JESD204B子 类1(Subclass1),作为ADRV9009与FPGA之间的数据接口协议。ADRV9009与FPGA之间的JESD204B接口的数据链路如图2所示。

图2 系统JESD204B链路框图

JESD204B接口的单个通道数率计算公式:Lane rate=(M×N'×[10⁄8]×Fs)/L;其 中M是ADC/DAC的数量,N'是ADC/DAC的位数,Fs是采用时钟,10/8是8b/10b编码的链路开销,L是通道数。本设计系统是双路ADC,位数16bit,采样率245.76MHz,使用2个通道传输,用到IQ采样传输。因此带入上面公式计算得单个Lane通道速率Lane rate为9830.4MHz,因为XC7Z100系列FPGA的GTX接口最大速率是12.5GHz,满足ADRV9009芯片JESD204B接口与FPGA的GTX接口之间的传输数字速率9.8304GHz。

3 系统平台验证

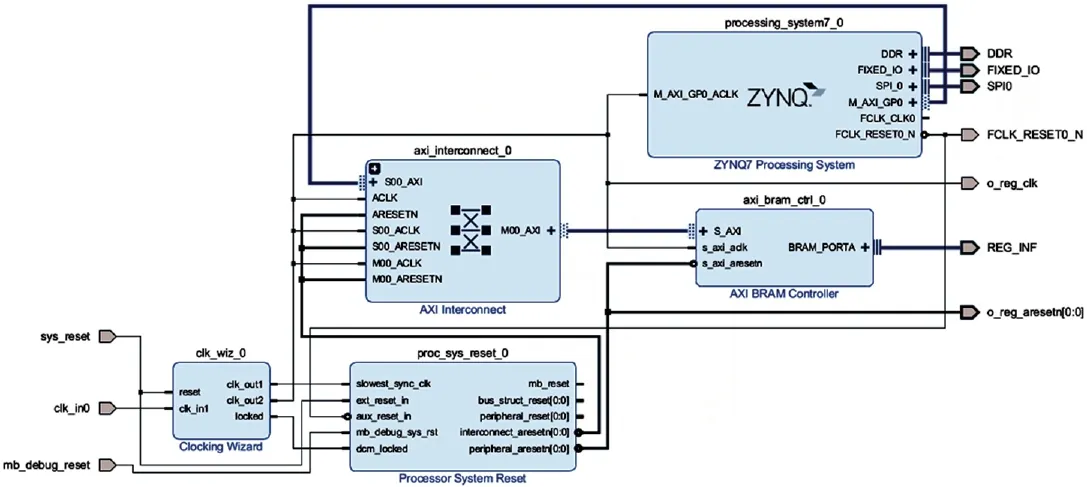

在Vivado2018.1开发环境下搭建ADRV9009的收发环回环测试工程:ADRV9009的接收端RX1采集回来的数据信号在FPGA内部的JESD204B的IPcore数字接口输出直接连到JESD204B的IPcore的数字接口输入端。因此接收采集回来的数据就直接回环到ADRV9009的发端数据接口TX1。另外,也可以通过PC端的串口工具对PS端的串口发送ADRV9009接收通道切换命令,命令切换ADRV9009到观测通道ORX1。FPGA工程内部把ADRV9009的ORX1通道采集接收回来的数据直接回环到发端数据接口TX1。整个系统FPGA工程采用Verilog语言编写,PS端在SDK环境下采用C语言编写;FPGA工程顶层设计模块如下:

图3 FPGA工程顶层模块图

FPGA工程模块包含4大模块:系统时钟、系统复位、AXI内部链接、Bram模块、PS控制端模块。

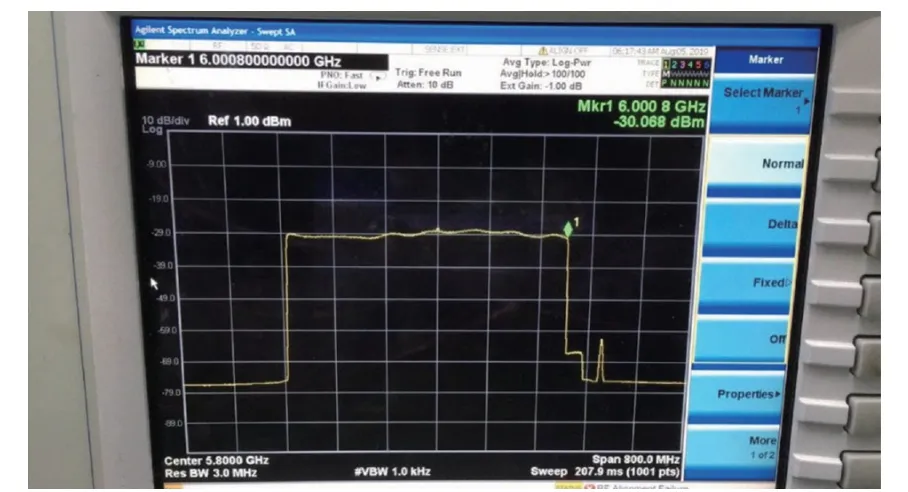

搭建测试平台仪器,信号源用Aglient N5182A,频谱仪用Aglient N9020A。设置信号源发射CW信号,幅度-20dBm,接到RX1。频谱仪接到TX1,这样就可以直接观测验证ADRV9009的接收RX1和发射TX1信号是否正常。验证结果跟FPGA工程设计一致后;通过PC端发送接收通道切换命令到板卡上,信号源连接到ORX1,继续验证ORX1通道接收带宽和平坦度。所有环路功能验证通过后,就可以把FPGA工程中的接收端口RX数据接口独立出来,再进一步做信号信号处理,并做FFT变换就可以对才采集的信号进行频谱有效监测。

为了验证ADRV9009器件的全带宽性能,收发频点范围75MHz-6GHz。进行抽样设置几个频点进行测试,对ADRV9009的本震中心频点分别配置在:230MHz、1GHz、2GHz、3GHz、4GHz、5GHz、5.8GHz;这几个抽样频点,进行全频段内的抽样带宽测试和平坦度测试。其中本震在5.8GHz信号源输入接收机的接收端,进行扫频。接收机的发送端输出测试结果见图4,可以看到该接收机可以到达器件的最大频率6GHz,带宽450MHz,整体平坦度3dbm左右。

图4 系统最大频点和最大带宽测试

4 结束语

本文介绍了基于ADRV9009的频谱监测接收机设计与实现,以及对最新高速数据接口JESD204B进行比较清晰简明扼要阐述。该方案实现的频谱监测接收机,具有电路结构简单,体积小,采集带宽大,本震频点切换时间短等优势。可做成便携式监测仪,方便户外随时随地监测频谱信号。本文对无线电频谱监测和数据采集系统设计工程实现和涉及到高速数据接口JESD204B标准设计具有良好的参考。