基于摆幅恢复传输管逻辑的高性能全加器设计

2020-09-21韩金亮张跃军张会红

韩金亮,张跃军✉,温 亮,张会红

1) 宁波大学信息科学与工程学院,宁波 315211 2) 中国人民武装警察部队海警学院电子技术系,宁波 315211

高性能的加法器对数字电路系统性能提升具有至关重要的作用[1−3]. 根据输出信号的阈值损失情况,全加器可分为非全摆幅和全摆幅两大类型.非全摆幅全加器包括:静态能量回收全加器(Static energy recovery full adder, SERF)[4]、10T[5]、8T[6]等.此类全加器通过减少电路晶体管数目的方法来提升电路速度、降低功耗,但是往往会造成电路输出不能达到全摆幅、驱动能力下降. 全摆幅全加器包括:互补CMOS全加器、传输函数全加器(Transmission function full adder, TFA)、传输门全加器(Transmission gate full adder, TGA)、互补式传输 管 逻 辑 全 加 器 (Complementary pass transistor logic full adder, CPL)[7−9]. 互补 CMOS 全加器具有完整PMOS、NMOS链的优点,门的上/下拉网络为对偶结构,具有良好的驱动能力和全摆幅输出. 但是互补CMOS全加器需要28个晶体管,晶体管数量较多导致电路面积较大、关键路径较长导致电路速度降低. TFA采用两个异或电路和2选1数据选择器的结构,由16个晶体管组成. 因此TFA减少晶体管数量和输入电容,具有速度快和功耗低的特点,但由于驱动能力弱导致TFA在大扇出或者级联时性能显著下降. TGA由20个晶体管组成,其关键路径包括4个晶体管. 由于TGA单元的输入耦合到输出,因此缺乏驱动能力,在级联时需要通过缓冲器改善驱动能力[10]. CPL采用多个NMOS管的方式实现,其中4个PMOS管形成上拉网络恢复输出电平. 由于使用大量的NMOS管,CPL具有更快的速度,但内部切换节点过多,导致电路的动态功耗过大. 近几年来,研究人员陆续提出各种采用不同器件工艺设计的全加器,例如量子元胞自动机(Quantum-dot cellular automata, QCA)全加器[11],门扩散输入逻辑(Gate diffusion input, GDI)全加器[12],超薄体绝缘体上硅(Ultra-thin-body silicon-on-insulator, UTBSOI) 全加器[13]等. 相对于发展成熟的CMOS工艺,新型的器件工艺成本昂贵且处于开发阶段. 因此,CMOS工艺仍然是全加器电路应用中的主流工艺.传统全加器在设计上采用不同的设计风格和传输逻辑来达到全摆幅输出. 这些设计各有优缺点,因此高性能全加器设计应综合考虑输出摆幅、驱动能力、延时与功耗等.

鉴此,通过对不同逻辑补偿阈值损失的异或/同或(XOR/XNOR)电路研究,分析 3T XOR/XNOR[14]电路中存在的阈值损失,本文提出一种无阈值损失的摆幅恢复7T XOR/XNOR电路. 然后,设计求和与进位电路,使用异或/同或电路产生的互补输出作为求和与进位电路的驱动信号. 最后,实现具有摆幅恢复传输管逻辑的高性能全加器.

1 XOR/XNOR 的阈值损失建模与分析

1.1 3T XOR/XNOR 电路分析

异或/同或电路是高性能全加器设计的关键[15−18],设计低硬件开销、无阈值损失的电路具有十分重要的意义. 本文以采用传输管逻辑的3T XOR/XNOR电路为例进行分析,如图1(a)所示. 此电路具有较快的速度,但输出存在阈值损失,且电路中存在直流通路. 当输入AB=00时,P1和P2同时导通,输出端负载电容CL放电,由于PMOS晶体管的栅极与漏极之间存在阈值损失VTP,负载电容CL只能下拉至∣VTP∣,输出端XOR为∣VTP∣的弱‘0’信号,如图 1(c)所示;当输入AB=01时,P3和 N2同时导通. 此时存在P3至N2的直流通路,产生较大的直流功耗;当输入AB=10时,P1和N1同时导通,此时存在P1至N1的直流通路;当输入AB=11时,N2,N3管晶体管导通,VDD对输出端负载电容CL充电,由于NMOS晶体管的栅极与漏极之间存在阈值损失VTN,负载电容CL只能上拉至VDD-VTN,输出端 XNOR 为VDD-VTN的弱‘1’信号,如图 1(b)所示.

图1 3T XOR/XNOR 电路和传输管传输状态分析. (a)异或/同或电路;(b)NMOS 高电平传输状态;(c)PMOS 低电平传输状态Fig.1 3T XOR/XNOR circuit and the transition analysis by pass transistor:(a) XOR/XNOR circuit; (b) logic “1” transition by NMOS; (c)logic “0” transition by PMOS

1.2 改进型 XOR/XNOR 电路建模与分析

针对3T XOR/XNOR电路存在直流通路的问题,采用增加串联NMOS/PMOS管的方法消除电路中的直流通路,如图 2(a)所示. 当AB=11时,N1和N2同时导通将XOR信号下拉至低电平. 当AB=00时,P3和P4同时导通将XNOR信号上拉至高电平. 电路中不存在直流通路,降低了功耗.

图2 改进型异或/同或电路与 RC 模型. (a)改进型异或/同或电路;(b)AB=11 异或电路 RC 模型;(c)AB=00 同或电路 RC 模型Fig.2 Improved XOR/XNOR circuit and RC model:(a) improved XOR/XNOR circuit; (b) RC model of XOR circuit forAB=11; (c) RC model of XNOR circuit forAB=00

在改进型异或/同或电路基础上构建其电阻-电容(Resistor-capacitance, RC)模型. 当输入AB=11和AB=00时,异或电路和同或电路的RC模型如图 2(b)和(c)所示. 当电路工作在异或模式时,两个串联NMOS管(N1和N2)共享同一个衬底,与输出节点相邻的N1管存在体效应. 因此连接至N1的输入具有更高的阈值电压和更大的寄生电容,导致不同输入端的寄生延时存在差异. 分析当输入AB=10向输入AB=11跳变的情形.R为单位NMOS晶体管的等效电阻,KPX、KNX为PMOS和NMOS管的单位宽度,Cd为晶体管的扩散电容. 根据图2(b)可以得到节点电容CXOR和CX的表达式,

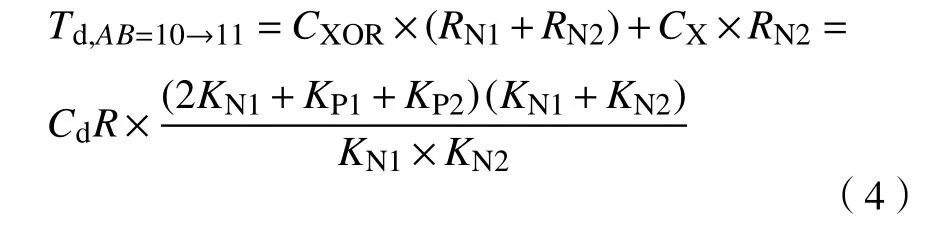

当AB从10到11跳变时,由于节点X处的电压为VDD-VTN,结合图 2(b)和 Naseri与 Timarchi[19]延时公式可得Td,AB=10→11的表达式,

当AB从01向11跳变时,由于节点X处的电压为0,不需要电荷传送到节点X. 可得Td,AB=01→11的表达式,

2 摆幅恢复 7T XOR/XNOR 电路设计

2.1 7T XOR/XNOR 电路工作原理

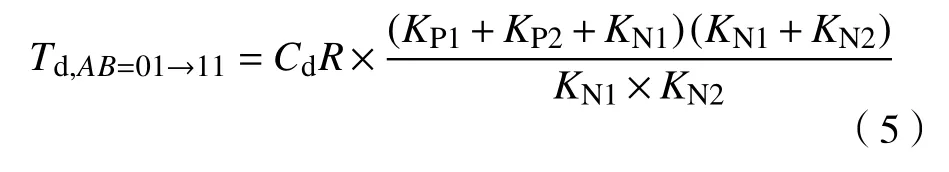

通过对上述阈值损失和电路延时的分析,在改进型异或/同或电路的基础上,利用补偿电路阈值损失的方式,提出具有摆幅恢复的7T XOR/XNOR电路,如图3所示. 为了平衡上述Elmore延时差使电路达到最优性能,在异或电路设计中,输入信号A连接到内层晶体管N2,采用栅极接的NMOS管弥补XOR信号的阈值损失,并将输入信号B连接到N3的扩散区. 同理,在同或电路中将输入信号B连接到内层晶体管P2,采用栅极接的PMOS管弥补XNOR信号的阈值损失,并将输入信号A连接到P3的扩散区. 所设计的异或/同或电路包括三个区域:传输管逻辑区域、静态CMOS区域和摆幅恢复区域. N4、N5、P4、P5构成快速传输管电路,P1和P2为上拉网络,N1和N2为下拉网络,P3和N3为阈值补偿晶体管组成摆幅恢复电路.

图3 摆幅恢复 7T XOR/XNOR 电路Fig.3 Swing recovery 7T XOR/XNOR circuit

当输入AB=00时,P1、P2串联上拉网络使得XNOR 信号强‘1’输出. P4、P5 管仅能传输电位为∣VTP∣的弱‘0’信号,N3 晶体管作强‘0’补充使得XOR信号强‘0’输出;当输入AB=01和AB=10时,由 N4、N5、P4和 P5使得 XOR,XNOR信号强‘1’和强‘0’输出;当输入AB=11时,N1、N2串联下拉网络使得 XOR 信号强‘0’输出. N4、N5管仅能传输电位为VDD-VTN的弱‘1’信号,P3 晶体管作强‘1’补充使得XNOR信号强‘1’输出,弥补N4、N5管传输高电平时的不足.

2.2 阈值补偿情况分析

通过4中的仿真环境对所设计的7T XOR/XNOR与3T XOR/XNOR电路进行仿真对比分析阈值补偿情况. 图 4为在 1.2 V 电压下 3T XOR/XNOR电路与7T XOR/XNOR电路输出电平对比图. 如上文分析,对于输入AB=00,由于PMOS管传输低电平存在阈值损失,3T XOR电路中输出信号不能达到全摆幅,输出XOR仅能达到∣VTP∣≈0.36 V 的弱‘0’信号,如图 4(a)所示. 同样,对于输入AB=11,由于NMOS管传输高电平存在阈值损失,3T XNOR电路中输出信号不能达到全摆幅,输出XNOR仅能达到VDD-VTN≈0.89 V的弱‘1’信号,如图 4(b)所示. 对于摆幅恢复 7T XOR/XNOR 电路,当输入AB=00时,N3管作为强‘0’补充使输出XOR达到全摆幅;当输入AB=11时,P3管作为强‘1’补充使输出XNOR达到全摆幅.

图4 异或/同或电路输出电平对比. (a) XOR;(b) XNORFig.4 Comparison of XOR/XNOR circuit output levels:(a) XOR; (b)XNOR

3 摆幅恢复 SRPL-26T 全加器电路设计

3.1 SRPL-26T 全加器结构框图

在全加器中,A和B为加数,CI为进位输入,Sum为和,Cout为进位输出. 通过对全加器逻辑表达式的推导,可以获得表达式(6)和(7).

⊕为异或运算符. 由表达式(6)和(7),可以将全加器分为3个部分:异或/同或电路,求和电路,进位电路. 其中异或/同或电路可以产生同步的XOR,XNOR信号,作为求和电路和进位电路的驱动信号,如图5所示.

图5 全加器结构框图Fig.5 Full adder block diagram

3.2 求和电路与进位电路设计

通过对上述异或/同或电路以及全加器结构的分析,列出求和电路与进位电路,如图6所示.图6(a)为采用传输管逻辑和传输门逻辑的4T XOR[20]求和电路,异或/同或电路产生的互补输出信号作为传输门的栅极输入. 当传输门关断时,由 P2 和 N2 分别传输强‘1’和强‘0’信号,使输出Sum达到全摆幅;当传输门导通时,由于P2传输低电平存在阈值损失,N2传输高电平存在阈值损失,传输门作为强‘1’和强‘0’补充弥补阈值损失,因此输出Sum能达到全摆幅. 该电路输出无阈值损失且晶体管数量较少,具有较低的硬件开销.图6(b)为使用传输门逻辑实现的进位电路[21],输出无阈值损失,但由于输出节点使用传输门,因此不适用于大负载电路. 通过式(5)分析,对输入信号与输出信号同时取反,在输出节点处接反相器同样可得到正确的逻辑功能. 图6(c)为改进的具有一定驱动能力的进位电路,在输出节点处使用反向器以增加驱动能力.

3.3 SRPL-26T 全加器电路及工作原理

图6 求和电路与进位电路. (a)基于传输门的 4T XOR 求和电路;(b)基于传输门的进位电路;(c)改进的传输门进位电路Fig.6 Sum circuit and carry circuit:(a) 4T XOR sum circuit based on transmission gate; (b) carry circuit based on transmission gate; (c) improved carry circuit based on transmission gate

图7 SRPL-26T 全加器电路Fig.7 SRPL-26T full adder circuit

SRPL-26T全加器电路结构如图7所示,由18个晶体管和4个反相器组成,包括异或/同或电路、求和电路、进位电路. 异或/同或电路产生同步的XOR和XNOR信号,作为求和电路与进位电路的驱动信号. 求和电路采用了由传输门与传输管逻辑组成的4T XOR电路,异或/同或电路产生的互补信号作为传输门的栅极输入信号. 进位电路采用改进的基于传输门的数据选择器,输出节点连接反相器,以提高进位输出信号Cout的驱动能力.

当输入AB=00时,XOR信号输出为0,XNOR信号输出为1. 若输入信号CI为0,P7导通将源极输入信号XOR传输至输出端. 由于PMOS管传输低电平存在阈值损失,输出Sum达不到全摆幅,与此同时P6和N6组成的传输门导通弥补阈值损失,因此输出信号Sum能达到强‘0’输出. 进位电路中P8和N8组成的传输门导通将输入信号传输至节点经由反相器达到输出端,因此输出信号 Cout能达到强‘0’输出. 若输入 CI为 1,N7 导通将源极输入信号XNOR传输至输出端. 由于NMOS管传输高电平存在阈值损失,输出Sum达不到全摆幅,与此同时P6和N6组成的传输门导通弥补阈值损失,因此输出信号Sum能达到强‘1’输出. 此时输出信号 Sum 为 1,Cout为 0. 同理,当输入AB=11时,XOR信号输出为0,XNOR信号输出为1. 若输入信号CI为0,则输出信号Sum为0,Cout为1. 若输入信号CI为1,则输出信号Sum为1,Cout为1.

当输入AB=01时,XOR信号输出为1,XNOR信号输出为0. 若输入CI为0,P7导通将源极输入信号XOR传输至输出端,输出信号Sum能达到强‘1’输出. 与此同时进位电路中P9和N9组成的传输门导通将输入信号传 输至输出节点经由反相器达到输出端,因此输出信号Cout能达到强‘0’输出. 若输入信号 CI为 1,N7 导通将输入信号XNOR传输至输出端,输出无阈值损失. 此时输出信号Sum为0,Cout为1. 同理,当输入AB=10时,若输入CI为0,此时输出信号Sum为1,Cout为0;若输入CI为1,此时输出信号Sum为0,Cout为1.SRPL-26T全加器电路具有全摆幅输出和良好的驱动能力. 采用全定制方法在TSMC 65 nm工艺下使用Cadence Virtuoso工具绘制SRPL-26T全加器电路的版图,仅采用两层金属线布局,如图8所示,版图面积为 17.78 μm2.

4 实验结果与分析

在 TSMC 65 nm工艺下,本文使用 HSPICE软件对所设计的电路进行仿真验证. 输入信号为包含所有跳变情况的随机数(其最大工作频率为1 GHz),电源电压为 1.2 V,延时为输入电压电平50%到输出电压电平50%的时间,功耗为电路的平均功耗,功耗延时积为电路的平均功耗与最大延时的乘积,输出负载为FO1-FO32[19]的反相器.在与相关文献比较时,采用相同的测试环境,且均将晶体管尺寸调节到最优尺寸,确保比较的准确性与公平性.

4.1 XOR/XNOR 电路实验结果分析

图8 SRPL-26T 全加器电路全定制版图Fig.8 SRPL-26T full adder circuit layout

图9 摆幅恢复 7T XOR/XNOR 电路仿真结果. (a)仿真波形图;(b)不同负载下 PDP 对比Fig.9 Swing recovery of 7T XOR/XNOR circuit:(a) simulation waveform; (b) PDP results under different load conditions

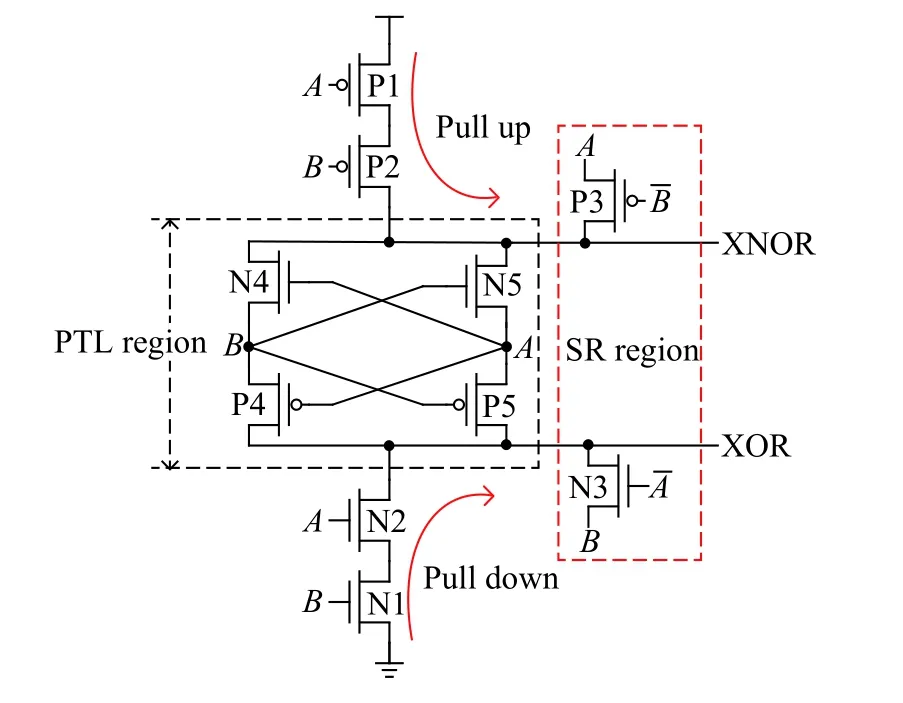

在上述实验条件下对异或/同或电路进行仿真分析,实验结果如图9所示. 图9(a)为摆幅恢复7T XOR/XNOR电路仿真波形图. 对于不同的输入和跳变组合,XOR和XNOR信号均能达到全摆幅输出. 为了更好的评估电路性能,也对比分析了不同负载下异或/同或电路的性能. 图9(b)为在不同负载下异或/同或电路功耗延时积(Power-delay product, PDP)对比. 摆幅恢复 7T XOR/XNOR 电路有对称的上拉和下拉网络,能提供良好的驱动能力,当负载在FO1-FO8变化时,能保持最小的PDP. 可以预测当负载继续加大时,电路仍能保持最小的PDP. 异或/同或电路在电压为1.2 V时的仿真结果如表1所示. 从仿真结果分析得出,文献[21]采用的反馈式异或/同或电路具有最小的平均功耗,但由于其上拉能力不足导致延时最大. 文献[20]采用的交叉耦合上拉式异或/同或电路由于其内部翻转节点过多且存在直流通路导致功耗过大. 本文提出的摆幅恢复7T XOR/XNOR电路具有最小的延时,延时可减少7.8%~50.6%,PDP可减少23.8%~43.9%.

4.2 全加器电路实验结果分析

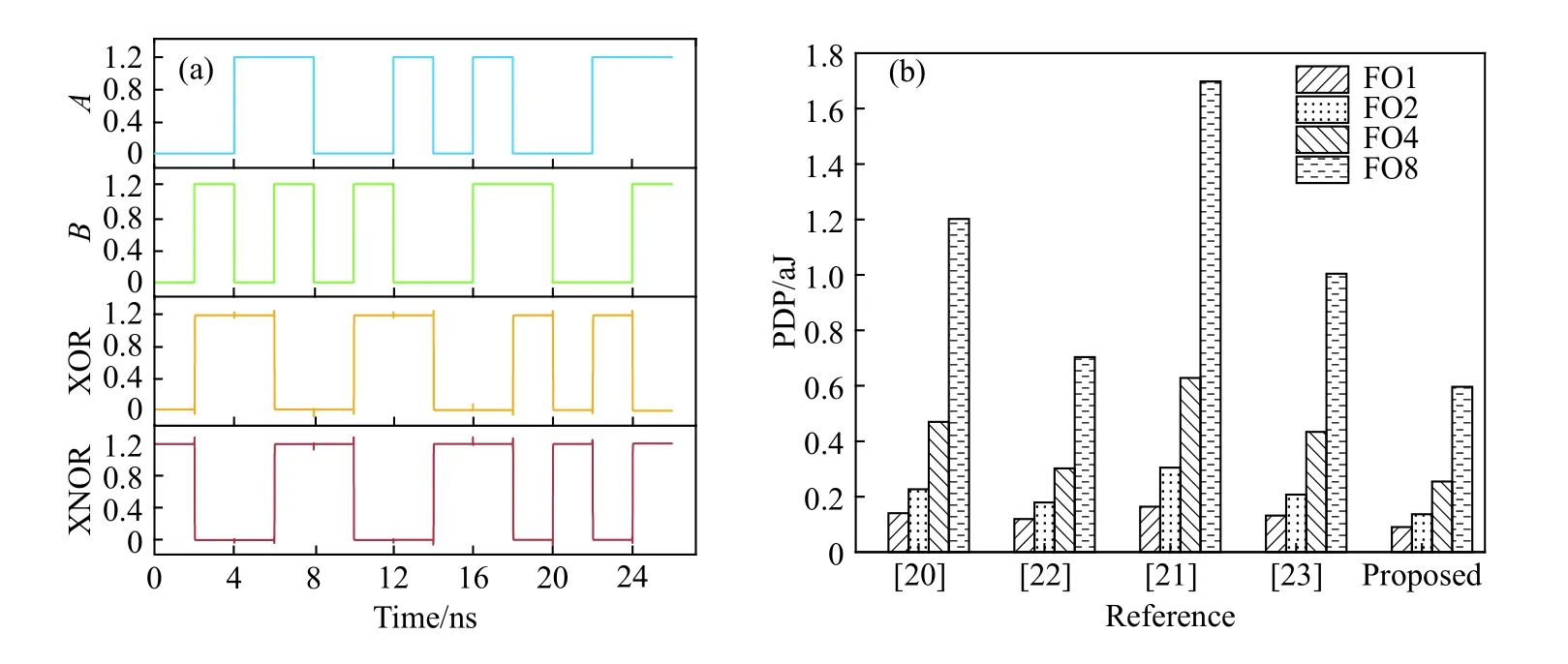

为了模拟真实的测试环境和更好的比较全加器电路性能,对全摆幅全加器在不同电压与不同负载下进行仿真分析. 分别比较了全摆幅全加器在0.7~1.4 V供电电压下的功耗、延时和PDP,如图 10(a)、10(b)、10(c)所示. 通过对仿真数据分析得到,由于CPL采用了大量的NMOS管使其在速度上有明显优势,但CPL在电压变化范围内具有最大的功耗,导致其PDP最大. 14T全加器在电压低于1 V时输出达不到供电电压的50%. 随着电压的减少,14T全加器的延时与其它全加器相比逐渐增大. 本文提出的全加器在电压变化范围内具有最小的延时和PDP. 随着电源电压降低,PDP逐渐趋于平缓,在1.1~1.2 V电压下达到最小PDP.图10(d)为在不同负载下全摆幅全加器的PDP对比. 在FO4-FO32的不同的负载下,SRPL-26T全加器与其它结构相比具有最小的PDP. 随着负载逐渐增加,本文提出的全加器的PDP保持最小的增幅.

表1 摆幅恢复 7T XOR/XNOR 电路与相关文献比较结果Table 1 7T XOR/XNOR circuit and comparison results of related literature

图10 不同电压与不同负载下全加器电路仿真结果. (a)不同电压下全加器电路功耗对比;(b)不同电压下全加器电路延时对比;(c)不同电压下全加器电路PDP对比;(d)不同负载下全加器电路PDP对比Fig.10 Simulation results of full adder circuit under different voltages and loads:(a) power results for different voltages; (b) delay results for different voltages; (c) PDP results for different voltages; (d) PDP results under different load conditions

全加器电路在1.2 V电压,负载为FO4时的仿真结果如表2所示. 与其他电路相比,SERF和10T全加器使用了较少的晶体管具有最小的功耗与面积,但输出存在阈值损失达不到全摆幅,在负载较大时延时显著增加. 在全摆幅全加器中14T全加器的面积最小,但其没有良好的驱动能力导致延时较大,在设计时需要仔细优化反馈晶体管的尺寸. TGA全加器的晶体管数量较少,但它的面积只比CMOS略小,因为TGA需要更大的晶体管尺寸以实现最小PDP. CPL使用了最多的晶体管,功耗最大,其不规则的排列导致布局的复杂性增加,面积最大. TFA与Hybrid全加器的晶体管数量相同,但后者面积更大. 因为Hybrid的延时改善是以增大晶体管尺寸为代价的,导致其面积增加. 本文提出的全加器具有最小的延时和PDP,与CPL、TFA、Hybrid等结构相比,延时分别减少10.7%、14.4%、13.7%以上. 本文提出的全加器的布局更加规整,其面积比CMOS略大,因为需要额外的金属线连接互补输入导致布局复杂性增加.与常规全加器相比,提出的全加器以较低的面积开销为代价提升性能,且具有低硬件开销特性.

表2 全加器电路与相关文献比较结果Table 2 Full adder circuit and related literature comparison results

5 结论

通过对3T XOR/XNOR电路的阈值损失机理与电路特性分析,在改进型异或/同或电路的Elmore延时分析基础上结合摆幅恢复逻辑提出摆幅恢复7T XOR/XNOR电路. 使用增加阈值补偿晶体管的方式弥补电路的阈值损失使电路输出达到全摆幅. 实验结果表明,所设计的7T XOR/XNOR电路具有全摆幅输出,且与相关文献相比具有更快的速度和更好的驱动能力. 并结合4T XOR快速求和电路与改进的传输门进位电路实现高性能全加器. 实验结果表明,在0.7~1.4 V电压变化范围内提出的全加器电路与文献相比具有最小的延时和PDP,且在不同负载下也表现出良好的性能. 由于采用摆幅恢复逻辑,电路设计中引入反向输入,增加电路面积. 提出的全加器电路以较小的面积增加提升电路性能,仍然具有低开销特性. 利用摆幅恢复逻辑实现电路低延时与全摆幅输出的设计思想,可以进一步应用到其它逻辑电路的设计中,从而推动摆幅恢复逻辑电路的实用化进程.