一种基于FPGA的多通道数据采集系统设计

2020-09-17简志

简志 景 ,梁 昊

(1.中国科学技术大学 核探测与核电子学国家重点实验室,安徽 合肥230026;2.中国科学技术大学 近代物理系,安徽 合肥 230026)

0 引言

在低温等离子体诊断领域,Langmuir单探针方法由于结构简单、测量范围大和结果可靠而被广泛应用。目前以单片机为主控芯片的传统诊断设备采样率较低,一般不超过400 kS/s[1],甚至只有 38 kS/s[2],这些设备的ADC数据接口通常采用SPI或I2C,数据传输能力有限,而且数据处理大多依赖软件设计,难以满足现在高速、高精度、长时间和大容量的测量要求[3]。准确高效地获取这些数据对等离子体特性的研究有重要意义。

为了提高诊断结果的准确性,需要采集大量的实验数据。本文提出了一套基于FPGA的四通道数据采集硬件系统,每通道采样率为65 MS/s,硬件中的ADC与FPGA之间采用高速LVDS信号进行数据传输,并且完成了基于.net框架下WPF技术的上位机可视化软件开发,实现了高速、大容量的数据采集、处理和显示。该系统可以由上位机灵活控制并长期稳定运行。

1 系统总体架构设计

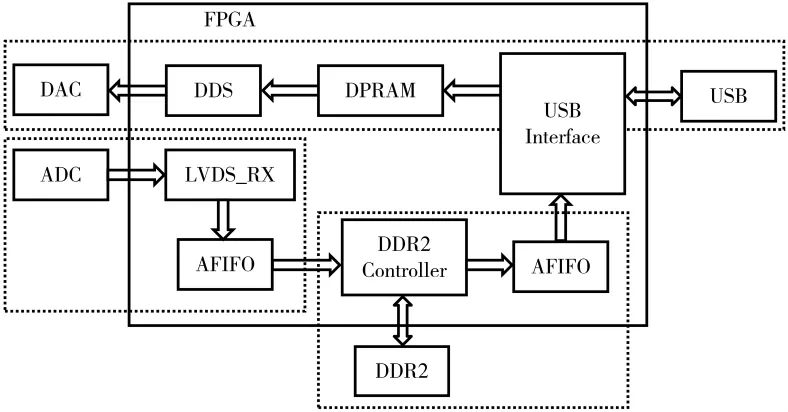

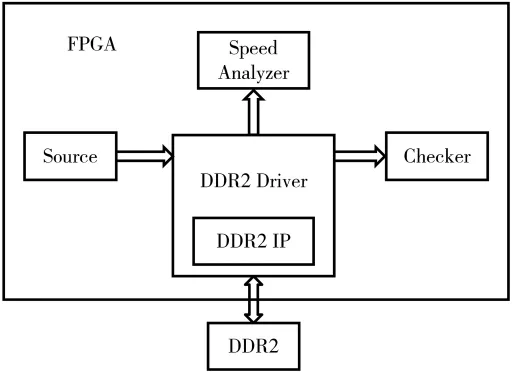

FPGA作为主控芯片控制数模转换器(DAC)输出激励波形如三角波、锯齿波和正弦波等,波形的幅度、频率和相位等均可由用户在上位机设置。DAC产生的波形信号经过电压放大和功率放大后施加在等离子体上进行扫描。通过采样电阻将微弱的电流信号转换为电压信号,放大后的电压信号被模数转换器(ADC)采集、传输给FPGA并缓存在DDR2中,当缓存达到所要求的数据量时,上位机控制FPGA将DDR2中的数据通过USB上传、保存、处理和显示。系统总体结构如图1所示。

图1 系统总体框图

2 器件选型

2.1 FPGA选型

FPGA作为系统控制的核心,为系统提供了足够强大的可重构能力,选型时需要兼顾性能与成本。本设计选用了Intel公司Cyclone III系列的EP3C25F324C6芯片[4],该芯片成本低,具有丰富的逻辑资源,包括24 624个逻辑单元,608 256 bit片上存储空间,4个锁相环,215个可用I/O,其中高速差分引脚 83对,最高数据速率 875 Mb/s,C6系列速度等级最高,可支持最高200 MHz时钟频率的DDR2,完全能够满足系统的要求。

为FPGA设计了JTAG和AS两种配置接口,JTAG可以将配置逻辑下载到FPGA并使用 SignalTap读回数据,方便调试,但由于SRAM工艺的FPGA掉电后数据不能保存,因此需要AS方式将配置逻辑烧录到非易失性的EPCS中存储。

2.2 ADC选型

为了实现对等离子体数据的高速数字化,系统采用了 ADI公司的AD9219模数转换芯片[5],AD9219是内置 4个独立通道的ADC,采样率为 65 MS/s,分辨率10 bit。AD9219的模拟输入和数字输出都是差分信号,输出为650 Mb/s的高速LVDS信号,差分输入范围为2 Vpp。

2.3 其他器件选型

DAC采用了双通道12位的AD5405,刷新频率可以达到21.3 MS/s。DAC电路设计为单极性输出,输出电压符合:

其中VREF为DAC的参考电压,D为从 0到4 095的数字码值,分辨率 n为 12。

DDR2 SDRAM存储芯片选用了Micro公司的MT47H32M16NF颗粒。DDR2在与FPGA进行连接时,应将DDR2的DQS管脚和DM管脚与FPGA中相关管脚相连,因为通过这些管脚的信号工作频率较高,对信号完整性要求也比较高。FPGA不同Bank所能支持DDR2的最大工作频率不同[6],使用底部或顶部 Bank可以支持到 200 MHz,而左右Bank仅能支持到167 MHz。本设计选择了底部Bank放置相关接口,在200 MHz工作频率下理论带宽可达6 400 Mb/s,可以满足四通道ADC共计2 600 Mb/s的数据传输要求。容量为512 Mb,用来缓存获取的大量数据。

3 FPGA逻辑

本设计采用Verilog语言在Quartus II 13.0上实现了ADC数据采集、DDR2控制和直接数字合成(DDS)等功能,在完成仿真、综合、布局布线后,生成了下载文件。FPGA总体逻辑框图如图2所示。

图2 FPGA总体逻辑框图

3.1 ADC数据采集逻辑

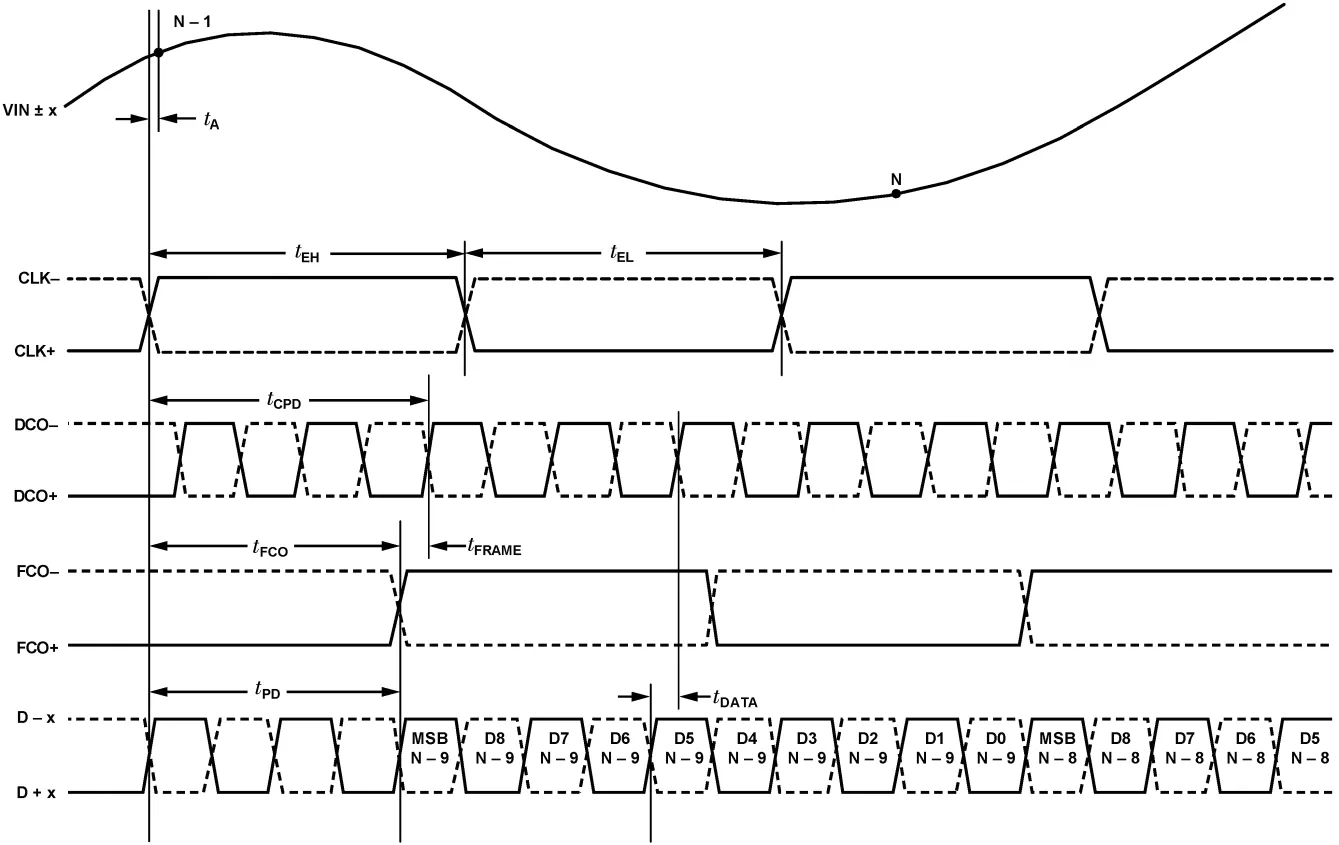

FPGA在接收ADC输出的高速LVDS串行信号时,需要考虑数据输出时钟(Data Clock Output,DCO)边沿与数据边沿所存在的相位差,这种相位差主要来自ADC自身,AD9219中约为770 ps,此外不同的电路板走线长度也会产生延时差,在硬件布局布线设计中可以对板上走线延时设置约束,本设计中时钟和数据走线延时差小于5 ps。知道了时钟与数据间的相位关系,便可以设置合理的时序约束,以满足建立时间和保持时间,消除亚稳态。Intel提供了串并转换IP核LVDS_RX,只需要确定通道数、串并比例、输入时钟频率和相位关系等参数即可调用,极大地提高了开发效率。

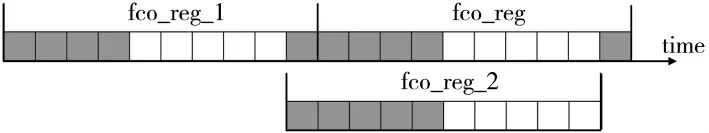

图4 FCO各寄存器比特序列调整

除了需要与数据确定相位关系,DCO也要和帧输出时钟(FCO)确定相位关系,因为仅靠 DCO采集到的数据虽然是正确的,但只是一串比特流,而不能确定数据的最高位(MSB)或最低位(LSB),只有通过FCO进行比特序列调整才可以恢复数据。比特调整的原理依据如图3所示[5],数据与 FCO的相位基本同步,FCO的上升沿与数据的MSB对应,上升沿是指FCO由0转1的比特位,此时采集的数据就是MSB。对FCO的各寄存器进行比特序列调整如图4所示,将图中寄存器fco_reg打拍得到寄存器fco_reg_1,然后拼接得到的寄存器fco_reg_2就符合要求的正确序列。对数据比特流进行同样的序列调整和拼接操作,得到的就是从MSB到LSB依次排列的数据。

数据进行比特序列调整的驱动时钟为65 MHz,而DDR2控制模块工作在100 MHz,因此需要异步FIFO进行跨时钟域处理,以防止因亚稳态产生的数据错误或数据丢失。

3.2 DDR2控制逻辑

DDR2内存读写控制逻辑包括DDR2控制器IP核和用户驱动模块。控制器IP核负责DDR2内存初始化,完成预充电、刷新和Bank激活等操作,并提供读写命令和数据接口给本地用户,以方便调用。用户驱动模块则根据读写需求向IP核下发命令和数据。IP核的工作方式有全速或半速两种,前者工作频率为 200 MHz,用户接口位宽为 32;后者100 MHz,位宽 64,所以半速工作方式是将时钟减半而数据位宽加倍。两者不会产生读写效率的差异,但半速工作方式因为工作频率低,时序要求更容易满足,故本设计采用了半速工作方式。

图3 数据流与时钟相位关系

3.3 DDS逻辑

该系统在数据获取时,需要产生扫描电压信号。模拟合成产生波形的方法只能针对特定几种波形,而且每种波形都需要特定的电路设计,不仅结构复杂而且难以实时控制。因此数字化的方法逐渐得到越来越多的应用,其中DDS是一种常用的产生波形的方法[7]。DDS主要由相位累加器、波形存储器、数模转换器和波形重建滤波器组成。工作时,上位机通过USB将波形数据下发,存储在由双端口RAM组成的波形存储器中。相位累加器会在每个时钟周期更新,其值作为地址在波形存储器中进行查询,查得样本数据通过数模转换器生成模拟波形,再经过重建滤波器得到所需波形。

4 上位机软件开发

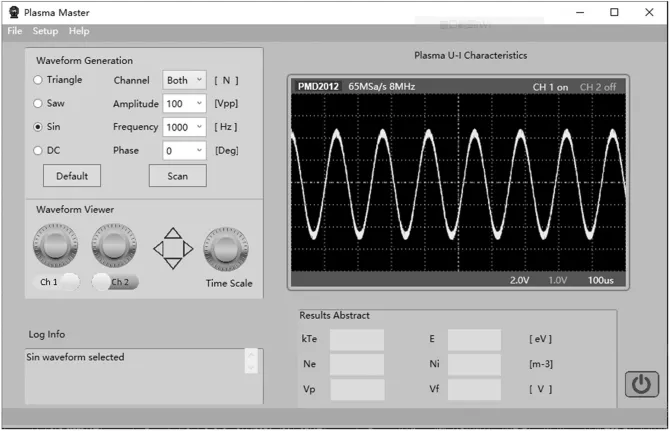

上位机的主要功能是控制波形输出、数据读回、保存和显示等。在Visual Studio平台上开发了一套基于Windows客户端程序框架(Windows Presentation Foundation,WPF)的软件平台。WPF包含大量文本、图形和布局控件,可支持2D/3D图形动态渲染,控件的功能可用C#语言实现,软件界面则由可扩展应用程序标记语言(eXtensible Application Markup Language,XAML)进行描述,上位机界面如图5所示。

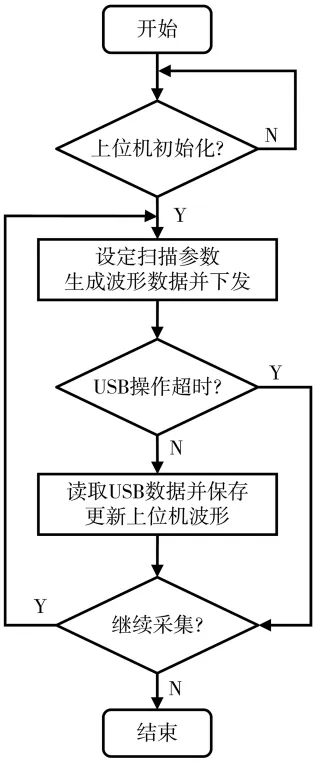

上位机工作流程如图6所示,用户首先在软件界面设置波形的类型、频率、幅度和相位等参数,据此生成波形数据并通过USB下发至FPGA;其次将ADC采集的数据读回,当读回一定量的数据之后,进行存盘;最终将最近一次读回的数据作图并显示在屏幕上。

图6 上位机工作流程图

5 系统测试

系统在完成硬件装配、逻辑调试下载之后,进行了上板测试,包括DDR2读写测试、USB通信测试、ADC性能测试和DAC输出测试。

5.1 DDR2读写测试

DDR2读写测试包括数据读写正确性测试和读写速度测试,测试原理如图7所示。

图7 DDR2读写测试原理框图

数据读写正确性测试由数据源、DDR2驱动器和检测模块构成。数据源持续写入DDR2驱动器直到写满,然后将DDR2中数据依次读出,送至检测模块确认数据正确性。在连续读写超过680 Gb数据后,即将容量512 Mb的DDR2反复读写 1 300余次,未发现错误。

图5 上位机软件界面

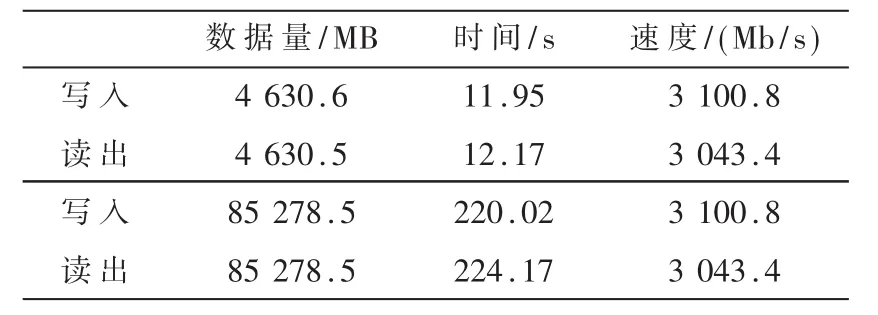

读写速度测试是在正确性测试的基础上进行计时,同时统计读写数据量和工作时间,得到长时间工作的平均速度。测试结果如表1所示。DDR2写入速度大于ADC需求速度是因为中间采用异步FIFO缓存,减少了DDR2写入的等待时间。

表1 DDR2读写速度测试结果

5.2 USB通信测试

USB通信测试[8]包括上位机下发波形数据测试和数据读回测试。上位机下发的波形数据通过SignalTap在线抓取,经过连续多次下发测试,验证了数据在经过USB芯片后可以被FPGA正确接收。数据读回测试是在FPGA中构建测试源并将数据传输到上位机,在上位机中进行数据对比检测,经过约100 Gb数据读回测试,没有发现错误。

5.3 ADC性能测试

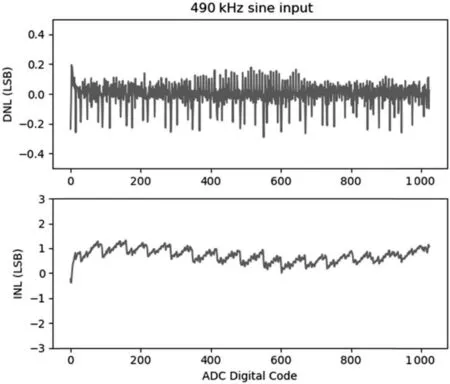

ADC的性能基本决定了整个系统的性能,其测试包括静态性能测试和动态性能测试[9]。静态性能指标包括微分非线性(DNL)和积分非线性(INL),测试信号源为490 kHz的正弦波,由泰克AFG3252C提供,连续采样点数1 228 800,非线性测试结果如图8所示,DNL范围为-0.3 LSB到 0.2 LSB,INL范围为-0.4 LSB到1.3 LSB。ADC采集的波形与频谱如图9所示。

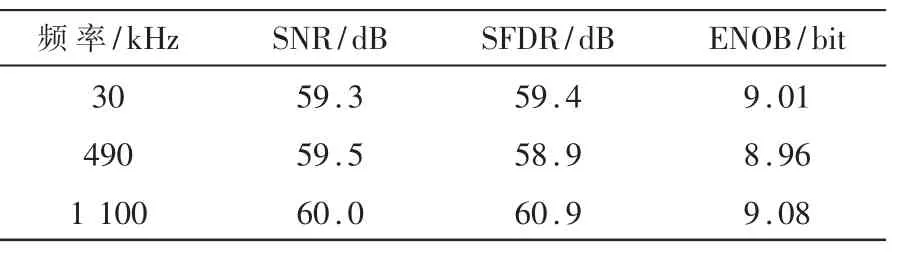

常用的动态性能指标包括信噪比(SNR)、无伪峰动态范围(SFDR)和有效位(ENOB)等,测试结果如表2所示,整体性能符合要求。

表2 ADC性能测试结果

图8 ADC微分非线性与积分非线性测试结果

图9 ADC采集的490 kHz正弦波形与频谱图

5.4 DAC输出测试

DAC输出测试由上位机依次给定要转换的数字码值,并由安捷伦34 401 A万用表测量DAC输出的直流电压和噪声(RMS)。测量直流电压与式(1)计算的理论值进行比较计算误差,参考电压为-2.037 V,最大直流误差小于 0.1%,噪声电压(RMS)6.6 mV,可以满足要求。

6 结论

本文设计了一种多通道数据采集系统,包括硬件和上位机软件。经过长时间连续板上测试,得到DDR2写入速度为3 100.8 Mb/s,读出速度为3 043.4 Mb/s,ADC的 ENOB可达 9.08,SNR为 60.0 dB,典型 DNL小于 0.3 LSB,INL小于 1.3 LSB,DAC输出直流误差小于0.1%。整个系统运行稳定,可由用户灵活控制,证明了设计方案的可行性。

表3 DAC输出测试结果