基于FPGA的功率谱分析系统

2020-09-17付恩孙秀男

付恩 琪 ,孙秀男 ,梁 昊

(1.中国科学技术大学 核探测与核电子国家重点实验室,安徽 合肥230026;2.中国科学技术大学 近代物理系,安徽 合肥 230026)

0 引言

功率谱估计是信号分析的重要方法,广泛应用于雷达信号处理、语音识别、无线通信等领域[1-3]。针对激光雷达的微弱信号探测,由于单个脉冲功率谱强度较低,通常需要将多个脉冲功率谱进行分段累加以提高探测性能[4]。经典谱估计建立在快速傅里叶变换(Fast Fourier Transform,FFT)基础之上,目前常用的基于MATLAB的功率谱估计运算耗时长、效率低,无法满足实时数据处理的需求。随着现场可编程门阵列(Field Programmable Gate Array,FPGA)集成度进一步提高,其内部资源丰富,性能强大,设计更加灵活,并具有很好的兼容性和可移植性,成为理想的解决方案。

本文设计了一种基于FPGA的功率谱分析系统,在上位机软件控制下对关键参数进行配置,实现了数据采集、硬件触发、DDR3存取、功率谱估计、结果上传等系列功能。重点研究了两种功率谱估计方案:方案一不加窗,由单精度浮点的并行FFT模块实现,计算结果精度高;方案二增加了实时加窗处理,由24 bit定点的流水线FFT模块实现,在降低频谱泄露的同时进一步提升处理速度。系统通过分段累加处理提高了对微弱信号的探测性能。

1 系统总体结构

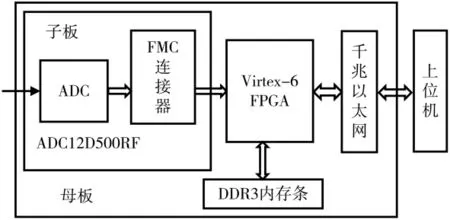

1.1 硬件总体结构

图1 系统硬件总体结构

功率谱分析系统的硬件总体结构如图1所示,包括数据采集子板和数据处理母板,两者通过FPGA夹层卡(FPGA Mezzanine Card,FMC)连接。子板负责前端模拟信号采样,以1 GS/s的 12位 ADC芯片ADC12D500RF为核心,数字信号以250 MHz、48 bit的4路并行模式输出。母板负责整体系统控制及信号处理,使用Xilinx公司的Virtex-6 FPGA芯片XC6VLX240T完成数据触发采样、DDR3存取、功率谱估计。最后,通过千兆以太网将计算结果上传至上位机。

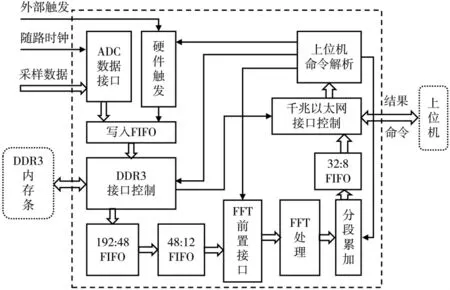

1.2 逻辑总体结构

功率谱分析系统的逻辑结构主要可分为数据接收、功率谱估计以及结果上传三部分。数据接收部分包括ADC数据接口、硬件触发和DDR3接口模块;功率谱估计部分包括FFT前置接口、FFT处理和分段累加模块;结果上传部分包括上位机命令解析、千兆以太网接口模块,总体结构如图2所示。

图2 系统逻辑总体结构

数据采集由外部硬件触发控制,触发频率为10 kHz,采集总时间为1 s。系统通过上位机配置的参数如下:(1)触发采样点数 L,范围是 20 000~67 000点;(2)触发延时 t,范围是 0~1 000 ns,每次触发后延迟 t ns再采集 L个采样点;(3)距离门点数 M,范围是 200~1 024点,以 M为节点对采样点数L进行分段,每段都需要进行FFT处理,FFT模块变换长度为固定的1 024点,其中输入FFT模块的前M点为采样数据点,后(1 024-M)点做补零操作;(4)累加次数P,范围是 1 000~10 000次,每次触发分段的FFT结果需要与之前保存的相同段结果累加,当P设置为10 000次时对应连续采集1 s。

系统的工作流程如下:(1)上位机软件完成参数的设置后,各指令通过千兆以太网接口下发至相应的功能模块;(2)对信号进行触发采样,当 FIFO中达到一定数据量就开始向DDR3中写入数据,直至写完P次触发的数据量;(3)将数据从DDR3中读出进行功率谱估计,每次触发采样信号分为floor(L/M)段,即向下取整,进行FFT计算,求模平方后保留前一半结果,最后将每次触发对应段结果累加P次存入相应的RAM中;(4)将功率谱估计结果上传至上位机。

2 系统逻辑设计

2.1 数据接收部分

ADC数据接口使用Xilinx器件原语IBUFGDS和IBUFDS[5]将随路时钟和采样信号由差分LVDS信号转换为单端信号,同时注意将接收采样信号的寄存器固定在FPGA的IO单元上,否则可能造成数据错位。原信号宽度为48 bit,利用四个寄存器缓存串并转换后信号宽度为192 bit,剩下64 bit做补零处理,与256 bit的DDR3数据存储位宽匹配。

硬件触发模块负责控制采样信号的触发写入、每次触发的采样点数以及触发延时。系统工作时,模块时钟频率为62.5 MHz,收到触发信号后,利用计数器控制触发延时t,在t/16个周期内禁止FIFO的写入。同理,对采样点数 L,在 L/16个周期内允许FIFO写入,之后禁止写入直至下一次触发。触发延时的控制精度为16 ns,触发采样点数的控制精度为16个采样点。

DDR3接口由Xilinx公司提供的IP核与用户控制模块构成[6],根据上位机指令,与读写FIFO配合,完成信号存取操作。

2.2 功率谱估计部分

针对两种功率谱估计方法,方案一采用32 bit单精度浮点的并行FFT模块,保证了谱分析的精度;另一方面,FPGA实时生成的汉宁窗系数无法达到很高的精度,为提高数据处理速度,方案二采用24 bit定点的流水线FFT模块。

2.2.1 FFT前置接口

FFT前置接口的功能是根据距离门点数M进行分段取数、补零操作以及数据格式转换。DDR3读出的采样信号经两级FIFO缓冲后送入FFT前置接口,通过控制FIFO读使能每次读出M个采样点,其余(1 024-M)点做补零处理。对于并行处理FFT模块利用Floating-point IP核将12 bit的采样信号转换为32 bit单精度浮点。

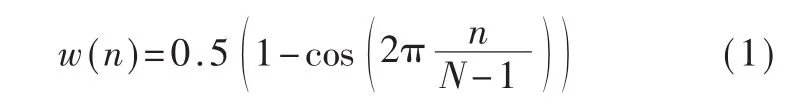

为了降低频谱泄露[7],为流水线 FFT处理模块提供了实时硬件加窗处理,已知汉宁窗时域表达式为:

其中,n=0,1,…,N-1,而距离门点数 M就对应着式中的N。当M设置完成后,上位机同时发送系数 1/(M-1),利用乘法器、CORDIC IP核及减法器实时生成18 bit汉宁窗系数,与原信号相乘后结果保留24 bit作为流水线FFT模块输入。

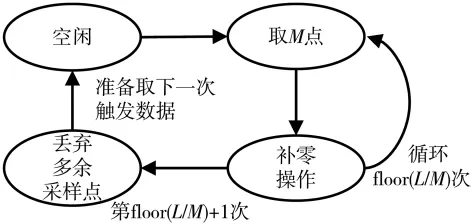

另外,对于分段后多余的采样点,需要读出并丢弃。图3展示了FFT前置接口工作状态转移图。

图3 FFT前置接口工作状态转移图

2.2.2 FFT处理模块

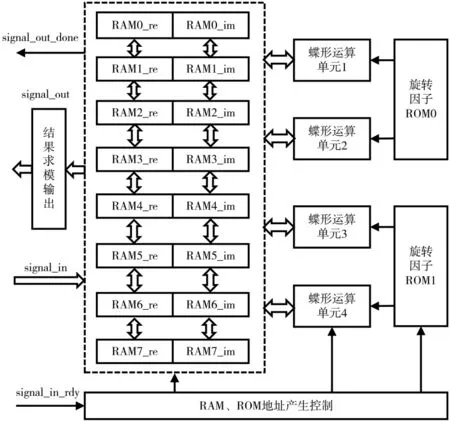

并行FFT处理模块的设计主要参考了苏斌[8]等提出的方案,采用按时间抽取(Decimation In Time,DIT)的基-2 FFT算法实现32 bit单精度浮点的快速傅里叶变换,通过四个蝶形单元并行计算提升处理速度,其结构如图4所示。模块中主要包含双端口RAM、蝶形运算单元、旋转因子ROM及地址产生控制单元等。

图4 并行FFT处理模块的总体结构

模块中存储器较多,在实现过程中为了降低地址控制复杂度,根据FFT计算规律,将RAM0、RAM2、RAM4、RAM6 分 为 一 组 ,其 读 写 地 址用一对寄存器 ram_up_wr_addr、ram_up_rd_addr控制,而 RAM1、RAM3、RAM5、RAM7 为另一组 , 读写地址用另一对寄存器ram_down_wr_addr、ram_down_rd_addr控制。同时利用多路选择器控制四个蝶形单元与RAM的连接,在FFT计算的不同阶段进行切换,最终以较少的信号实现对16个RAM的控制。

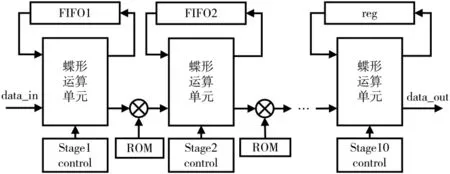

流水线FFT处理模块采用按频率抽取(Decimation In Frequency,DIF)的基-2 FFT 算法,通过单路延时反 馈(Single-path Delay Feedback,SDF)架 构[9-10]实 现24 bit定点的快速傅里叶变换,其结构如图5所示。流水线结构在FFT变换的每一级都有单独的处理模块,每个模块中都包含蝶形运算单元、延时缓存单元、旋转因子ROM及信号控制单元。

图5 流水线FFT处理模块的总体结构

蝶形运算单元由24 bit有符号的乘法器和加减法器构成,定点运算需要考虑截断和溢出。对于截断,将乘法器输出从高位开始向下截取24位作为计算结果。另一方面,为了防止加减计算发生溢出,设计在每一级的输入端将信号大小减半。

根据流水线处理的特点,延时缓存单元由FIFO实现,当需要缓存的数据少于16点时,使用移位寄存器作为延时缓存单元。信号控制单元主要负责控制FIFO的读写使能、选通信号以及旋转因子ROM的读地址。通过控制选通信号,延时缓存单元一方面可以存储输入信号,另一方面也存储蝶形运算的输出结果,分时复用的策略保证了信号的流水线处理。

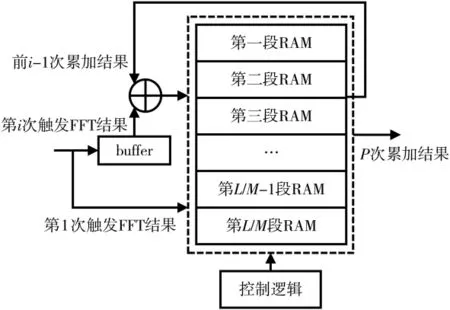

2.2.3 分段累加模块

分段累加模块主要包括双端口RAM、加法器及控制逻辑,结构如图6所示,其功能是根据累加次数P将对应段的功率谱结果累加并保存。第一次触发的分段FFT结果直接存入RAM中,之后每次触发处理后的结果到来时取出RAM中对应段数据送入加法器,并把结果存回RAM直至完成P次累加。

图6 分段累加模块结构

2.3 结果上传部分

千兆以太网接口负责控制命令收发以及结果上传,由Xilinx公司提供的 IP核产生MAC层,结合物理层芯片88E1111实现。最终需要上传的数据大小为 floor(L/M)×512×32 bit,将自定义数据帧的数据长度设置为1 024 B,收到一次上传命令则上传2帧,如此循环floor(L/M)次即可将所有数据上传。

3 系统测试

功率谱分析系统的测试内容包括并行FFT处理模块的仿真、流水线FFT处理模块的仿真、整体系统的功能验证和处理速度测试。

3.1 并行FFT处理模块的仿真

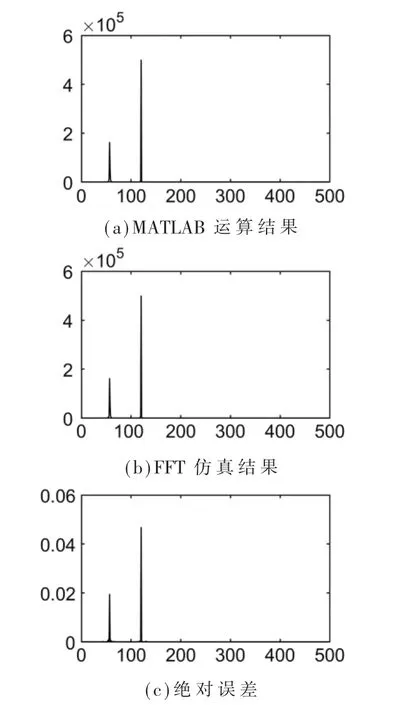

利用MATLAB生成波形数据,作为FFT模块测试信号。图7是并行FFT处理模块仿真结果与MATLAB运算结果的对比,观察发现,两者处理结果一致,频谱峰值在 105量级,绝对误差在 10-2量级,故单精度浮点处理的相对误差为10-7量级。

图7 并行FFT处理模块误差分析

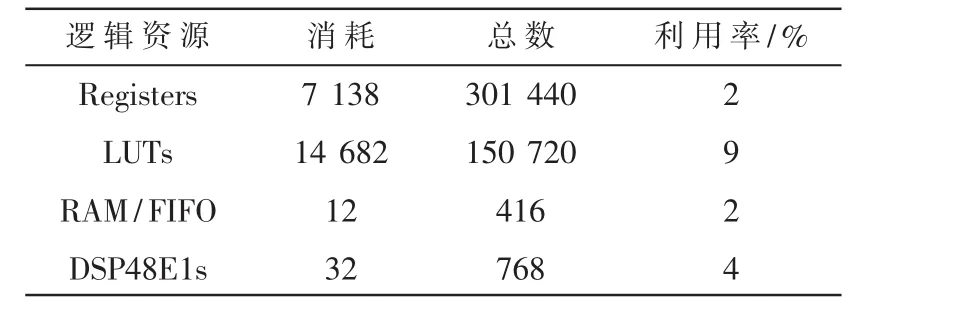

综合结果表明模块最高工作频率为250.2 MHz,系统采用200 MHz作为工作频率,完成1 024点FFT计算共耗时17.41μs,除去信号输入输出后变换时间为7.17μs。表1展示了硬件资源占用情况。

表1 并行FFT处理模块硬件资源消耗

3.2 流水线FFT处理模块仿真

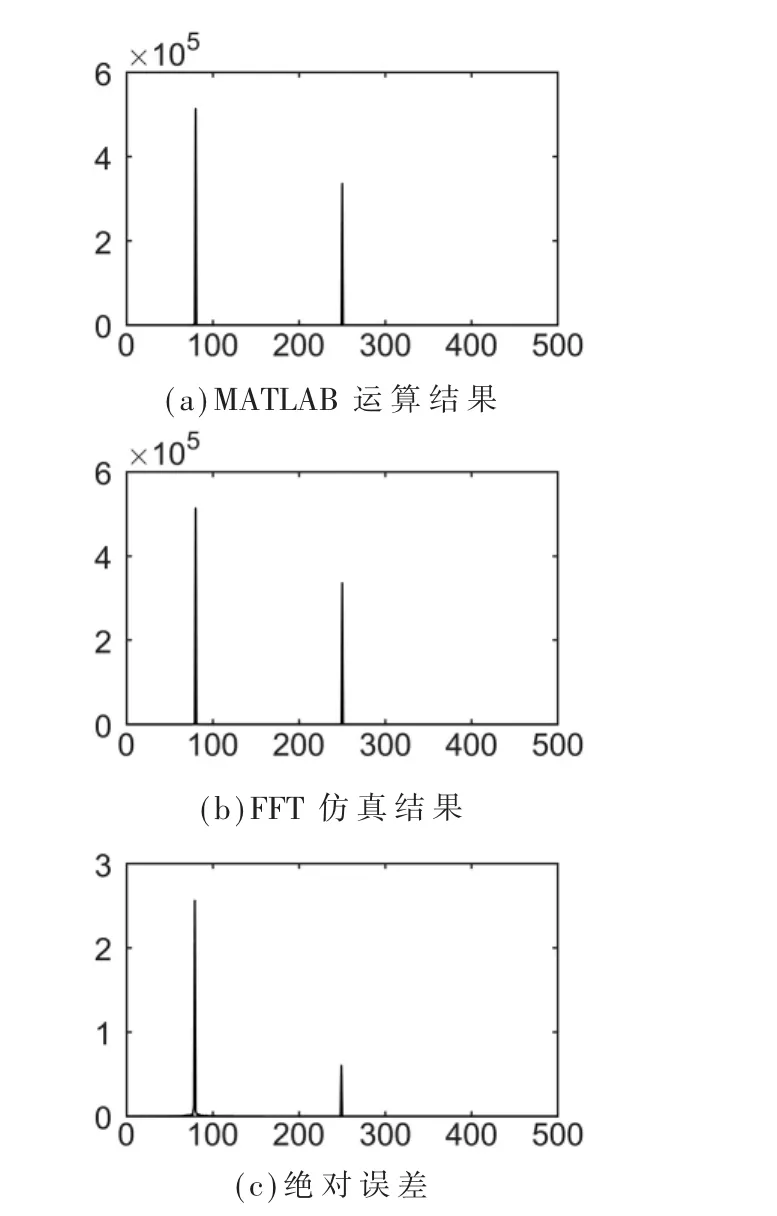

图8是流水线FFT处理模块仿真结果与MATLAB运算结果的对比,其中,频谱峰值在105量级,绝对误差在100量级,故 24 bit定点处理的相对误差为10-5量级。FFT前置接口模块生成的汉宁窗系数精度为10-5量级,将信号加窗后再进行FFT计算,此时整体的相对误差为10-4量级。

图8 流水线FFT处理模块误差分析

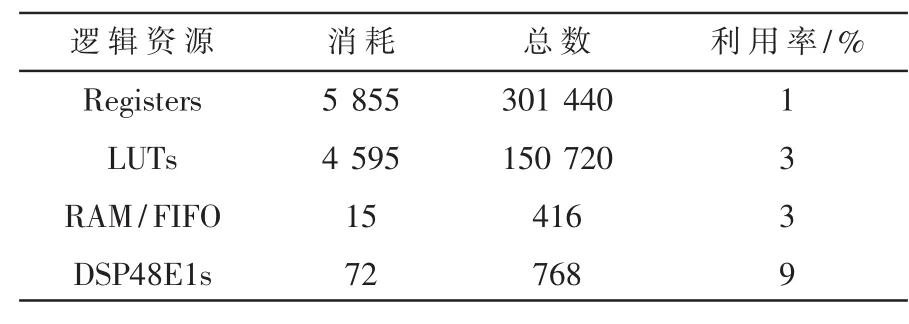

综合结果表明模块最高工作频率为394.3 MHz,在200 MHz频率下完成1 024点FFT计算耗时10.65μs。表 2展示了流水线FFT处理模块硬件资源占用情况。

表2 流水线FFT处理模块硬件资源消耗

3.3 功率谱分析系统测试

上位机指令下发后,通过ChipScope抓取各模块中收到的参数数据,对比发现各命令正确下发。利用控制变量法,分别改变输入信号频率、每次触发采样点数及累加次数等参数,进行数据采集、分段FFT处理并上传,利用MATLAB程序分析上传结果,验证了各个功能的正确性。

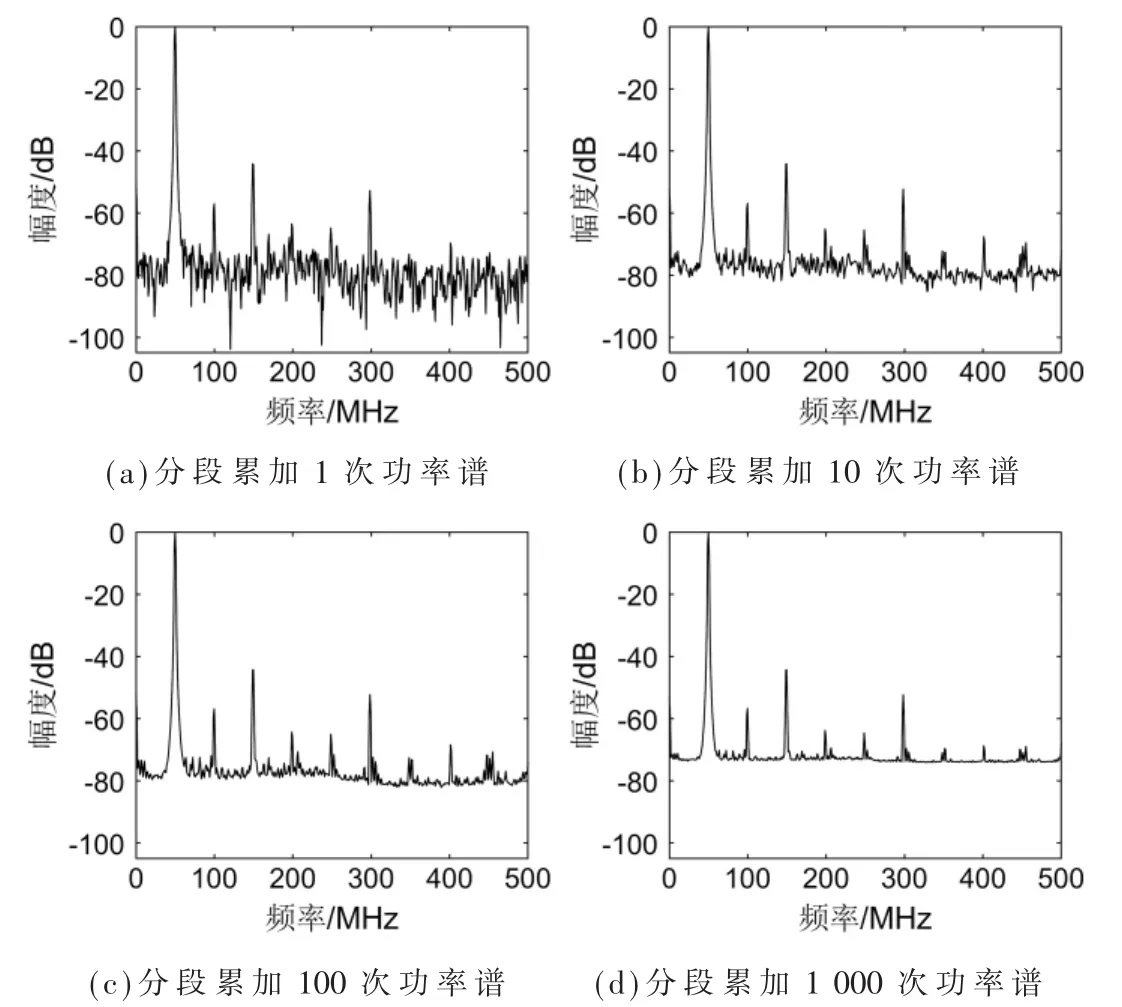

通过分段累加的方式,保留了大量信号的基本特征,同时改善了功率谱估计的性能。图9展示了系统分段累加 1、10、100、1 000次处理后功率谱的对比,可以看出,随着累加次数的增加,功率谱逐渐平滑。

图9 不同累加次数下功率谱对比

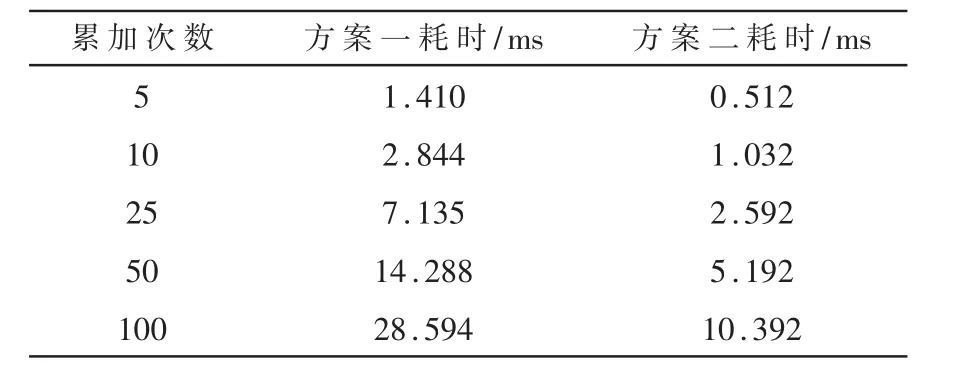

将触发采样点数L设置为20 000,距离门点数M为 1 024,即每次触发完成19次FFT运算,通过改变累加次数改变整体运算量。以信号开始输入为计时起点,结果开始输出为计时终点,分别测试两种方案进行功率谱估计消耗的时间,结果如表3所示。

表3 两种功率谱估计方案耗时

表4是本文功率谱估计方案与其他方案的比较。本文系统的优势是采样频率高,可根据需求灵活配置关键参数,频率分辨合适,并提供了实时硬件加窗处理。另一方面,由于数据量较大,本文采取先缓存后处理方式,整体消耗时间相对偏长,接下来将尝试采用多路并行FFT方案进一步提升速度。

表4 功率谱估计方案性能比较

4 结论

本文设计了一种基于FPGA的功率谱分析系统,通过硬件平台和逻辑算法的结合,灵活实现了数据采集、触发、缓存、功率谱估计、结果上传等系列功能。测试结果表明,两种FFT处理方案均达到较高的精度和速度。在上位机软件的控制下,系统能够实现实时功率谱估计,并通过分段多次累加改善功率谱估计的性能,提高了激光雷达对微弱信号的探测处理能力。