基于LVDS的并行高速AD接口逻辑设计与实现

2020-09-02饶嘉成黄明汪弈舟杨富华马栋梁

饶嘉成 黄明 汪弈舟 杨富华 马栋梁

摘 要: 随着高速AD在电子测量、宽带通信等领域的广泛应用,FPGA与高速AD的接口设计成为关键和难点,其性能影响应用功能的实现。基于FPGA驱动,实现了LVDS并行ADC配置方案以及时钟数据的时序同步;采用Xilinx XC7A200T芯片和HMCAD1520 AD芯片,实现了250 Msps×14 Bit×2通道的采集设计。逻辑仿真结果验证了设计的合理性,实际板卡测试正确。该系统接口逻辑简单,通用扩展性强,可为并行LVDS驱动高速AD数据采集设计提供有效可行的参考。

关键词: 高速AD;数据时钟同步;LVDS;FPGA;数据采集

中图分类号:TP311 文献标识码:A 文章编号:2095-8412 (2020) 04-058-05

工业技术创新 URL: http://gyjs.cbpt.cnki.net DOI: 10.14103/j.issn.2095-8412.2020.04.011

引言

随着数字化、网络化、智能化技术的发展,采集技术的准确性和高效性越来越成为信息真实性的保障。当前数据采集系统在科学研究、工业信息化系统、网络技术等领域得到了广泛应用,对AD转换高精度和实时性提出的要求也越来越高。

伴随着FPGA技术的不断发展,基于FPGA的器件在频率、速度、效率和逻辑控制能力方面开始具有其他器件无法比拟的优点[1]。为了获得更高的采样精度、速率和带宽,选择FPGA来驱动高速AD板卡成为主流,其更有利于数据前端处理及后续的高速数字信号处理。

本文首先介绍一款典型的用于模数转换芯片(ADC)初始化、功能参数配置的LVDS输出模式,实现了上电SPI接口自动配置;其次通过发送时序信号验证配置结果;最后用Chipscope抓取在线数据,验证IDDR接收数据正确性。通过FPGA内部的逻辑块和自带原语调节数据时钟相位使其符合同步及数据最优提取时序关系,输入测试信号,采集观察波形和频率,进行同步验证。

1 系统方案设计

本文实现的数据采集以Xilinx XC7A200T为主要的逻辑控制芯片,采用自顶向下的设计方法,通过FPGA对ADC HMCAD1520实现了配置控制,并实现了时钟和数据同步,完成了高速、高精度、高稳定性的数据采集。

系统硬件工作原理:以经过调理电路的模拟信号作为输入,Xilinx XC7A200T芯片完成对信号的模数转换,并将转化后的数字信号输出到FPGA,FPGA可进行后续信号处理操作。

Xilinx XC7A200T芯片拥有内部寄存器,用于功能参数配置,例如输入通道数、有效输入通道,以及输出的数据格式和位数等。本文在FPGA设计中实现了SPI接口的自动配置模块,根据数据采样需求对HMCAD1520芯片进行正确的初始化配置。

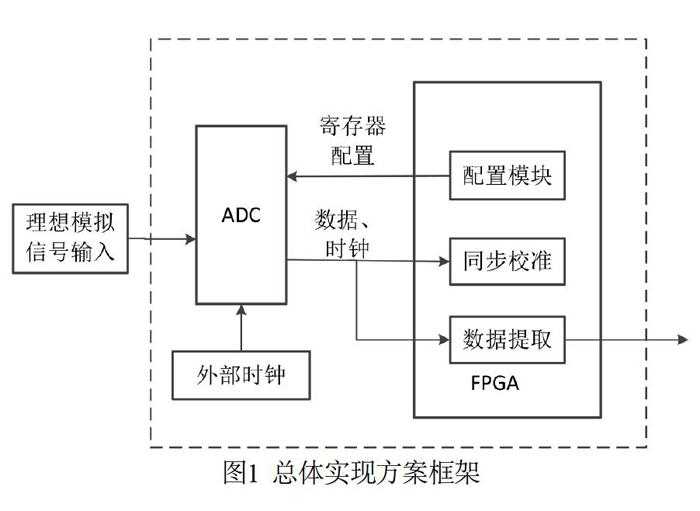

对于正常高速AD采集的有效数据,其特点是数据量大、速率高,因此在FPGA中设计高速数据接口模块,并实现数据时钟的同步校准,以避免亚稳态甚至错误数据的产生[2]。该模块使用了Xilinx内部自带DDR及信号延时调节IP原语进行设计,同步模块对位时钟和数据的建立时间和保持时间进行调整,用来保证得到准确有效的采样数据,从而实现了250 Msps×14 Bit×2通道的稳定数据传输。总体实现方案框架如图1所示。

ADC模块依据外部时钟将模拟信号转化为数字信号,配置模块可确保ADC处于正常工作状态。同步校准模块可确保数据与时钟进入FPGA时,相位关系符合提取的要求,从而经过数据提取模块显示结果。

2 ADC芯片配置详细设计与实现

为确保HMCAD1520能够正常工作,生成有效时钟和数据,ADC芯片正常工作前须先正确完成配置。本章对HMCAD1520芯片的配置详细设计与实现进行说明,包括对AD芯片的初始化、对SPI配置接口的说明以及对芯片内寄存器配置的说明。

2.1 AD芯片配置接口

系统正常工作的前提是芯片正确初始化,使得芯片处于已知的状态。本芯片特殊之处在于,作为HMCAD1520上电序列的一部分,必须应用复位和掉电周期才能确保芯片初始化正确。

芯片的具体功能由寄存器内容实现,需要对寄存器进行配置。访问HMCAD1520的寄存器接口的串行接口由SDATA(串行接口数据)、SCLK(串行接口时钟)和CSN(片选,低电平有效)引脚组成。当CSN设为低电平时,串行数据移入芯片,在SCLK的每个上升沿,锁存SDATA上存在的值,每24个上升沿载入寄存器,前8位是寄存器地址,其余16位是寄存器数据。

为了保证数据发送正确有效,具体的串行端口接口时序应满足图2关系[3]。ADC芯片的完整配置流程在各步骤间只存在一个时间上的顺序关系,各管脚和各寄存器的值之间互不相关,故可以把每个步骤看作一个状态内的操作,而时间上的顺序可以看作状态间的转移,然后采用有限状态机(FSM)来实现。

有限状态机流程如图3所示。首先对RESETN引脚施加最短20 ns的低脉冲应用复位,接着将寄存器中PD引脚拉高或利用SPI命令0x0F 0x0200实现掉电循环,然后使用SPI命令实现14位LVDS输出模式,PD引脚拉低设置活动模式,最后SPI命令选择双通道模拟输入。

2.2 AD配置实现及验证

ADC芯片的正常工作是整个驱动得以完成的前提,所以系统有必要首先验证ADC是否完成。正确的配置信号是由FPGA发送、ADC接收,最终使得ADC得到正确的响应。

FPGA配置時序在线调试状态如图4所示,主要通过判断FPGA发送的时序信号是否正确、ADC采集验证是否响应正确、从FPGA中发送出来的SPI配置信号是否正确。以上可以通过代码的行为级仿真确定,该仿真能很好地模拟发送出来的信号ADC是否响应正确,可以根据具体的配置功能是否得以实现来验证。譬如,通道数和有效位数会影响位时钟频率,所以可以测量位时钟频率来进行侧面验证。若该仿真中配置信号不符合预期,就必须要返回顶层文件重新修改代码,直至逻辑正确。

3 位时钟同步设计与实现

当AD芯片已处于正常的工作状态时,若传输中时钟线与数据线触发器的延时ts和th不恰当,可能会产生亚稳态[4]。为正确提取有效数据,须先保证数据信号有足够的建立时间和保持时间,于是本章设计位时钟同步模块,来保证这个正确的相位关系。

3.1 时钟与数据的位同步调整

由于时序单元寄存器需要考虑数据的建立时间和保持时间,所以ADC芯片通常会发送一个标准的相位关系,来保证数据的建立时间和保持时间。本文中的ADC芯片确保位时钟默认位于有效数据眼的中间,且位时钟相位偏移到数据和帧时钟信号90°最佳,如图5所示。

当信号周期固定时,如果确定了信号变化的边沿,理论上该边沿可以对齐到周期内的任意位置。对周期的遍历可以通过使用可编程延迟单元IP添加或删减延迟来实现,在每个阶段对齐周期开始时,减少抽头的数量,在每个步骤测量寄存器的输出,然后退回到起始点。当延迟时钟采样开始于时钟两种状态之间的交叉区域时,由于抖动的影响,寄存器总是输出不同的值。在这种情况下,延迟时钟已经与原时钟相位对齐,如图6所示。

Xilinx 7系列的FPGA专门提供了用于高速时钟同步和数据接收的逻辑块,在顶层文件中直接使用原语是推断这类元件逻辑特性的高效方法[5]。本次设计用到了ILOGIC块,以设计输入双倍数据速率的专用寄存器(IDDR)。使用了可编程延迟的IDELAYE2原语,且在时钟和数据信号进入FPGA时使用了IBUFGDS原语,如图7所示。

來自ADC的位时钟DCLK通过用于可变模式的IDELAYE2路由到达BUFR的输入(见上图7)。DCLK变为BitClk_MonClk(对齐的DCLK)。DCLK也作为数据输入于IDDR的D输入端。IDDR的Q1作为数据输入于CONTROL,当这个数据处于稳定状态(一直为0或一直为1)时,通过递增或递减IDELAYE2的节拍数量,从IDDR 的CLK中引入或删除延迟,直至数据处于亚稳态,此时象征着内部时钟与外部时钟对齐。由于当外部硬件稳定及FPGA逻辑布局布线完成后,电路的延迟已经固定,所以通过遍历即可确定最合适的单元[6]。

ADC是否响应正确可以根据配置具体功能、验证接收数据是否吻合得以验证。譬如,选择特定的通道数和有效位数会影响位时钟频率,所以可以测量位时钟频率佐证。

3.2 同步验证

在基于FPGA驱动高速AD芯片时,测试验证必不可少[7]。系统的每个模块只有经过了验证,设计的方案才具备可信性,这里同时给出经过验证后的数据结果。

3.2.1 同步前处亚稳态判定

主要判断位时钟是否存在且被正确锁定,通过连接外部示波器或频谱仪来确定[8]。为判断时钟是否实现了边沿捕捉,可以发送特定数据,通过查看接收端 IDDR后的数据是否稳定来确定。本文中通过Chipscope进行数据抓取,来验证IDDR数据是否已处于亚稳态。

提取到的亚稳态数据如图8所示。由于时钟与数据调用的资源和布局不同,二者在FPGA内的路径也不相同,导致二者在到达同一寄存器时,相位关系可能已发生偏斜。而且亚稳态会导致信号接收出现逻辑误判,触发器中出现中间级电平还会影响下一级传输,使故障扩延[9]。

3.2.2 同步后正确结果判定验证

通过查看采样数据是否正确来验证数据提取,如图9所示。由ADC芯片测试码的一种已知数据模式,例如通过设置ADC发送的递增序列测试码,查看最终数据是否完成递增,即可验证。

3.2.3 正常采集测试

配置ADC,采集模式为250 Msps×14 Bit×2通道工作模式,分别接入正弦波/锯齿波模拟信号进行双通道采集,测试采集波形如图10所示。

当完成上述操作后,从ADC配置到ADC发送数据,到数据经过路由进入FPGA,再到FPGA处理数据,有效性都得到了保证,只需验证真正的外部信号输入时ADC采样是否正确,而本实验通过观察采样后的波形是否失真以及频率是否准确而完成了验证。

4 结束语

本文基于LVDS的双通道250 Msps×14 bit ×2通道实现了高速AD采集逻辑设计,逻辑仿真结果正确且具有接口简单、通用性强的优点,可为并行LVDS驱动高速AD数据采集设计提供一定的参考。

基金项目

北方工业大学信息学院学生科技活动、北京市大学生科学研究与创业行动计划项目资助与支持

参考文献

[1] 刘轩.基于FPGA的多通道高速数据采集系统设计[D].北京:北京理工大学,2015.

[2] Xilinx. 7 Series FPGAs SelectIO Resources User Guide. UG471[Z]. 2015-09-18.

[3] Analog Devices. “HIGH SPEED MULTI-MODE A/D CONVERTER” HMCAD1520 Datesheet, v04. 1015[Z].

[4] 黄隶凡, 郑学仁. FPGA设计中的亚稳态研究[J]. 微电子学, 2011, 41(2): 265-268.

[5] Xilinx. 7 Series FPGAs Clocking Resources User Guide. UG472[Z]. 2015-06-12.

[6] Marc Defossez. Serial LVDS High-Speed ADC Interface. [EB/OL]. https://www.xilinx.com/. 2012.

[7] 齊红涛, 苏涛. 基于FPGA的高速AD采样设计[J]. 航空兵器, 2010(1): 35-39.

[8] 徐泽琨, 黄明, 汪弈舟, 等. 高速NRZ码同步时钟提取设计及FPGA实现[J]. 工业技术创新, 2019, 6(5): 28-33.

[9] 苏延川, 穆仕博. 多通道高速AD采样电路设计与实现[J]. 电子质量, 2018(2): 11-14.

作者简介:

饶嘉成(2000—),通信作者,男,北方工业大学2018级本科生。主要研究方向:数字信号处理。

E-mail: 2200656454@qq.com

(收稿日期:2020-07-11)

Parallel High-speed AD Interface Logic Design and Implementation Based on LVDS

RAO Jia-cheng, HUANG Ming, WANG Yi-zhou, YANG Fu-hua, MA Dong-liang

(North China University of Technology, Beijing 100144, China)

Abstract: With the wide application of high-speed AD in the fields including electronic measurement and broadband communication, the interface design of FPGA and high-speed AD has become a key and difficult point, and its performance affects the realization of application functions. Based on the FPGA driver, the LVDS parallel ADC configuration scheme and timing synchronization of clock data are realized. Xilinx XC7A200T chip and HMCAD1520 AD chip are used, so that 250 Msps×14 Bit×2 Channel acquisition design is realized. The logic simulation results verify the rationality of the design, and the actual board test is correct. Such a system has simple interface logic and strong universal scalability, which can provide effective and feasible references for the design of parallel LVDS driven high-speed AD data acquisition.

Key words: High-speed AD; Data Clock Synchronization; LVDS; FPGA; Data Acquisition