一种基于深肖特基势垒辅助栅控制的隧穿场效应晶体管

2020-08-24马恺璐靳晓诗

马恺璐,靳晓诗

(沈阳工业大学信息科学与工程学院,沈阳110870)

1 引言

集成电路基本单元的研究基于两个方面,一方面是要提高集成电路的集成度,令集成电路的基本单元尺寸需要尽可能地减小;另一方面是要提高特性[1-2]。改进的MOSFET结构也称作多级栅场效应晶体管,例如Fin FET采用小于30纳米技术节点克服了短沟道效应[3]。具有更好特性的新型结构基本单元被设计出来取代现有单元,最具有代表性的就是隧穿场效应晶体管[4-5]。在这两方面的研究有一个大的前提,即纳米级技术的现实可行性。但是,即使多级栅FET在低于10纳米量级时也不能完全克服短沟道效应[6],在这一尺度下,突变结在常规技术上难以实现,需要借助于昂贵的毫秒退火技术[7]。

为此,提出一种基于深肖特基势垒辅助栅控制的隧穿场效应晶体管。传统肖特基势垒晶体管希望势垒尽可能降低[8-9],与此不同,所设计器件利用深肖特基势垒来克服由肖特基势垒隧穿产生的电流,使源漏与硅体接触界面处的正向导通电流,即带带隧穿(BTBT)电流,实现最大化。新器件利用辅助栅电极有效抑制反向漏电流,与传统SB MOSFET或者JL FETs相比,能获得低亚阈值摆幅、更小的反向偏置GIDL电流和高开关电流比等优越性能。

2 HSB-TFET器件结构

所设计的深肖特基势垒辅助栅控制的隧穿场效应晶体管(HSB-TFET)主视图如图1(a)所示,图1(b)和图1(c)分别为图1(a)沿切线A、B的俯视图和左视图。由图1(a)和图1(b)可以看出,器件为对称结构,源漏区可以互相调换。以N型为例,在源漏与硅界面形成肖特基接触。主控栅极分别在源电极和漏电极的侧面,其形状近似于一对括号,从三个方向控制源漏区附近的硅。辅助栅极用来控制体硅的中心部分。图中,L是源漏区间体硅的长度,T是体硅的厚度,tox是栅极氧化层厚度,Wsd为源漏区宽度,Wtunnel是发生隧穿区宽度,Lag是辅助栅极长度,W是体硅的宽度。

图1新设计HSB-TFET结构图

HSB-TFET采用金属结在源漏区处形成肖特基势垒。传统SB MOSFET的导通电流是热电子发射电流,所以希望降低器件的势垒高度。而新器件采用深肖特基势垒最大程度阻挡肖特基势垒热激发电子电流,换言之,肖特基势垒被用来阻止电流在源漏间的直接流动,降低热激发电子电流,取而代之的是增加带带隧穿电流的产生,作为器件的导通机制。新HSB-TFET在器件的中心位置引入一个辅助栅极结构,设置一个特定的值,控制沟道内载流子流动。

以N型为例,新设计HSB-TFET的能带分布情况如图2所示。

图2新设计HSB-TFET能带图

如图2(a)和2(c),如果主控栅极和辅助栅极都为正向偏置,电子空穴对主要由源区的带带隧穿产生,空穴流向源极,导带电子可以容易地流向漏极,因为对于电子从源极到漏极没有形成势垒。

如图2(b)和2(d),如果主控栅极为反偏,辅助栅极仍然保持正偏,电子空穴对主要由漏区带带隧穿产生,电子流向漏极,而此时,正向偏置辅助栅极会对空穴形成一个潜在的势垒,能够有效地阻止空穴从漏极流向源极,因此,大量漏电流被阻止。

3 三种FET的特性比较

对HSB-TFET、常规TFET和SB-MOSFET的IDS-VGS特性进行比较,如图3所示。新HSB-TFET的肖特基势垒高度对于导带电子设置为0.9V。传统SB-MOSFET的肖特基势垒高度设置为0.3V。TFET的P+区掺杂浓度为1020cm-3。

图3三种FET的IDS-VGS特性曲线

即使优化SB-MOSFET和TFET的结构,反向偏置下IDS-VGS特性也非常糟糕,尤其是当VDS越大漏电流越大,相反,TFET正向电流仍然很小。新设计的HSB-TFET显示出比SB-MOSFET和TFET更高的开启电流、更陡的亚阈值特性。新HSB-TFET的反向漏电流比SB-MOSFET小很多,尤其是大偏置漏电压下。

4 势垒高度对IDS-VGS影响

图4是HSB-TFET不同肖特基势垒高度的IDSVGS特性,可将曲线分为三个工作状态:正向导通区、静态工作区、反向漏电区。势垒高度对正向导通区电流没有影响;静态工作区随着势垒高度的增加电流先减后增;反向漏电区电流随着势垒高度增加电流减小。这意味着在新设计的HSB-TFET中,势垒高度并不是越大越好,而是存在着一个理想值。

图4不同势垒高度下IDS-VGS特性曲线

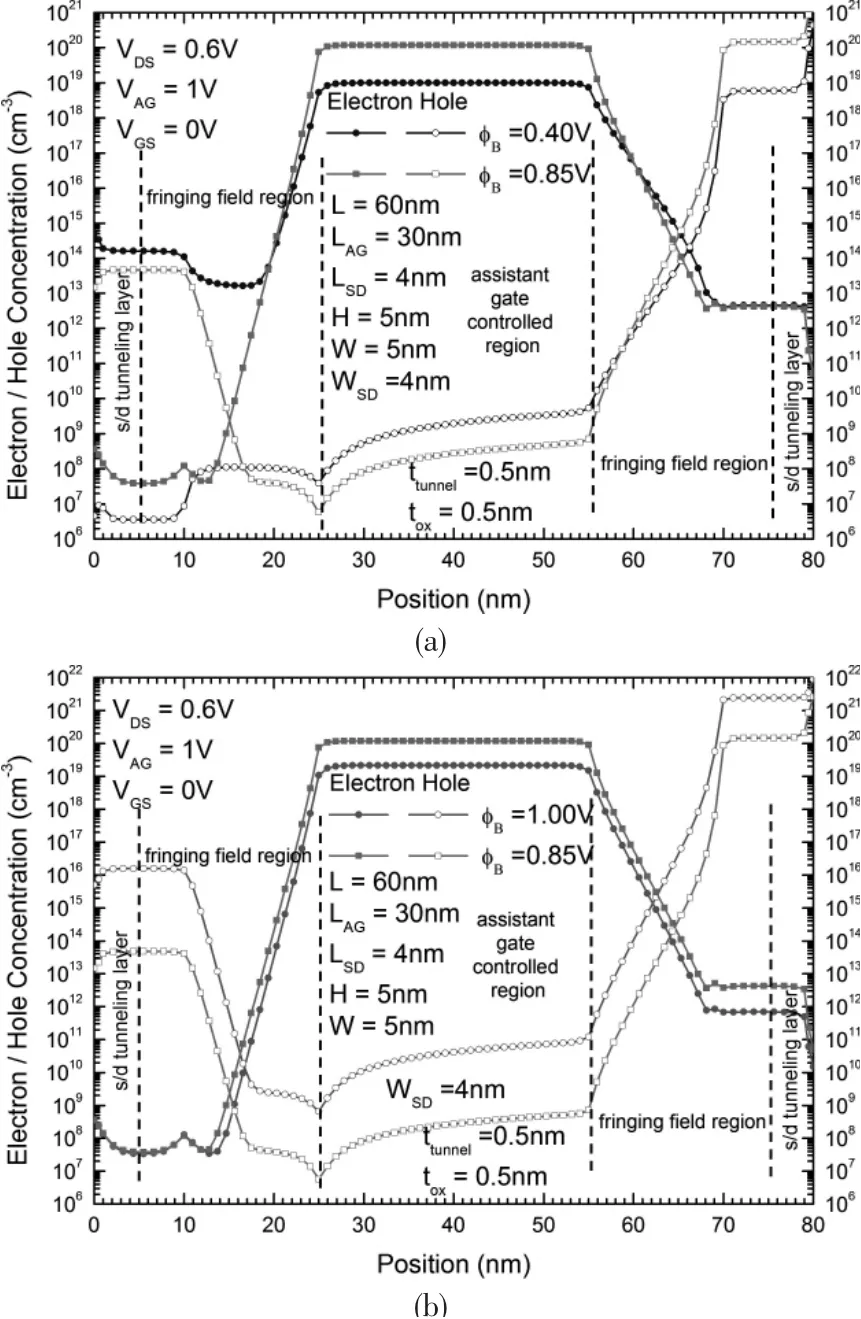

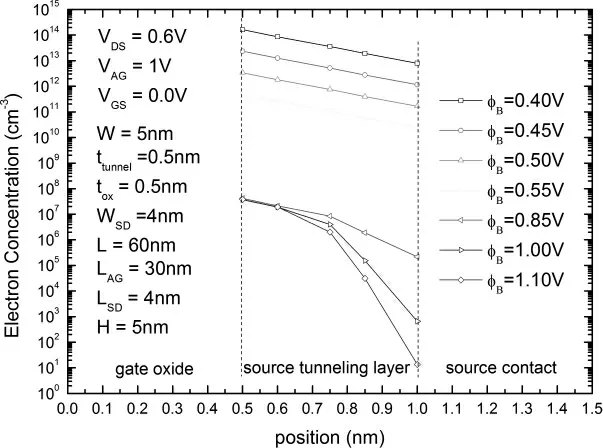

静态工作区从源极到漏极电子/空穴浓度如图5所示。源极隧穿区电子浓度如图6所示。可见源极隧穿区电子浓度随势垒高度从0.4V增至0.85V而大量减少,这是因为,此时没有外加电场作用,电流主要由热激发产生,随着势垒高度的增加,电子没有足够的能量跃迁到导带,从而电流减小。在图5(b)中,随着势垒高度继续增加,空穴浓度显著增加,这是因为势垒高度的逐渐增加使能级逐渐靠近价带;空穴不需要很大的能量就能够跃迁到价带,此时漏电流主要为空穴电流。

图5源极到漏极特性曲线

图6源极隧穿区特性曲线

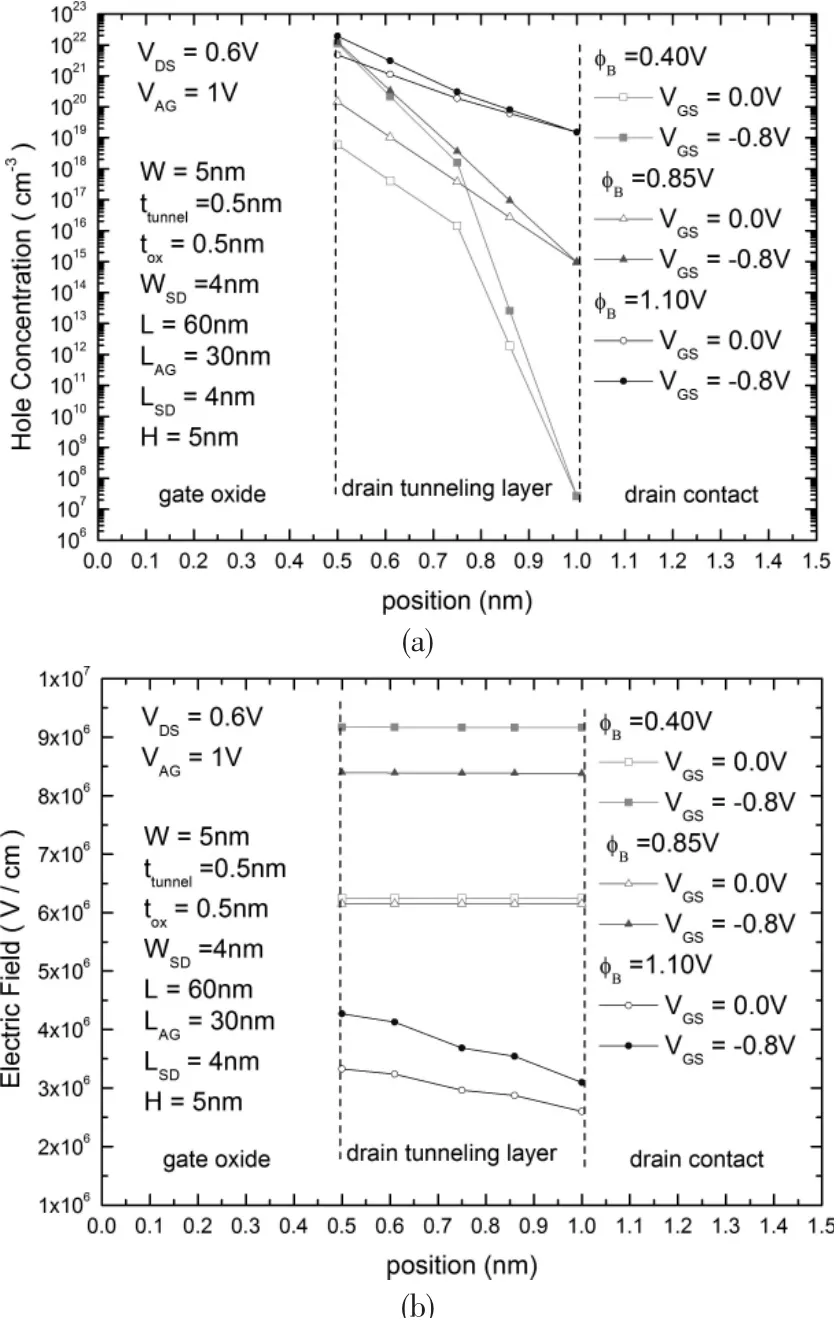

反向漏电区与静态工作区空穴浓度和电场如图7所示。反向漏电流随着势垒高度的增加逐渐减小,因为随着能级逐渐靠近价带,大量空穴跃迁到价带,在半导体体内堆积,同时空穴增加抑制了此处能带的弯曲,虽然增加漏源电压能够使能带弯曲,但是不足以抵消空穴对其抑制作用,因此反向漏电流降低。由图7(a)可见,当其他条件一定时,随着势垒高度的增加,空穴浓度增加,证明随着能级靠近价带,空穴大量跃迁到价带,抑制能带弯曲;而由图7(b)可见,当其他条件一定时,漏源电压越大,电场强度越大,能带弯曲程度越剧烈。

图7漏极隧穿区特性曲线

5 结束语

在TFET和SB MOSFET的基础上,利用深肖特基势垒辅助栅控制对隧穿场效应晶体管进行重新设计,解决了一系列基于半导体集成电路尺寸不断缩小带来的问题。降低越过肖特基势垒热激发产生的电流,增大体硅与源漏接触界面处的带带隧穿电流,利用辅助栅极来阻挡反向漏电流。新型器件可实现更低的亚阈值摆幅、更小的反偏栅致漏电流、更大的开关电流比,实现大于传统隧穿场效应晶体管的开启电流,由于结构对称,也有利于更好的集成。