基于BISS协议绝对式光栅尺数据采集系统设计

2020-08-12邝俊澎杨志军熊少旺吴建成李俊颖

邝俊澎,杨志军,孙 晗,熊少旺,吴建成,李俊颖,贾 静

(1.广东工业大学,广东省微纳加工技术与装备重点实验室,广东广州 510006;2.三英精控(天津)科技有限公司,天津 301700)

0 引言

随着时代的不断发展,在高端数控机床、精密电子封装设备和机器人等行业,对定位精度和定位速度的要求越来越高[1-3],因此对位置反馈器件的性能要求越来越高。位置编码器根据其工作方式可分为绝对式、增量式和混合式绝对编码器3 种。由于绝对式编码器由机械位置确定编码而且无需找参考点,在抗干扰性和数据的可靠性方面得到很大提高。

位置编码器作为伺服闭环控制中重要的反馈环节,与主机的通信速度和对数据处理的速度是限制执行机构快速定位的另一大因素[4-5]。本文采用绝对式直线光栅尺,其通讯协议为BISS协议。在低端应用场合中通常采用官方解码芯片或者单片机,但由于受到专用芯片的扩展能力和单片机的数据处理能力的限制,使得在高端场合和多场景应用显得力有不逮[6]。而FPGA具有灵活性高、可移植性强的特点和快速处理数据的能力,综合分析后最终采用FPGA实现BISS协议通讯。

本文介绍了BISS协议的数据结构,设计了该系统的硬件电路原理图和所需的各个软件模块,实现了通讯接口和上位机的设计并将位置数据上传至上位机显示。

1 BISS协议数据结构

BISS是来自iC-Haus公司的开源协议[7-8],它适用于传感器和执行器的数字双向串行接口,而且带CRC校验功能保护数据传送。与其他同类通讯协议相比,BISS协议在兼容性和网络结构方面更具有优势,高速性和时延与SSI相当[9]。同时,BISS协议的数据长度可以根据实际情况做出修改,具有良好的扩展性。

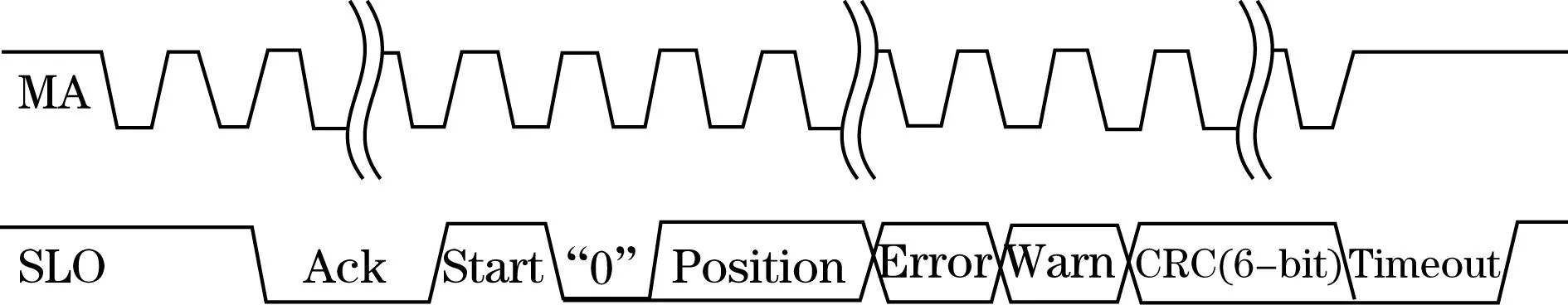

BISS协议有传感器模式(sensor mode)和寄存器模式(register mode)2种工作模式[10-11]。在传感器模式中,光栅尺充当从机,主机只需向从机发送位置请求即可快速获取相关信息。而寄存器模式中,主机和光栅尺可以进行双向读写操作来获取相应的信息。在传感器模式下,其数据帧格式如图1所示,首先是“Ack”响应阶段,紧接着是“Start”位和“0”位,之后的主体数据部分由若干位位置数据、1位错误位、1位警告位和6位CRC校验码组成,最后是超时结束阶段“Timeout”。

图1 BISS协议数据格式

具体的通信请求循环如下:

(1)空闲时,主机使MA时钟线保持高电平而光栅尺使SLO线保持高电平表示已准备就绪。

(2)请求位置采集时,主机开始传输MA时钟脉冲。

(3)光栅尺在MA时钟的第二个上升沿时将SLO线设为低电平作为响应。

(4)完成 Ack 周期后,光栅尺将二进制格式的绝对位置数据传输到与时钟同步的主机。

(5)光栅尺传送完所有数据后,主机停下时钟并将MA线设置为高电平。

(6)如果光栅尚未准备下一个位置请求周期,它会将SLO线设为低电平。

(7)当光栅尺准备进行下一请求周期时,它通过将SLO线设为高电平来提示主机。

2 系统软硬件设计

2.1 硬件电路设计

硬件系统由FPGA(Cyclone Ⅳ系列EP4CE6E22C8)和绝对式光栅尺构成,该绝对式光栅尺的通讯格式为RS485/RS422差分线驱动信号,最高通讯速率为10 Mbit/s。

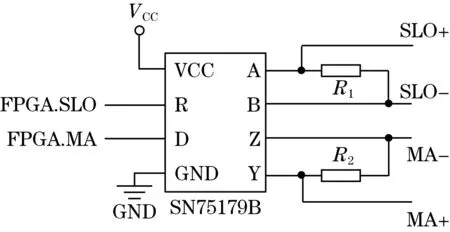

信号处理的硬件电路如图2所示,采用全双工差分芯片SN75179B对RS485信号进行处理。该芯片具有一个接收器和一个驱动器,数据传输速率达到10 Mbit/s,满足BISS协议最高数据传输要求。光栅尺通过DB9接口与主控板连接,FPGA发出的MA时钟脉冲经过转换芯片由TTL电平转为差分信号输出给光栅尺。另一方面,光栅尺返回的SLO信号经芯片处理后由差分信号转为TTL电平输入至FPGA。FPGA与上位机采用串口通信方式,FPGA将获取的位置数据依次发送至上位机中,然后上位机将位置数据描点绘图,显示工作平台的运动轨迹数据。

图2 电平转换电路

2.2 软件模块设计

该数据采集系统如图3所示,主要由锁相环、MA时钟控制器、SLO数据控制器、FIFO、UART控制器、光栅尺和上位机组成。其中锁相环的作用是为了得到不同的MA时钟频率,然后根据实际需求设置所需的MA时钟频率。光栅尺接收到MA时钟信号后返回当前位置信息给FPGA,然后经过一系列的数据处理,最后将结果传输至上位机显示。

图3 系统框图

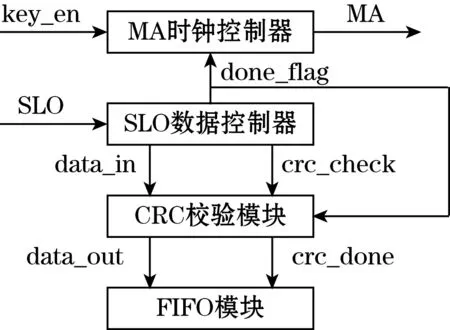

在FPGA数据处理部分中,其具体工作原理如图4所示。FPGA通过key_en信号使能MA时钟信号控制器开始工作,向光栅尺发送MA时钟信号请求获取当前位置值。光栅尺接收到位置请求后,以同样MA时钟周期返回信息数据。

图4 数据处理模块示意图

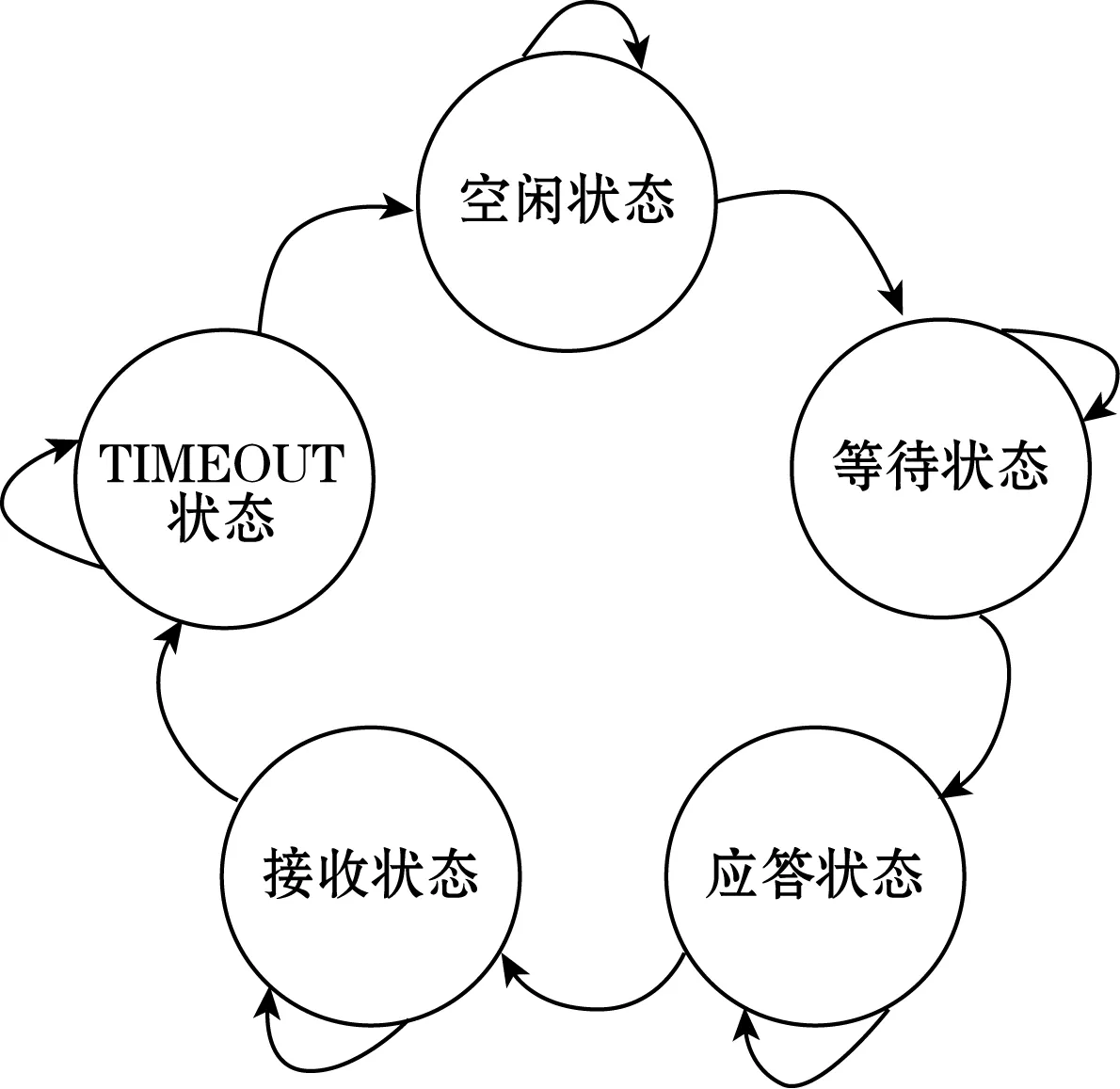

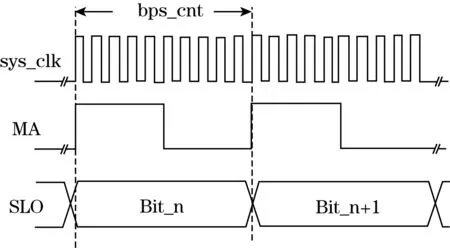

根据BISS协议的数据特点,将SLO数据控制接收数据的过程划分为5个状态,该状态机工作方式如图5所示。开始时SLO数据控制器处于空闲状态并且进入等待状态等待光栅尺返回数据。当SLO从高电平变成低电平时,状态机进入应答状态等待Start位。当接收到Start位后SLO数据控制器进入工作状态开始接收数据。一般接收数据的做法是根据MA时钟的上升沿读取当前SLO的电平状态,但是在实际电平转换过程中,电平并不稳定。因此仅仅根据MA时钟上升沿读取SLO引脚当前电平值会存在接收错误的情况。而数据在传输过程中,一般来说数据的中间位置的电平状态是最稳定的。因此在接收状态阶段中,如图6所示。其中sys_clk为系统时钟,bps_cnt为一个MA时钟周期对应系统时钟周期的数量,当计数值等于bps_cnt一半时读取数据即可获得稳定的电平值。接收完数据后,SLO控制器进入TIMEOUT状态。当SLO从低电平拉高后,SLO控制器重新进入空闲状态,如此循环工作。

图5 数据接收状态机

图6 电平信号采集原理

SLO数据控制器接收完数据后向MA时钟控制器和CRC校验模块返回done_flag信号,并且将接收到的数据分为data_in和crc_check 2部分数据传输至下一级模块中,其中data_in数据是接收到的位置值、错误位和警告位,而crc_check数据是接收到的CRC校验码。当MA时钟控制器接收到done_flag信号后停止MA时钟,并且将MA信号拉高;当CRC校验模块接收到done_flag信号后,开始对data_in数据进行CRC校验运算[12]。光栅尺的校验字段为1000011。为了进一步提升数据处理的效率,充分发挥FPGA并行数据处理的优势。CRC校验采用并行运算的算法[13-15],只需一个系统时钟周期即可计算出CRC校验码,主要代码如下:

crc_out[0]<=d[26]^d[25]^d[24]^d[20]^d[18]^d[17]^d[16]^d[15]^d[12]^d[10]^d[6]^d[5]^d[0]^c[2]^c[3]^c[4];

crc_out[1]<= d[27]^d[24]^d[21]^d[20]^d[19]^d[15]^d[13]^d[12]^d[11]^d[10]^d[7]^d[5]^d[1]^d[0]^c[2]^c[5];

crc_out[2]<= d[25]^d[22]^d[21]^d[20]^d[16]^d[14]^d[13]^d[12]^d[11]^d[8]^d[6]^d[2]^d[1]^c[0]^c[3];

crc_out[3]<= d[26]^d[23]^d[22]^d[21]^d[17]^d[15]^d[14]^d[13]^d[12]^d[9]^d[7]^d[3]^d[2]^c[0]^c[1]^c[4];

crc_out[4]<= d[27]^d[24]^d[23]^d[22]^d[18]^d[16]^d[15]^d[14]^d[13]^d[10]^d[8]^d[4]^d[3]^c[0]^c[1]^c[2]^c[5];

crc_out[5]<= d[25]^d[24]^d[23]^d[19]^d[17]^d[16]^d[15]^d[14]^d[11]^d[9]^d[5]^d[4]^c[1]^c[2]^c[3];

其中crc_out[5∶0]是CRC校验模块对数据进行计算得出的校验码,d[27∶0]为校验模块接收的data_in数据,而c[5∶0]的值全为零,最后将计算得出的校验码与接收的crc_check校验码进行比对。如果二者一致,则crc_done信号输出高电平脉冲,表示正确接收数据,并将该数据传输至下一级处理单元;否则舍弃该数据,并准备发起下一次光栅位置请求。

由于光栅尺获取位置数据的速度远快于串口与上位机之间的通讯速度,因此会造成因数据传输速率不一致而导致数据丢失的情况。针对这种情况,在数据传输过程中设计了数据缓存块。该数据采集系统的数据传输具有传输速率不一致、传输数据位宽不一致和数据传输的顺序不变的特点。综合比对各种缓存结构的特点,最后采用FIFO存储器作为数据缓存。FIFO一般用于不同时钟域之间的数据传输,也常用来实现不同位宽接口的数据匹配。数据在传送过程中需要满足寄存器对建立与保持时间的要求,数据存在亚稳态情况实现缓存功能,从而解决传输速率不一致的问题。

3 上位机设计

上位机开发利用的是基于图形界面开发的MATLAB GUI工具箱,能够快速开发实验平台原型。该工具箱集成了大量的常用模块并且提供MATLAB函数库接口,支持RS232/RS485串口通讯协议[16-17]。同时,MATIAB具有强大的绘图功能和数据分析功能,非常适用于信号采集与信号分析。而且该工具箱能够使程序转换成exe文件,使其脱离MATLAB环境也能正常工作。

由于串口通信一次只能发送8位数据,而光栅尺位置数据共26位。为了提高计算机寻址效率,FPGA将位置数据拆分为4组8位数据发送至上位机。上位机将接收到的4组数据进行拼接,然后进行十进制换算,最后根据转换后的数据画出图表。

4 仿真测试

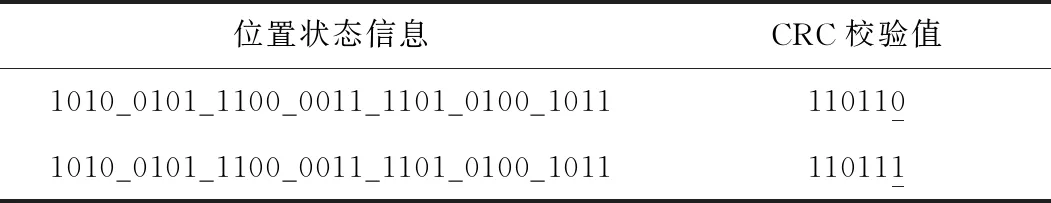

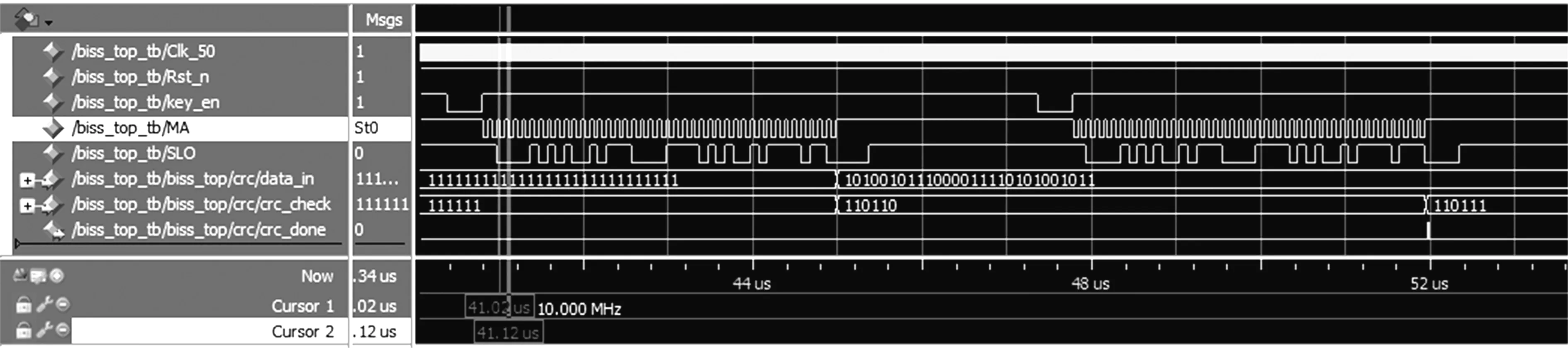

最后将整体设计好的各模块通过ModelSim软件进行仿真验证,在测试文件中模拟光栅尺以10 Mbit/s的通讯速率向FPGA传输数据。本次测试中设置了2组数据,如表1所示,其中第二组数据完全正确。由数据表可知,2组的位置状态信息一致,但CRC校验值最后一位不同。由此可以测试SLO数据控制器接收2组数据的位置状态信息是否一致和CRC校验模块能否正确工作,其整体测试结果如图7所示。

表1 仿真数据表

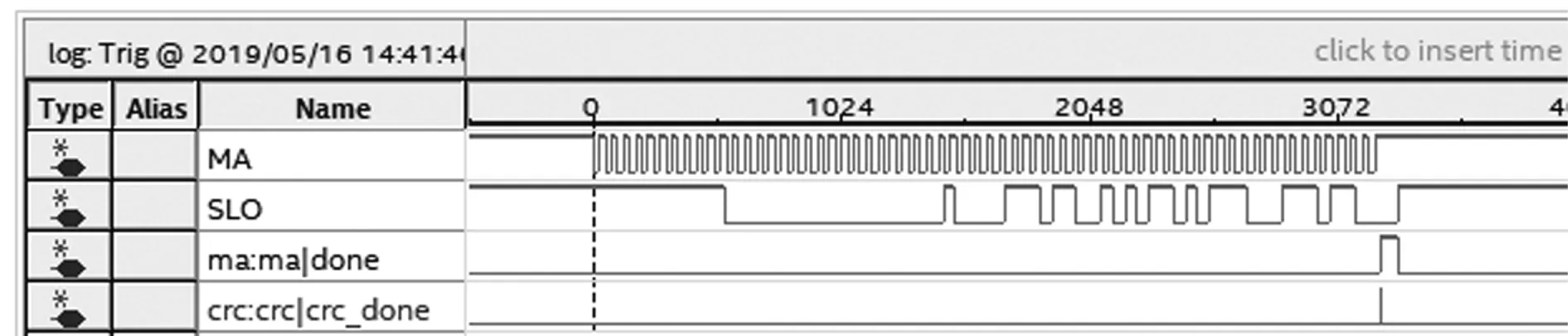

由图7可以看出,当触发信号key_en使能后,MA时钟以10 MHz的频率向光栅尺发出位置请求。测试文件模拟光栅尺发送数据,当接收完数据后MA时钟停止工作并且保持高电平等待下次触发。从波形图数据分析得,SLO数据控制器正确接收2组的位置状态信息和CRC校验值。但因为第一组的CRC校验值与事实不符,所以crc_done无高电平脉冲返回。而第二组数据crc_done返回高电平脉冲证明CRC校验成功。由此得出设计的BISS接口通过高速通信仿真测试。

图7 ModelSim仿真图

5 实验结果与分析

将编写好的程序下载到FPGA中,连接绝对式光栅尺。移动平台到不同的位置,然后发出位置请求信号,通过Signal Tap Logic Analyzer捕获FPGA内部接收的信号如图8所示。由图8可知,当FPGA发出位置请求后,MA时钟信号开始工作;当接收到完成标志位后,MA时钟停止工作并且保持高电平;之后将接收到的数据进行CRC校验,crc_done信号产生高电平脉冲信号,证明接收的数据正确。由此可见,该波形图符合BISS协议理论时序图,其数据处理模块能够正常稳定工作。

图8 Signal Tap数据捕获

通过等间距地驱动平台并且向光栅尺发送位置请求信号,FPGA将接收到的光栅尺位置信息经过校验后上传至上位机显示,如图9所示。从图9可以看出,上位机能够正确接收光栅尺的位置数据并将其描绘成图表。

图9 上位机数据显示示意图

6 结束语

本文根据BISS通讯协议设计了硬件电路和解码模块以实现绝对式光栅尺数据采集并且设计了上位机显示光栅尺数据。以FPGA为核心的数据采集系统,节省了外围电路的空间,而且移植性和扩展性好,具有一定的通用性。为了充分发挥FPGA强大的数据处理能力和灵活性,加入了并行CRC校验运算,缩短了工作周期。实验结果表明,该数据采集系统能够以10 Mbit/s的通信速率准确接收光栅尺数据,并且解码后将其传输给上位机反映平台运动信息。