一种宇航FPGA芯片的上电复位电路潜通路干扰分析

2020-08-12李森缪依展杨鹿滕树鹏张凯华

李森 缪依展 杨鹿 滕树鹏 张凯华

(1上海航天电子技术研究所/八院智能计算技术重点实验室,上海,201109;2上海航天技术研究院,上海,201109)

潜通路是指因系统或设备中存在异常电路通路,当受到特定的激励后产生的响应,其直接后果是触发电路中非预期存在的功能,抑制了正常需要的功能[1]。航天器的功能性能升级日新月异,随之而来的是器上电子电路系统的速度、规模、容量、复杂程度等指标呈指数级增长,电子电路系统的功能增多也带来了系统间接口日渐复杂。由此,对多个分系统交互处产生的潜通路干扰的分析,其重要性日益突显。

笔者结合宇航电子系统测试中的现象,论述一种基于宇航FPGA芯片上电复位电路的潜通路干扰分析,为宇航应用中大规模高速芯片上电复位电路中的潜通路干扰分析提供一种思路。

1 航天器电路潜通路干扰

航天器电子系统的复杂程度日益增高,电路的供电及回线设计难度日渐增大,供电系统中,易出现电压倒灌、电流浪涌及地线噪声等干扰。

1.1 电压倒灌干扰

航天器系统在整器设计时,通常被分解为多个分系统,再由分系统进行下一级的细分,一般分到可单独实现某种功能的单机或设备为止。在多电子设备供电共同连接的情况下,各电子设备根据功能,在上电过程中存在时间差,导致电子设备在上电前,电路中存在电压倒灌的干扰,倒灌电压通常使用隔离电路进行隔离。

1.2 电流浪涌干扰

电子设备为了提高电源品质以及EMC特性,在电源输入端加入大量的电容滤波电路,因此在加电启动瞬间要吸取大量的电流[2]。电流的瞬态不平衡,可能导致电子设备供电线路处于振荡状态,以至于无法正常启动,通常航天器电子设备需要设计专门的浪涌隔离电路。

1.3 地线噪声干扰

在航天器地面测试过程中,为对整器功能进行测试监控,会引入地面测试设备进行辅助。地面测试设备通常采用市电供电,并将其回线接入航天器电路回线中。各种不同的地面测试设备与市电的隔离情况参差不一,且市电受更大的回路影响,由此会产生地线噪声干扰。为考察航天器电子设备对地线噪声干扰的免疫性能,需通过EMC试验对电子设备进行考核。

2 上电复位电路模型

上电复位电路广泛应用于数字电路系统中,尤其以需要在上电时完成寄存器初始化、程序加载、数据读取等功能的芯片为多。而在航天应用中,为保证系统的稳定性与可靠性,上电复位电路的正确使用是强制标准要求。

航天电子系统中,为满足数据处理、逻辑控制、接口转换等功能实现,涉及使用到一种宇航级大规模FPGA,该芯片为反熔丝设计,规模为200万门。该芯片在上电时必须通过上电复位电路提供复位电平,以保证芯片的实际复位时间大于要求复位时间,原理如图1所示。

图1 宇航FPGA上电复位电路原理示意图

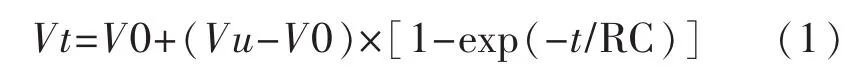

根据图1,设计适应该芯片的上电复位电路,如图2所示。该芯片上电复位信号工作电压为3.0V~3.3V。上电延时t可根据公式 (1)计算。

式中,Vt为任意时刻t电容上的电压值,V0为电容上的初始电压值,Vu为电容充满电后的电压值。经过一个时间常数的时间,电容上的电压可达到充电电源电压的0.63倍,即Vt=0.63Vu。经计算,图2中上电复位电路的上电延时理论值为675ms,可达最低要求工作电压。

图2 宇航FPGA上电复位电路原理图

3 上电复位电路潜通路干扰分析

若在上电复位电路中存在潜通路干扰,尤其是干扰对电路中的RC电路进行提前充电,可能会导致上电复位延时不足,FPGA芯片复位提前结束,影响FPGA功能正常运行。在某典型的航天器整器测试中,对其中一个电子设备的供电及回线进行测量,测量到两种潜通路干扰电压/噪声。

3.1 一次供电倒灌及母线噪声电压

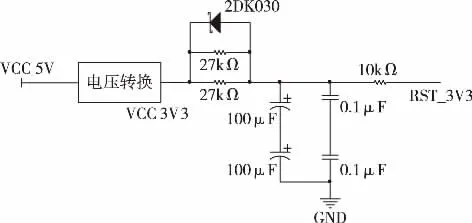

大规模FPGA的供电,由电压转换芯片将5V的二次电压转为3.3V电压来满足要求。图3所示的是电压转换芯片 (MSK5230)的内部电路图,管脚1为电压输入,管脚2为电压输出,管脚3为二次地。

图3 电压转换芯片 (MSK5230)内部电路图

当电压转换芯片在正常工作时,三极管Q1工作在不饱和区,通过比较器D1与反馈电阻R1,R2调整输出电压;三极管Q3及温度传感器为过温保护电路;二极稳压管D2及三极管Q4组成过流保护电路。当管脚1无输入时,管脚2有倒灌电压存在情况下,三极管Q1存在寄生反向二极管,此寄生反向二极管的测试压降约为0.3V,因此此时可在管脚1上存在倒灌电压。

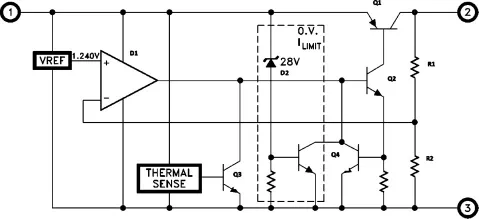

航天器整器测试时,地线上存在有脉冲宽度6μs,频率为20kHz,幅值约为400mV的地噪声叠加,噪声波形如图4所示。

图4 航天器整器供电地线噪声示意图

在该状态下测试时,5V电源的倒灌电压为0.29V,该电压与0.4V的地线噪声叠加后可达到0.69V,此时电压转换芯片开始已经有输出,实测该输出电压约为0.35V。

3.2 地线噪声

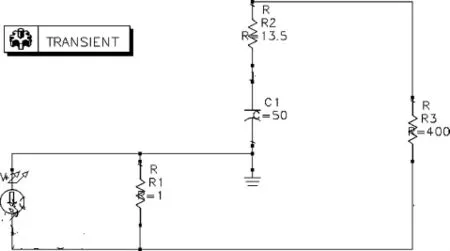

该设备电压转换芯片的3.3V输出电压端与二次地之间的实测负载阻抗是400Ω,对该部分电路进行抽象简化,使用ADS搭建的等效电路模型如图5所示。

图5 上电复位电路等效电路图

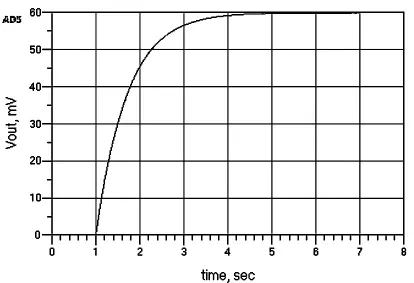

脉冲宽度为 6μs, 周期为 50μs, 幅值为400mV的噪声,对该噪声进行运行仿真,仿真出RC电路中的电容充电电压约60mV,如图6所示。

图6 第二类噪声仿真结果图

RC上电电路中的电容上干扰电压为0.35V。代入公式 (1)中,计算可得上电复位延时变为571.926ms,降低了15.3%。

4 优化措施

4.1 电源芯片倒灌优化

针对电源芯片电压倒灌,常规的做法是在电源输出端串联低压降二极管。当输出电压为3.3V时,二极管正向导通,当有反向电压时,二极管反向截止,即可阻挡电压倒灌。缺点为正向电压有约为0.3V~0.5V压降。本设备3.3V为CMOS逻辑芯片的IO电压,供电电压要求为(3.3±0.3)V,增加防倒灌二极管后实测电路可以正常工作。

4.2 地线噪声优化

针对地线上存在的噪声,常规的优化方法是电容旁路。理想电容的阻抗为Z=1/jωc,随着信号频率升高,阻抗变小。而实际电容因为有寄生电感的作用,阻抗先变小再增大,即存在一个阻抗最低的谐振点,所以应根据想要滤除的噪声频率来挑选合适的电容,串联在信号和地之间,即可起到 “噪声旁路”的作用。本次地噪声的频率为 20kHz。因此挑选 10μF的瓷片电容,20kHz时阻抗很小约为0.8Ω,能较好的起到噪声信号旁路的作用。

本文使用潜通路干扰分析的方法,介绍了航天器电子系统中的主要干扰形式,对宇航大规模FPGA芯片的上电复位电路进行分析,在测试中测量到电压倒灌干扰和地线噪声干扰,根据仿真分析的结果表明,在该案例的条件下,潜通路干扰将大规模FPGA的有效上电复位延时缩短了15.3%。这对FPGA上电复位电路以及FPGA代码的设计具有启示意义,通过软硬件的裕度设计,满足降额指标,实现宇航大规模FPGA应用过程中的可靠性与安全性。