一种基于Serial Rapid IO标准协议的高速交换技术*

2020-08-12朱新忠王冠雄韦杰鲍迪李毅

朱新忠 王冠雄 韦杰 鲍迪 李毅

(上海航天电子技术研究所/八院智能计算技术重点实验室,上海,201109)

随着航天载荷技术的发展,载荷产生的数据量以及数据速率呈爆发性增加。以某光学相机9Gbps的数据速率为例,当前卫星平台较弱的在轨处理能力和数传能力 (900Mbps)无法完成新型载荷数据的实时传输、存储或实时处理任务。此外,传统空间信息系统往往采用直连的拓扑结构,具有定制性强、通用性差、互联不灵活的缺点。而网络化拓扑具有扩展性强、通用性高、组网灵活、可实现多种冗余架构的优势,是当前空间信息系统和高性能计算系统的研究热点。

为提升空间信息系统的数据传输能力,优化空间信息系统单机内、单机间的互联拓扑架构,基于Serial RapidIO(SRIO)标准协议的高速交换技术,我们分析了SRIO协议及CPS 1848交换芯片特点,结合SpaceVPX架构,研究了一种交换阵列,以此为基础构建了SRIO交换模块,并进行基于SRIO协议的高速交换的技术验证。

1 SRIO协议

SRIO协议是一种标准通信协议,以高速Serdes(高速串并转换收发器)为物理层接口,可实现流量控制、交换及光电传输,具备构建网络化空间信息系统的潜力。SRIO协议具有传输协议简单、支持多种网络拓扑、软件依赖性小的优点,适合在恶劣空间环境下实现嵌入式系统的高速互联。SRIO协议支持5种基础网络拓扑结构:双星互联拓扑、单星互联拓扑、单星扩展拓扑、全互联拓扑和部分互联拓扑。

SRIO协议只通过物理层、传输层即可完成数据的交换转发。交换节点依靠包的路由来实现其交换功能。在SRIO互联系统内,每个可寻址器件至少具有一个唯一的DeviceID,当通信节点产生数据包时,会将destID和sourceID放在包头。SRIO交换部件内部设有路由表将不同的DeviceID映射到物理端口,SRIO交换部件通过解析收到的包头取得当前包的destID和sourceID并输入路由表查找到相应的物理端口,完成查找后导通相应端口实现包的路由操作从而完成交换。

2 基于CPS 1848的交换组网技术

2.1 交换阵列

目前高速SRIO交换芯片的种类较少,较为常用的是IDT公司的CPS 1848。该芯片采用48路双向RapidIO端口组成Switch结构 (交换结构)。芯片设计符合RapidIO 2.1标准,支持多种位宽模式、全端口无阻塞交换以及热插拔。该芯片允许从外部对拓扑结构进行动态配置,可以实时进行网络重构。

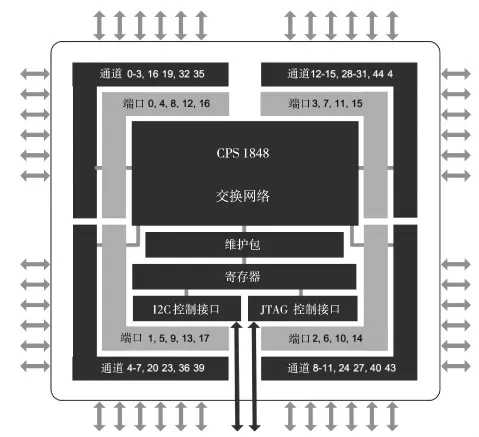

CPS 1848微架构如图1所示[1],该芯片具有48路Serdes接口,单通道最大线速可达6.25Gbps,单片峰值交换吞吐量可达240Gbps。

图1 CPS 1848微架构

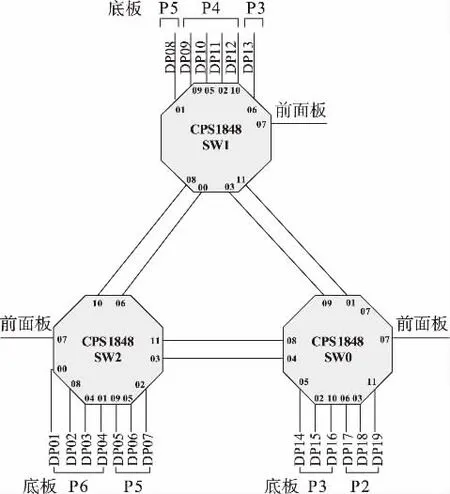

根据性能需求,采用3颗CPS 1848组网即可构成交换阵列,如图2所示。交换阵列用于执行不同端口之间的导通/关断,并提供交换缓冲,性能参数如下。

a)端口数量:如果使用标准VPX接插件的所有差分节点,最多可以为底板 (见图2中P2~P6)提供 19路 4×通道的交换接口 (见图 2中DP01~DP19);同时能够向交换前面板提供3路4×通道的对外交换接口。

b)交换吞吐量:峰值可达440Gbps,底板接口吞吐量可达380Gbps,对外接口吞吐量可达60Gbps。

c)负载分析:86%的交换资源都用于底板交换,在仅保证系统底板数据交换时,交换阵列内各芯片几乎满载。

图2 交换阵列结构

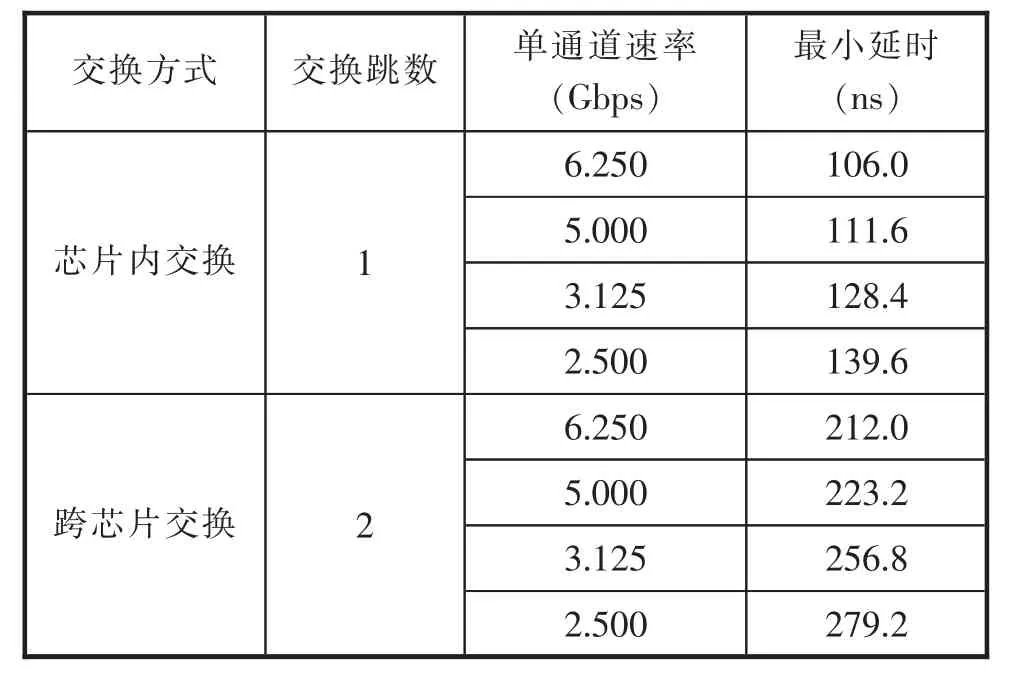

在4×模式下,根据CPS 1848的端口透传时间,计算SRIO交换网络延时信息,结果见表1。可以看出,CPS 1848交换阵列增加了端对端交换的传输延时,但是在保证交换端口数大于20的情况下,各端口间的交换跳数和延时趋于平稳和一致,从而使得系统高速数据的传输时序更为稳定。

表1 SRIO交换网络延时表

2.2 交换模块

以交换阵列为基础构建交换模块,交换模块用于实现系统内模块之间、系统与外部通信节点之间的高速数据交换,具体包括交换端口、FPGA、DSP和交换阵列等部分。

3 基于IBIS-AMI模型的信号完整性分析

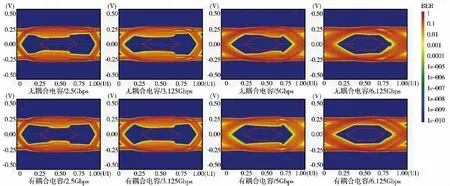

使用IDT公司提供的SRIO交换芯片Serdes接口的IBIS-AMI模型[2],对通信接口及链路进行信号完整性分析。在空间电子系统应用场景下,交换模块与系统内其他模块通过底板连接,底板作为高速串行通信的信道介质,SRIO接口、底板的信号完整性分析对于交换模块、系统底板的设计与研制具有重要意义。从底板的PCB中提取最长信道和的传输线模型,最长路径19.807cm,线宽 140μm,特性阻抗 59Ω,延时1.447ns,收端均串接0.1μF的耦合电容。

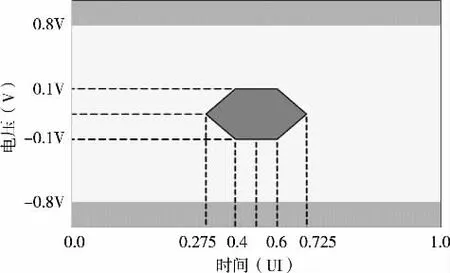

眼图波罩如图3所示,在最长路径下,绘制了不同速率时Serdes的收端信号眼图,如图4所示。测试比特数为100万,采用8b/10b编码。可见在最长路径、最短路径下,信道收端的眼图在不同速率下均可将眼图波罩放入眼图内部,其中当收端串接0.1μF的交流耦合电容时高速传输(高于5Gbps时)的信号完整性更好,但对长路径下的低速传输有轻微影响。综上所述,交换模块信号完整性设计合理。

图3 RPIO 2.0收端眼图波罩(代入CPS 1848参数)

图4 最长路径下的Serdes眼图

4 交换技术验证及测试分析

4.1 测试系统

在单星拓扑下,进行测试以验证SRIO交换模块的交换速率和信号完整性。测试系统由直流电源、测试设备、测试计算机、网线及各类测试电缆组成。

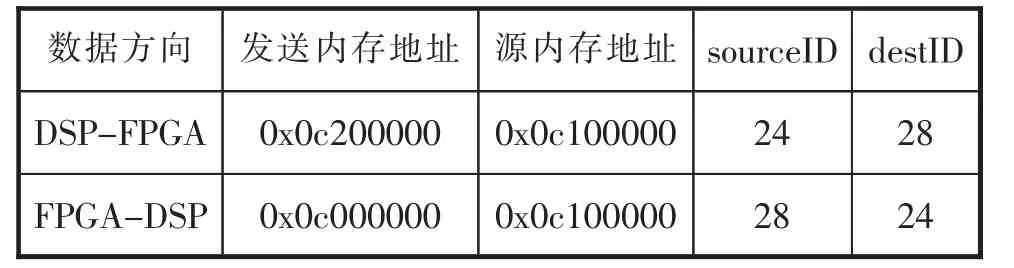

测试信息流见及数据信息见表2,高速数字信号处理模块使用板内DSP的集成SRIO接口经交换模块向与板内Kintex-7 FPGA互发数据[3],从而对SRIO交换模块进行技术验证。并使用Xilinx的IBERT IP核使用FPGA绘制SRIO接口在单路速率为5Gbps时的信号眼图。

表2 SRIO数据包信息

4.2 测试结果分析

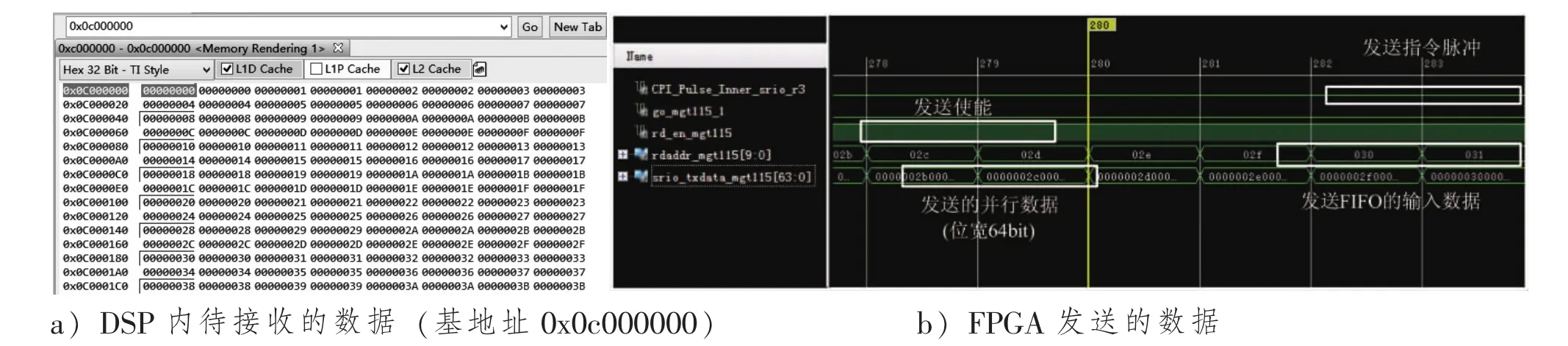

如图5 a)所示为DSP内基地址为0x0c100000的一段初始化为顺序数的内存,DSP将此段数据以DMA方式[4]由SRIO接口发出,经过交换模块后,通过ILA逻辑分析仪在FPGA内部可以观测到接收到的顺序数,详情如图5 b)所示。

同时,FPGA也使用SRIO接口通过交换模块向DSP传输数据 (如图6所示),DSP的SRIO接口模块接收到数据包后,根据解析包头将数据以DMA方式写入起始地址为0x0c000000的内存内。

图5 SRIO数据互传 (DSP向FPGA)

图6 SRIO数据互传 (FPGA向DSP)

使用Xilinx的IBERT IP核测试Serdes接口的内回环通信误码率,测得误码率为10-8。在DSP上测得实际有效速率为12.368Gbps。根据有效速率与链路速率的关系计算链路速率可达到20Gbps。

本文研究了基于SRIO协议的高速串行总线交换技术,开展了信号完整性分析,基于CPS 1848芯片进行了SRIO交换技术验证,在测试过程中使用了高性能FPGA及多核DSP SOC的SRIO接口对本文所述的交换技术进行验证,链路速率达到20Gbps,理论吞吐率达到440Gbps,测试结果表明本文所述基于SRIO协议的高速串行总线交换技术具备较强的数据传输能力和组网能力,在高速网络化信息系统领域具备广阔的应用前景。